国際特許分類[H01L29/06]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体本体 (3,016) | 半導体本体の形状に特徴のあるもの;半導体領域の形状,相対的な大きさまたは配列に特徴のあるもの (1,731)

国際特許分類[H01L29/06]の下位に属する分類

整流,増幅,またはスイッチされる電流を流す電極が接続されている半導体領域をもつものであって,その電極が3つ以上の電極を持つ半導体装置の部分であるもの (1)

整流,増幅,またはスイッチされる電流を流さない電極が接続されている半導体領域をもつものであって,その電極が3つ以上の電極を持つ半導体装置の部分であるもの

国際特許分類[H01L29/06]に分類される特許

41 - 50 / 1,730

半導体装置及びその製造方法

【課題】半導体層と電極との間に絶縁膜を介するMIS構造を採用するも、オン抵抗の上昇及び閾値の変動を抑止し、信頼性の高い半導体装置を得る。

【解決手段】AlGaN/GaN・HEMTは、化合物半導体積層構造2と、化合物半導体積層構造2の表面と接触する挿入金属層4と、挿入金属層4上に形成されたゲート絶縁膜7と、挿入金属層4の上方でゲート絶縁膜7を介して形成されたゲート電極8とを含み構成される。

(もっと読む)

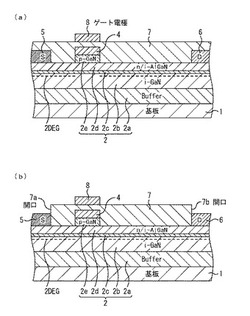

化合物半導体装置及びその製造方法

【課題】第1の極性を有する第1の化合物半導体層と共にこれと逆極性(第2の極性)の第2の化合物半導体層を用い、化合物半導体層の再成長をすることなく、第2の極性に対応した導電型の含有量が実効的に、容易且つ確実に所期に制御された、複雑な動作を可能とする信頼性の高い高耐圧の化合物半導体装置を得る。

【解決手段】第1の極性を有する電子走行層2bと、電子走行層2bの上方に形成された第2の極性を有するp型キャップ層2eと、p型キャップ層2e上に形成された第1の極性を有するn型キャップ層2fとを有しており、n型キャップ層2fは、厚みの異なる部位2fa,2fbを有する。

(もっと読む)

電子装置およびその製造方法

【課題】開口部を形成されることにより、大きなバンドギャップを有するグラフェンシートを有する電子装置を提供する。

【解決手段】基板と、前記基板上に形成されたグラフェンシート23と、前記グラフェンシートの一端に形成されたソース電極23Sと、前記グラフェンシートの他端に形成されたドレイン電極23Dと、前記グラフェンシート上ゲート絶縁膜を介して形成され、前記グラフェンシートにゲート電圧を印加するゲート電極と、前記グラフェンシートに前記ソース電極とドレイン電極を結ぶ方向を横切って形成された複数の開口部23Aよりなる開口部列と、を備え、前記複数の開口部はいずれも、三つのジグザグ端により画成されて正三角形の形状を有し、前記ジグザグ端のうち二つは、前記ソース電極とドレイン電極を結んだ方向に対し30°の角度をなし、もう一つのジグザグ端は90°の角度をなし、それぞれの正三角形の向きを揃えて形成されている。

(もっと読む)

電力用半導体装置

【課題】終端領域の耐圧が高く、終端領域の面積が小さい半導体装置を提供する。

【解決手段】本発明の実施形態の半導体装置は、第1導電形の第1の半導体層2、第2導電形のガードリング層5、第1のFP絶縁膜8、第2のFP絶縁膜8a、第1のFP電極9、第2のFP電極9a、第1の層間絶縁膜12、ゲート絶縁膜11、ゲート電極13、第1の電極16、及び第2の電極17を備える。第2のトレンチ7は、第1の半導体層の第1の表面から第1の半導体層中に延伸し、複数の第1のトレンチ6を囲み、ガードリング層の端を終端する。第1のFP電極は、第1のトレンチ内に第1のFP絶縁膜を介して設けられる。第2のFP電極は、第1のFP電極と電気的に接続され、第2のFP絶縁膜を介して、ガードリング層上から、第2のトレンチの第1のトレンチ側の側壁上を経て、第2のトレンチの底部上を第1のトレンチとは反対側に向かって延伸して設けられる。

(もっと読む)

メモリ用シフトレジスタ

【課題】大容量なメモリ用シフトレジスタを提供する。

【解決手段】メモリ用シフトレジスタは、基板101と、基板101上に形成され、基板101の主面に垂直な軸Lの周りを回転する螺旋形状を有するチャネル層111とを備える。さらに、メモリ用シフトレジスタは、基板101上に形成され、軸Lに平行な方向に延びており、チャネル層111内の電荷を転送するために使用される3本以上の制御電極1121,1122,1123を備える。

(もっと読む)

半導体装置

【課題】 半導体装置の耐圧の低下を抑制する。

【解決手段】 半導体装置54は、半導体基板50と、半導体基板の表面上に配置される絶縁膜20と、絶縁膜の表面上に配置される電極16,28と、電極16,18に電圧を印加する電圧印加回路44を有している。半導体基板50は、セル領域100と、そのセル領域に隣接する非セル領域200とを備える。セル領域100には半導体素子が形成されており、非セル領域200には耐圧構造が形成されている。絶縁膜20は、非セル領域の表面に形成されている。電極16,18は、半導体基板から電気的に分離されている。電圧印加回路44は、半導体素子に電圧が印加されていない期間の少なくとも一部において電極16,18に電圧を印加する。

(もっと読む)

半導体装置

【課題】耐圧を向上させ、オン抵抗を下げることが可能な半導体装置を提供する。

【解決手段】一態様に係る半導体装置は、MOSFETとして機能する第1領域、及び第1領域に隣接する第2領域を有する。第2領域は、第1半導体層、複数の第2トレンチ、第2絶縁層、及びフローティング電極層を有する。複数の第2トレンチは、第1半導体層の上面側から第1半導体層内に延びる。第2絶縁層は、第2トレンチの内壁に沿って形成される。フローティング電極層は、第2絶縁層を介して第2トレンチを埋めるように形成され且つフローティングとされる。

(もっと読む)

半導体装置

【課題】耐圧の向上、及び容量の低減を図ることができる半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、基板と、第1導通部と、第2導通部と、半導体部と、第1電極部と、第2電極部と、第1絶縁部と、第2絶縁部と、を備える。第1導通部はZ軸方向に延在する。第2導通部はZ軸方向に延在し、X軸方向に沿って第1導通部と離間する。半導体部は、第1導通部と第2導通部とのあいだに設けられる。第1電極部は、第1導通部と第2導通部とのあいだでZ軸方向に延在する。第2電極部は、第1電極部と第2導通部とのあいだでZ軸方向に延在し、第1電極部と離間する。第1絶縁部は、第1電極部と半導体部とのあいだに設けられ、第1電極部の境界面の法線方向に第1の厚さを有する。第2絶縁部は、第2電極部と半導体部とのあいだに設けられ、第2電極部の境界面の法線方向に、第1の厚さよりも厚い第2の厚さを有する。

(もっと読む)

電力用半導体装置

【課題】半導体チップの終端領域のアバランシェ耐量が高い電力用半導体装置を提供する。

【解決手段】本発明の実施形態の電力用半導体装置は、第1導電形の第1の半導体層1、第1の電極6、第2の電極9、第2導電形の第2の半導体層2、第2導電形の複数のガードリング層3、及び第1導電形の第3の半導体層4Cを備える。第2の半導体層2は、第1の半導体層1と第1の電極6との間に設けられ。複数の矩形の環状構造のガードリング層3は、第1の半導体層1の第1の表面に、第2の半導体層2とは離間し第1の電極6を取り囲むように設けられる。複数のガードリング層3の各層は、4つの辺部3Bと円弧状の4つのコーナー部3Cとを有する。第3の半導体層4Cは、複数のガードリング層3のうちの第1のガードリング層のコーナー部3Cと、第1の電極6側で離間して隣り合う第2のガードリング層のコーナー部3Cと、の間に設けられる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】活性領域の外側に位置する半導体層の表層部の電位を固定することができる半導体装置を提供する。

【解決手段】MOSFET1は、主表面10Aにトレンチ20が形成された半導体基板10と、ゲート酸化膜30と、ゲート電極40と、ソース配線60とを備える。半導体基板10は、n型のドリフト層12と、p型のボディ層13とを含む。トレンチ20は、ボディ層13を貫通してドリフト層12に達するように形成されている。トレンチ20は、平面的に見て活性領域10Bを取り囲むように配置される外周トレンチ22を含む。外周トレンチ22から見て活性領域10Bとは反対側の主表面10Bにはボディ層13が露出した電位固定領域10Cが形成されている。ソース配線60は、平面的に見て活性領域10Bに重なるように配置されている。電位固定領域10Cは、ソース配線60と電気的に接続されている。

(もっと読む)

41 - 50 / 1,730

[ Back to top ]