国際特許分類[H01L29/06]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体本体 (3,016) | 半導体本体の形状に特徴のあるもの;半導体領域の形状,相対的な大きさまたは配列に特徴のあるもの (1,731)

国際特許分類[H01L29/06]の下位に属する分類

整流,増幅,またはスイッチされる電流を流す電極が接続されている半導体領域をもつものであって,その電極が3つ以上の電極を持つ半導体装置の部分であるもの (1)

整流,増幅,またはスイッチされる電流を流さない電極が接続されている半導体領域をもつものであって,その電極が3つ以上の電極を持つ半導体装置の部分であるもの

国際特許分類[H01L29/06]に分類される特許

11 - 20 / 1,730

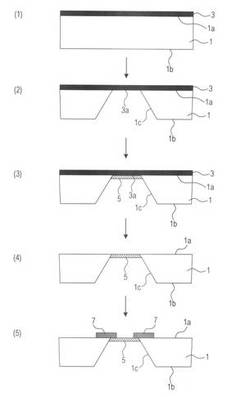

半導体素子及びその製造方法

【課題】スティッキングが生じにくい半導体素子及びその製造方法を提供することを目的とする。

【解決手段】一方の面1aに触媒層3が形成された基板1において、前記一方とは反対側から前記触媒層3の裏面3aに至る開口部1cを形成する工程と、前記開口部1cにおいて、前記触媒層3の裏面3aにグラフェン5を形成する工程と、前記触媒層3の少なくとも一部を除去する工程と、を有することを特徴とする半導体素子の製造方法。開口部1cの形成後、グラフェン5の形成前に、熱処理を行うことができる。グラフェン5を形成する前に、触媒層3の表面に保護層を形成することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】低電流領域でのオン電圧を低減することができる、SiC−IGBTを備える半導体装置およびその製造方法を提供すること。

【解決手段】エミッタ電極26と、エミッタ電極26に接続されたエミッタ領域41と、エミッタ領域41に対してSiC半導体層23の裏面25側にエミッタ領域41に接して形成されたチャネル領域39と、チャネル領域39に対してSiC半導体層23の裏面25側にチャネル領域39に接して形成されたSiCベース層33と、SiCベース層33に対してSiC半導体層23の裏面25側にSiCベース層33に接して形成されたコレクタ領域37と、コレクタ領域37に接続されたコレクタ電極27とを含む、SiC−IGBT9に対してMOSFET11を並列に接続する。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】炭化珪素半導体装置に含まれる炭化珪素層の側面の面方位を特定の結晶面により近づけることができる炭化珪素半導体装置の製造方法を提供する。

【解決手段】基板1上に、主表面が設けられた炭化珪素層19が形成される。炭化珪素層19の主表面の一部を覆うマスク17が形成される。主表面に対して傾斜した側面SSが炭化珪素層19に設けられるように、マスク17が形成された炭化珪素層19の主表面に対して、塩素系ガスを用いた熱エッチングが行われる。熱エッチングを行う工程は、塩素系ガスの分圧が50%以下である雰囲気下で行われる。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜上に良質のグラフェンを形成しうる半導体装置の製造方法を提供する。

【解決手段】第1の基板上に触媒金属膜を形成する工程と、触媒金属膜を触媒としてグラフェンを形成する工程と、グラフェン上に第1の絶縁膜を形成する工程と、第1の絶縁膜上に第1の金属膜を形成する工程と、第2の基板上に、第2の金属膜を形成する工程と、第1の金属膜の表面と第2の金属膜の表面とを対向させ、第1の金属膜と第2の金属膜とを接合する工程と、第1の基板を除去する工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】製造コストの増加を抑制することが可能な技術を提供することを目的とする。

【解決手段】半導体装置の製造方法は、(a)オフ角を有するSiC基板1上に、ドリフト層2と、酸化膜31と、レジスト32とをこの順に形成する工程と、(b)酸化膜31に第1開口部31aを形成するともに、レジスト32に第2開口部32bを形成する工程と、(c)不純物を、酸化膜31及びレジスト32を介してドリフト層2にイオン注入することにより、p型領域13,23をドリフト層2の上部に形成する工程とを備える。

(もっと読む)

スーパージャンクション構造を有する半導体装置

【課題】高温環境下で半導体装置に長時間逆バイアスを与えた場合であってもリーク電流が増加したり耐圧が低下したりすることのない、スーパージャンクション構造を有する半導体装置を提供する。

【解決手段】n−型半導体層(第1導電型の半導体層)114と、活性領域R1に形成された複数の柱状埋込層118と、活性領域R1に形成されたショットキーバリアメタル層(第1電極層)132と、耐圧領域R2に形成された複数のガードリング層(環状柱状埋込層)124と、耐圧領域R2及び周辺領域R3に形成された絶縁層130とを備える、スーパージャンクション構造を有する半導体装置であって、周辺領域R3に形成された第2ガードリング層(第2環状柱状埋込層)136と、周辺領域R3に形成された環状導電層142とをさらに備える、スーパージャンクション構造を有する半導体装置100。

(もっと読む)

半導体装置の製造方法

【課題】GaN系半導体を用い耐圧の異なるトランジスタを作り分ける。

【解決手段】基板1上方に第1、第2GaN系半導体層3,4、電極層5、第1絶縁膜6を積層し、電極層5及び第1絶縁膜6をパターニングして、第1ゲート電極5と第1絶縁膜6が積層された第1構造と、第2ゲート電極5と第1絶縁膜6が積層された第2構造を形成し、第1、第2構造を覆って第2絶縁膜7を形成し、第1ゲート電極5とその両側領域を露出する第1開口8SD、第2ゲート電極5を挟んでそれぞれ一方側、他方側に配置された第2、第3開口8S,8Dを有する第1マスクを用いて、第2絶縁膜7を異方性エッチングし、第1開口内8SDにおいて、第1構造の側面上にサイドウォール絶縁膜7SWを残しつつ、第1ゲート電極を挟んでコンタクトホール9S,9Dを形成し、第2、第3開口内に、それぞれコンタクトホール9S,9Dを形成し、各コンタクトホールに電極を形成する。

(もっと読む)

炭化珪素半導体装置

【課題】 少ない工程数で形成でき、耐熱性に優れた温度センサを備える炭化珪素半導体装置を得る。

【解決手段】 炭化珪素基板1の活性領域ARに形成された半導体素子と、活性領域ARを取り囲むように炭化珪素基板1中に形成されたウエル領域5と、炭化珪素基板1上に配設される多結晶シリコンからなるゲート電極8と、ゲート電極8と同時に形成され、その一部を用いて形成した測温抵抗体17と、を備えることを特徴とする。

(もっと読む)

グラフェン構造の製造方法及びこれを用いた半導体装置の製造方法

【課題】所望の位置にグラフェン膜を有するグラフェン構造及びこれを用いた半導体装置を提供する。

【解決手段】所定の基材3上において、炭素含有層4と、少なくともケイ素を含む炭素化合物層5とを順次に積層し、その上に絶縁膜層6を形成した後、絶縁膜層の一部をエッチングにより取り除いた基板に対してアニーリングを実施し、絶縁膜の除去部にのみグラフェン膜7を形成したグラフェン構造1を形成し、これを用いて表面にショットキー電極8、およびオーミック電極9,10を形成させて半導体装置2を作製する。

(もっと読む)

半導体装置

【課題】耐圧領域付近への電流集中と電力損失を抑制する半導体装置を提供する。

【解決手段】半導体装置1aは第1導電型の半導体基板2と、前記半導体基板の一方の側に設けられた第1主電極17と、前記半導体基板の他方の側に前記半導体基板の縁部から離れて設けられた第2導電型の第1半導体層11と、前記半導体基板の他方の側に前記縁部と前記第1半導体層との間において選択的に設けられた複数の第2導電型の第2半導体層12と、前記縁部から前記第1半導体層の一部を覆うように設けられた絶縁膜13と、前記絶縁膜及び前記第1半導体層の一部を覆うように設けられた導電膜14と、前記第1半導体層及び前記導電膜に接するように設けられた第2主電極15を有する。

(もっと読む)

11 - 20 / 1,730

[ Back to top ]