国際特許分類[H01L29/06]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体本体 (3,016) | 半導体本体の形状に特徴のあるもの;半導体領域の形状,相対的な大きさまたは配列に特徴のあるもの (1,731)

国際特許分類[H01L29/06]の下位に属する分類

整流,増幅,またはスイッチされる電流を流す電極が接続されている半導体領域をもつものであって,その電極が3つ以上の電極を持つ半導体装置の部分であるもの (1)

整流,増幅,またはスイッチされる電流を流さない電極が接続されている半導体領域をもつものであって,その電極が3つ以上の電極を持つ半導体装置の部分であるもの

国際特許分類[H01L29/06]に分類される特許

61 - 70 / 1,730

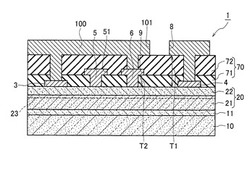

窒化物半導体装置

【課題】ドレイン配線電極に起因する電流コラプス現象への影響が抑制され、且つ耐圧が向上された窒化物半導体装置を提供する。

【解決手段】窒化物半導体からなるデバイス層と、デバイス層上に互いに離間して配置されたソース電極及びドレイン電極と、ソース電極とドレイン電極間でデバイス層上に配置されたゲート電極と、デバイス層上に配置された層間絶縁膜と、ドレイン電極とゲート電極間において層間絶縁膜を介してデバイス層と対向して配置され、ドレイン電極と電気的に接続されたドレイン配線電極と、ゲート電極とドレイン電極間においてデバイス層上に層間絶縁膜を介してデバイス層と対向して配置されたドレイン電極に比べて低電位側のフィールドプレートとを備え、ドレイン配線電極下方の層間絶縁膜の膜厚が、フィールドプレート下方の層間絶縁膜の膜厚よりも厚い。

(もっと読む)

有機電界効果型トランジスタ

【課題】カーボンナノチューブを含有する活性層を有する有機電界効果型トランジスタにおいて、熱プロセス、経時変化、外部環境に対して、移動度、Von、ヒステリシスの性能を安定化すること。

【解決手段】ゲート電極、ゲート絶縁層、カーボンナノチューブを含有する活性層、該活性層に対して前記ゲート絶縁層と反対側に形成された架橋構造を持つポリシロキサンを含む第2絶縁層、ソース電極およびドレイン電極を有する有機電界効果型トランジスタ。

(もっと読む)

炭化ケイ素デバイス用のエッジ終端構造およびエッジ終端構造を含む炭化ケイ素デバイスの製造方法

【課題】炭化ケイ素デバイスの改善されたエッジ終端構造を提供する。

【解決手段】炭化ケイ素半導体デバイス用のエッジ終端構造は、少なくとも炭化ケイ素ベース接合を部分的に取り囲んで、炭化ケイ素層中において、所定間隔で配置された複数の同心円のフローティングガードリング34を有すると共に、フローティングガードリング上に設けられた絶縁層、及びフローティングガードリング同士の間でかつ炭化ケイ素層の表面の近くに設けられた炭化ケイ素表面電荷補償領域38を有する。炭化ケイ素層上に窒化ケイ素層56が設けられ、窒化ケイ素層上に有機保護層66が設けられる。酸化膜層が窒化ケイ素層と炭化ケイ素層の表面との間に存在してもよい。エッジ終端構造の形成・製造方法を開示されている。

(もっと読む)

半導体装置およびその製造方法

【課題】不純物イオンの注入による悪影響を防止しつつ水平方向の耐圧を向上できる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、素子を構成し、電流が流れる一対の不純物領域が、半導体基板の第1主面の表層に形成されたものであり、水平方向の耐圧を確保するため、フィールドプレート33を有している。これに加えて、この半導体装置は、半導体基板の表面から、素子の電流経路となる第1不純物領域37および第2不純物領域38よりも深い所定の深さおいて、少なくとも第1不純物領域および第2不純物領域の間の領域に半導体基板と同一成分の非晶質層24を有する。この非晶質層は、単結晶および多結晶よりも高抵抗の層であり、擬似的なフィールドプレートとして機能する。そして、この非晶質層は、不活性元素のイオン注入により形成される。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】多様な構造を実現することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1の上方に形成された化合物半導体層2と、が設けられている。化合物半導体層2には、第1の不純物の活性化により発生した第1導電型のキャリアを含む第1の領域2aと、第1の不純物と同一種類の第2の不純物の活性化により発生したキャリアを、第1の領域2aよりも低濃度で含有する第2の領域2bと、が設けられている。

(もっと読む)

半導体装置の製造方法

【課題】SiC基板上に形成されたデバイスに対して、低温の熱工程にて良好なオーミック特性を備える電極を実現する半導体装置の製造方法を提供する。

【解決手段】実施の形態の半導体装置の製造方法は、炭化珪素(SiC)で形成されるn型不純物領域上およびp型不純物領域上に金属シリサイド膜を形成し、n型不純物領域上の金属シリサイド膜中にリン(P)をイオン注入し、第1の熱処理を行い、p型不純物領域上の金属シリサイド膜中にアルミニウム(Al)をイオン注入し、第1の熱処理よりも低温の第2の熱処理を行う

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置について、小型化を図りつつ、ドレイン耐圧を向上する。

【解決手段】ゲート電極20と、ゲート電極20と離間するソース電極24と、平面視でゲート電極20からみてソース電極24の反対側に位置し、かつゲート電極20と離間するドレイン電極22と、平面視でゲート電極20とドレイン電極22の間に位置し、絶縁膜26を介して半導体基板10上に設けられ、かつゲート電極20、ソース電極24およびドレイン電極22と離間する少なくとも一つのフィールドプレート電極30と、絶縁膜26中に設けられ、かつフィールドプレート電極30と半導体基板10を接続する少なくとも一つのフィールドプレートコンタクト40と、を備え、平面視でフィールドプレート電極30は、フィールドプレートコンタクト40からソース電極24側またはドレイン電極22側の少なくとも一方に延伸している。

(もっと読む)

半導体装置

【課題】接合終端領域における電界を緩和し、高耐圧化可能な半導体装置を提供する。

【解決手段】第1導電型の不純物を有する第1半導体領域と、第1半導体領域上に配置された、第1導電型と異なる第2導電型の第2半導体領域とを有する半導体基体には、コレクタ電極若しくはドレイン電極を有するスイッチング素子が形成された素子領域と、上方から見て半導体基体の最外周部に形成された、第2半導体領域の上面から第1半導体領域に達する終端トレンチと、終端トレンチの側壁および底面に形成された絶縁膜と、絶縁膜を介して溝の内側に埋め込まれた電極とを有し、溝の内側に埋め込まれた電極が第1半導体領域又はコレクタ領域若しくはドレイン電極と接続された等電位リングである。

(もっと読む)

IV族半導体ナノ細線の製造方法

【課題】IV族半導体ナノ細線の製造方法並びに構造制御方法を提供する。

【解決手段】気相−液相−固相(Vapor-Liquid-Solid : VLS)成長法により、SiとGeの混晶ナノ細線を成長し、酸化濃縮法によりSiO2膜で被覆されたGeナノ細線を作製する。また、気相-液相-固相成長法により、Si結晶およびSiとGeの混晶からなる超格子ナノ細線を作製し、酸化濃縮法を利用してナノメートル(nm)スケールでサイズ制御された、SiとGeの混晶から成るナノディスク又はナノドットを周期的に配列したナノ細線を作製する。

(もっと読む)

半導体装置及びその製造方法

【課題】電極端部への電界集中を抑えるとともに、ゲート電極の変形や、ゲート−フィールドプレート間に生じる容量による特性劣化を抑える。

【解決手段】半導体装置において、第1の基板と、第1の基板表面に形成された素子領域と、素子領域と接続され、第1の基板上に形成されたゲート電極、ソース電極及びドレイン電極と、第1の基板と、第1の面で積層される第2の基板と、第2の基板を貫通し、電極上に配置されるビアホールと、ビアホール内に形成され、電極と接続される金属層と、第2の基板に設けられ、ゲート電極、ソース電極及びドレイン電極のいずれかと接続されるフィールドプレート電極と、を備える。

(もっと読む)

61 - 70 / 1,730

[ Back to top ]