国際特許分類[H01L29/788]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体装置の型 (42,689) | 整流,増幅またはスイッチされる電流を流さない電極に電流のみまたは電位のみを与えることにより制御できるもの (37,192) | ユニポーラ装置 (34,588) | 電界効果トランジスタ (34,488) | 絶縁ゲートによって生じる電界効果を有するもの (29,475) | 浮遊ゲートを有するもの (4,374)

国際特許分類[H01L29/788]に分類される特許

1,071 - 1,080 / 4,374

半導体記憶装置及び半導体記憶装置の製造方法

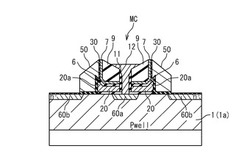

【課題】フローティングゲートとコントロールゲートとのオーバーラップ量のバラツキを抑制する。

【解決手段】基板(1)と、ゲート絶縁膜(2)を介してその基板(1)の上に設けたれたフローティングゲート(20)と、トンネル絶縁膜(30)を介してそのフローティングゲート(20)の隣に設けられたコントロールゲート(50)と、そのフローティングゲート(20)の上に設けられたスペーサー絶縁膜(9)と、そのスペーサー絶縁膜(9)とそのコントロールゲート(50)との間に設けられた保護膜(7)とを具備する半導体記憶装置(MC)を構成する。そのような半導体記憶装置(MC)において、その保護膜(7)は、スペーサー絶縁膜(9)以外の部分をエッチングするときに、スペーサー絶縁膜(9)の側面のストッパーとして機能している。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセルトランジスタの特性が均一な不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】シリコン基板上にボロンドープドポリシリコン層とノンドープドポリシリコン層とを交互に積層させて積層体を形成し、X方向に延びるスリットを形成することにより、ボロンドープドポリシリコン層を複数本のゲート電極21に分断する。次に、スリット内に絶縁材料を埋め込んで絶縁板材を形成し、積層体を貫通するように貫通ホール30を形成する。次に、貫通ホール30を介してウェットエッチングを行い、ノンドープドポリシリコン層を除去する。次に、貫通ホール30の内面上及びゲート電極21の上下面上にブロック絶縁膜35を堆積させる。次に、ブロック絶縁膜35上に電荷蓄積膜36及びトンネル絶縁膜37を堆積させる。次に、貫通ホール30内にポリシリコンを埋め込んで、シリコンピラー39を形成する。

(もっと読む)

マルチドットフラッシュメモリ

【課題】マルチドットフラッシュメモリの書き込み/消去の低消費電力化を図る。

【解決手段】本発明の例に係わるマルチドットフラッシュメモリは、書き込み/消去の対象となる選択されたフローティングゲートの左側に存在するビット線BL13,BL12,BL11,…の電位V2(1), V2(2), V2(3),…を、V2(1)>V2(2)>V2(3)>…とし、選択されたフローティングゲートの右側に存在するビット線BL14,BL15,BL16,…の電位V1(1), V1(2), V1(3),…を、V1(1)<V1(2)<V1(3)<…とする。但し、V2(1)は、プラス電位、V1(1)は、マイナス電位である。また、ビット線の電位は、選択されたフローティングゲートから離れるに従い、0Vに収束する。

(もっと読む)

不揮発性メモリセルのフローティングゲート形成方法

【課題】基板上に逆T形状を有するフローティングゲートを持った不揮発性メモリ構造を形成する、複雑ではない方法を提起する。

【解決手段】半導体材料の基板に少なくとも一つのメモリセルアレイを備えた不揮発性メモリの製造方法であって、メモリセルは、STI構造によって、互いに自己整合され互いから分離される。メモリセルは、メモリセルアレイに沿った断面において逆T形状を有するフローティングゲートを備える。ここで、逆T形状は、フローティングゲートの側壁の上部を酸化させることにより形成され、それによって犠牲酸化物層を形成し、その後、STI構造をさらにエッチバックすると同時に犠牲酸化物層を除去する。

(もっと読む)

半導体装置の製造方法

【課題】フラッシュメモリと、精度が低くても高耐圧性が要求されるキャパシタと、耐圧性が低くても高精度が要求されるキャパシタとを備えた半導体装置を比較的少ない工程で製造できる半導体装置の製造方法を提供する。

【解決手段】半導体基板10上に形成されたシリコン膜13により、フラッシュメモリのフローティングゲートと高耐圧キャパシタの下部電極13bとを形成する。この場合、シリコン膜13中の不純物濃度を、フラッシュメモリに適した濃度とする。その後、半導体基板10に不純物をイオン注入して高精度キャパシタの下部電極となる高濃度不純物領域15を形成する際に、高耐圧キャパシタの下部電極13bに不純物を追加注入し、下部電極13bの不純物濃度を向上させる。次いで、高精度キャパシタの誘電体膜12を、増速酸化により形成する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】選択ゲート電極を低抵抗化し、半導体ピラーを選択する選択ゲートトランジスタの応答特性が良好な不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】第1方向に交互に積層された複数の電極膜WLと複数の電極間絶縁膜14とを有する積層構造体MLと、前記第1方向において積層構造体MLに積層された選択ゲート電極SGと、積層構造体MLと選択ゲート電極SGとを前記第1方向に貫通する半導体ピラーSPと、電極膜WLのそれぞれと半導体ピラーSPとの交差部に設けられた記憶部と、半導体ピラーSPと選択ゲート電極SGとの間に設けられた選択ゲート絶縁膜SGIと、を備えた不揮発性半導体記憶装置が提供される。選択ゲート電極SGは、選択ゲート電極SGの前記第1方向に対して垂直な面上に設けられた第1シリサイド層51を有する。

(もっと読む)

半導体記憶素子の製造方法

【課題】金属ナノ結晶からなる離散的フローティングゲートを、移流集積法により形成する半導体記憶素子の製造方法を提供する。

【解決手段】製造方法は、シリコン基板1と、シリコン基板1上に形成されたトンネル絶縁膜に対向するように配置された第2の基板21との間に、金属ナノ粒子が分散された粒子分散液22を充填する充填工程と、トンネル絶縁膜の表面に沿った方向に、第2の基板21をシリコン基板1に対して相対的に移動させることにより、トンネル絶縁膜の表面における第2の基板21から露出した領域に形成される粒子分散液22のメニスカス領域23において、粒子分散液22の溶媒を蒸発させることにより、トンネル絶縁膜上に金属ナノ粒子を離散的に配置する。

(もっと読む)

半導体装置の製造方法

【課題】高アスペクト比のコンタクトホールを容易な加工で形成可能な半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、基板10上に第1の加工層を形成する工程と、第1の加工層に第1のコンタクトホールCS1を形成する工程と、第1のコンタクトホールCS1内に犠牲膜42aを埋め込む工程と、犠牲膜42aが埋め込まれた第1のコンタクトホールCS1上に第2の加工層44を形成する工程と、犠牲膜42a上の第2の加工層44に犠牲膜42aに達する第2のコンタクトホールCS2を形成する工程と、第2のコンタクトホールCS2を通じて第1のコンタクトホールCS1内から犠牲膜42aを除去し、第1のコンタクトホールCS1と第2のコンタクトホールCS2とを連通させる工程と、を備えた。

(もっと読む)

情報記録再生装置

【課題】高記録密度かつ低消費電力を実現した情報記録再生装置を提供する。

【解決手段】情報記録再生装置は、電圧パルスの印加によって所定の抵抗値を持つ第1の状態とこの第1の状態よりも高い抵抗値を持つ第2の状態との間を可逆的に遷移する記録層からなるメモリセルを備える。前記記録層は、組成式AxMyX4(0.1≦x≦1.2、2<y≦2.9)で表される第1化合物層を含む。前記Aは、Mn(マンガン)、Fe(鉄)、Co(コバルト)、Ni(ニッケル)、及びCu(銅)のグループから選択される少なくとも1種類の元素である。前記Mは、Al(アルミニウム)、Ga(ガリウム)、Ti(チタン)、Ge(ゲルマニウム)、及びSn(スズ)のグループから選択される少なくとも1種類の元素であり、かつ、前記Aとは異なる元素である。前記Xは、O(酸素)であることを特徴とする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】階段状に加工された複数層の電極層とコンタクト電極との接触抵抗を低減する半導体装置の製造方法及び半導体装置を提供する。

【解決手段】本発明の半導体装置の製造方法は、電極層WL1〜WL4と絶縁層25とを交互に複数積層する工程と、その積層体の一部を階段状に加工すると共に各段の表面に電極層WL1〜WL4を露出させる工程と、露出された電極層WL1〜WL4に接する金属膜43を形成する工程と、電極層WL1〜WL4における少なくとも金属膜43と接する部分に金属化合物44を形成する工程と、金属膜43の未反応部を除去した後層間絶縁層46を形成する工程と、層間絶縁層46を貫通しそれぞれが対応する各段の電極層WL1〜WL4の金属化合物44に達する複数のコンタクトホール47を形成する工程と、コンタクトホール47内にコンタクト電極50を設ける工程とを備えた。

(もっと読む)

1,071 - 1,080 / 4,374

[ Back to top ]