国際特許分類[H01L29/788]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体装置の型 (42,689) | 整流,増幅またはスイッチされる電流を流さない電極に電流のみまたは電位のみを与えることにより制御できるもの (37,192) | ユニポーラ装置 (34,588) | 電界効果トランジスタ (34,488) | 絶縁ゲートによって生じる電界効果を有するもの (29,475) | 浮遊ゲートを有するもの (4,374)

国際特許分類[H01L29/788]に分類される特許

1,041 - 1,050 / 4,374

半導体装置の製造方法

【課題】ロジック回路とメモリ回路を混載した半導体装置において、ロジック回路部に形成されるレジストパターン形状の精度低下抑制に寄与する半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、ロジックトランジスタ、不揮発性メモリをそれぞれ形成する第1及び第2の活性領域を画定する素子分離絶縁膜を、STIで形成する工程と、第2の活性領域上方に、フローティングゲートとなる導電層を形成する工程と、導電層上及びその外側の領域を覆って、窒化シリコンを含む絶縁膜を形成する工程と、第1の活性領域の隣接部分の素子分離絶縁膜上の窒化シリコンを含む絶縁膜を覆い、第1の活性領域を露出するマスクを用いてエッチングする工程と、第1の活性領域の隣接部分の素子分離絶縁膜上の窒化シリコンを含む絶縁膜上に端部の配置されたフォトレジストパターンを形成する工程とを有する。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】階段部に欠陥を生じさせることなく歩留まりを向上させた不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、メモリ領域AR1及び周辺領域AR2に亘って積層されたワード線導電層41a〜41dと、メモリ領域AR1にてワード線導電層41a〜41dに取り囲まれ、基板に対して垂直方向に延びる柱状部45Aを含むU字状半導体層45と、柱状部45Aの側面とワード線導電層41a〜41dとの間に形成されたメモリゲート絶縁層44とを備える。ワード線導電層41a〜41dは、メモリ領域AR1にてカラム方向に第1ピッチP1をもって配列されて、ロウ方向を長手方向とするストライプ状に形成された溝T1B、周辺領域AR2にてカラムに第2ピッチP2をもって配列されて、ロウ方向を長手方向とするストライプ状に形成された溝T2を備える。

(もっと読む)

Fin−FET型不揮発性メモリ・セル及びアレイ並びにその製造方法

不揮発性メモリ・セルが、基板層を有し、第1の導電型のフィン形状半導体部材が基板層上にある。フィン形状部材は、第2の導電型の第1の領域と、第1の領域から離間配置された第2の導電型の第2の領域とを有し、チャネル領域が第1の領域と第2の領域との間に延びている。フィン形状部材は、第1の領域と第2の領域との間に上面及び2つの側面を有する。ワード線が、第1の領域に隣接し、チャネル領域の第1の部分の上面及び2つの側面に容量結合される。浮遊ゲートが、ワード線に隣接し、上面から絶縁され、チャネル領域の第2の部分の2つの側面に容量結合される。 (もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】安定した動作を実行可能な不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】メモリストリングMSは、基板上に積層方向に延びる柱状部45Aを含むU字状半導体層45と、柱状部45Aを取り囲むように形成された電荷蓄積層44bと、電荷蓄積層44bを取り囲むように積層されたワード線導電層41a〜41dとを備える。ドレイン側選択トランジスタSDTrは、柱状部45Aの上面に接して積層方向に延びるドレイン側柱状半導体層57と、ドレイン側柱状半導体層57を取り囲むように形成された電荷蓄積層55bと、電荷蓄積層55bを取り囲むように形成されたドレイン側導電層51とを備える。電荷蓄積層55bは、ドレイン側導電層51の下層からドレイン側導電層51の上端近傍まで形成され、且つその上端近傍よりも上層には形成されていない。

(もっと読む)

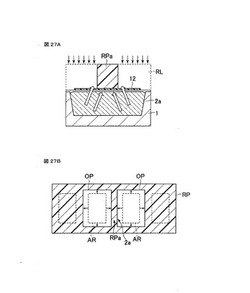

半導体記憶装置及びその製造方法

【課題】キャパシタ素子の配置面積低減が可能な半導体記憶装置を提供する。

【解決手段】メモリセル領域5及び周辺回路領域6を複数の素子形成領域に分離し、半導体基板11表面より上に上面を有する素子分離絶縁膜17と、メモリセル領域5の素子領域7上に、順に、トンネル絶縁膜13a、第1下層電極層15a、第1電極間絶縁膜19a、及び第1上層電極層25aとを有するメモリセル及び選択ゲートトランジスタ41、43と、周辺回路領域6の素子形成領域上に、上端に凹部18が加工された第2下層電極層15b、この凹凸面及び素子分離絶縁膜17上に配設され、第1電極間絶縁膜19aと同じ膜厚の第2電極間絶縁膜19b、及び第2電極間絶縁膜19b上に第2下層電極層15bに対応した凹凸の下面の第2上層電極層25bを有し、凹部18の底面が第1下層電極層15aの上面と同じ高さであるキャパシタ素子45とを備える。

(もっと読む)

不揮発スイッチ素子、その動作方法及びそれを用いた回路

【課題】高耐圧かつ不揮発のスイッチ素子を提供する。

【解決手段】上記課題を解決するため本発明のスイッチ素子は、半導体基板中に作られたソース・ドレインと、前記半導体基板上に作られたゲート絶縁膜と、前記ゲート絶縁膜の上に形成された電荷蓄積層と、前記電荷蓄積層の上に形成され前記電荷蓄積層が凹みに接触するイオン伝導層と、前記イオン伝導層の上に形成され前記イオン伝導層の凹みに接触する電荷注入層と、前記イオン伝導層の両脇に形成されたパス制御端子を有する。

(もっと読む)

半導体素子及びその形成方法

【課題】半導体素子及びその形成方法を提供する。

【解決手段】本発明の半導体素子の形成方法は、基板上に半導体構造物及び絶縁パターンを形成し、絶縁パターンの一面によって定義される側壁と半導体構造物の底によって定義される底を有するオープニングを形成し、オープニングを満たす第1金属膜を形成し、第1金属膜を湿式エッチングしてオープニングの側壁を少なくとも一部露出させ、第1金属膜上に第2金属膜を選択的に形成することを含む。

(もっと読む)

不揮発性半導体記憶装置

【課題】選択消去が可能な不揮発性半導体記憶装置を提供する。

【解決手段】メモリ部と制御部とを備える不揮発性半導体記憶装置を提供する。メモリ部は、互いに電気的に分離された第1、第2第半導体層に形成された第1、第2メモリストリングMCS1、MCS2と、第1、第2半導体層に接続された第1、第2配線W11、W12と、を有する。第1、第2メモリストリングは、複数のメモリセルを有する第1、第2メモリセル群と、第1、第2選択ゲートと、を有する。第1メモリセル群の選択セルトランジスタCL1を選択的に消去する際に、制御部は、第1配線に高電圧Vppを、選択セルトランジスタの制御ゲートに0Vを、選択セルトランジスタ以外の第1メモリストリングの非選択セルの制御ゲート、及び、第1選択ゲートに中間電圧Vmを、第2配線に中間電圧以下の低電圧Vccまたは0Vを印加する。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】ワード線引き出し部を活性領域の上に形成する構成としながら、リーク電流を抑制する。

【解決手段】側壁転写プロセスで形成されたワード線をワード線引き出し部WLaでループカットすると共に、ワード線引き出し部WLaを半導体基板2の活性領域Sa上に配設する構成であって、電極間絶縁膜4に選択ゲートトランジスタ用開口4aを形成する際にワード線引き出し部形成領域にループカット用開口4bを形成しておき、電極間絶縁膜4およびゲート絶縁膜3に対して選択的にエッチングを行うことによりワード線引き出し部の上層電極および下層電極を連続的に分離しループカットできるようにした。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】制御ゲート電極からリークした電子のエネルギーの増加を抑制し、トンネル絶縁膜の絶縁性の劣化を防止する。

【解決手段】本発明の例に係わる不揮発性半導体記憶装置は、半導体層101と、半導体層101の表面に形成された第1の絶縁膜102と、第1の絶縁膜102の表面に形成された電荷蓄積膜103と、電荷蓄積膜の表面に形成された第2の絶縁膜104と、第2の絶縁膜104の表面に形成された制御ゲート電極105とを具備し、電荷蓄積膜103及び第2の絶縁膜104の少なくとも一方に、散乱によって電子のエネルギーを減少させる非弾性散乱層が少なくとも一層含まれている。

(もっと読む)

1,041 - 1,050 / 4,374

[ Back to top ]