国際特許分類[H01L29/788]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体装置の型 (42,689) | 整流,増幅またはスイッチされる電流を流さない電極に電流のみまたは電位のみを与えることにより制御できるもの (37,192) | ユニポーラ装置 (34,588) | 電界効果トランジスタ (34,488) | 絶縁ゲートによって生じる電界効果を有するもの (29,475) | 浮遊ゲートを有するもの (4,374)

国際特許分類[H01L29/788]に分類される特許

161 - 170 / 4,374

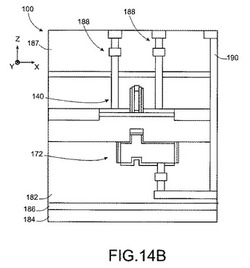

三次元集積回路を作製する方法

【課題】集積回路を作製する新規なタイプの方法を提供する。

【解決手段】少なくとも第3の層がその間に配置された、少なくとも半導体の第1および第2の層を備える基板を作製するステップと、少なくとも第1のMOSデバイスを作製するステップであって、その活性領域が半導体の第1の層の少なくとも一部に形成される、ステップと、少なくとも第2のMOSデバイスを作製するステップであって、その活性領域が半導体の第2の層の少なくとも一部に形成され、第2のMOSデバイスの活性領域が第2のMOSデバイスのゲートと第1のMOSデバイスの活性領域との間に配置される、ステップとを少なくとも含む、集積電子回路を作製する方法。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】選択ゲートトランジスタや周辺回路部のトランジスタの下部電極の抵抗値を低減し、しきい値電圧の増加も図れるようにする。

【解決手段】ゲート電極の加工時に、選択ゲートトランジスタのゲート電極SGD−SGD間の側壁部と、周辺回路部のトランジスタのゲート電極PGの両側壁とに、多結晶シリコン膜4の上部に段差形状を形成し、傾斜部4dを設ける。ゲート電極の多結晶シリコン膜6のシリサイド加工時に、多結晶シリコン膜4の傾斜部4dからもシリサイド化を進行させ、シリサイド膜7および7aを形成する。これにより、ゲート電極SGDおよびPGの下部電極においても低抵抗化を図ることができる。多結晶シリコン膜4に分断層4aを設けることで、シリサイド反応を停止させたり、設けないでゲート絶縁膜3の部分までシリサイド反応させてしきい値電圧を増加させたりできる。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】シリサイド工程によるゲート絶縁膜の金属汚染や、メモリセルのショートチャネル効果を抑制する。

【解決手段】実施形態によれば、不揮発性半導体記憶装置は、半導体基板と、前記半導体基板上に順に形成された第1絶縁層、電荷蓄積層、第2絶縁層、および制御電極を有し、前記電荷蓄積層の側面が傾斜面を有する複数のメモリセルトランジスタとを備える。さらに、前記装置は、前記メモリセルトランジスタの側面と、前記メモリセルトランジスタ間の前記半導体基板の上面に形成された第1の絶縁膜部分と、前記メモリセルトランジスタ間のエアギャップ上と前記メモリセルトランジスタ上に連続して形成された第2の絶縁膜部分と、を有する1層以上の絶縁膜を備える。さらに、前記メモリセルトランジスタ間の前記半導体基板の上面から前記エアギャップの下端までの第1距離は、前記メモリセルトランジスタの側面に形成された前記絶縁膜の膜厚よりも大きい。

(もっと読む)

半導体集積回路装置

【課題】過電圧がLSIの電源端子に印加されたことを確認できるようにする。

【解決手段】半導体集積回路装置(10)は、内部回路(11)と、上記内部回路に電源電圧を供給するための電源端子(15,16)とを含む。このとき、上記内部回路の電源電圧として想定されるレベルを越える電圧(過電圧)が上記電源端子に印加された事実を記録するための過電圧印加情報記録回路(12)を設ける。過電圧印加情報記録回路には、過電圧が上記電源端子に印加された事実が記録されているため、それに基づいて、過電圧がLSIの電源端子に印加されたことを確認することができる。

(もっと読む)

不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置

【課題】メモリセルトランジスタのゲート電極間の空隙の形状を最適化し、高性能、高信頼性を実現する不揮発性半導体記憶装置の製造方法。

【解決手段】実施の形態の不揮発性半導体記憶装置の製造方法は、半導体基板上に、第1のゲート絶縁膜、第1のフローティングゲート電極、第1のゲート間絶縁膜、第1のコントロールゲート電極、第1のゲートマスク絶縁膜の積層構造を有する複数のメモリセルゲート電極を形成する。メモリセルゲート電極の側壁部に保護膜を形成し、その一部を第1のコントロールゲート電極の側壁部の一部が露出するよう除去する。金属膜を形成し、熱処理により、金属膜と第1のコントロールゲート電極を反応させ第1の金属半導体化合物層を形成する。メモリセルゲート電極間を埋め込み、内部に空隙を有する層間絶縁膜であって、第1のコントロールゲート電極の上面よりも半導体基板から離れた位置に空隙の上端が位置する層間絶縁膜を形成する。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、酸化物半導体層に接して設けられた絶縁層と、を有し、酸化物半導体層は、該酸化物半導体層の端面において、ソース電極またはドレイン電極と接し、且つ該酸化物半導体層の上面において、絶縁層を介して、ソース電極またはドレイン電極と重なる半導体装置である。

(もっと読む)

不揮発性半導体記憶装置とその製造方法

【課題】書き込み特性を向上することが可能な不揮発性半導体記憶装置とその製造方法を提供する。

【解決手段】複数のゲート電極構造13は、半導体基板11上に形成されたゲート絶縁膜12、電荷蓄積層14、ゲート間絶縁膜15、第1制御ゲート16、及び前記第1制御ゲートより幅が広い第2制御ゲート電極17を有する。絶縁膜19は、制御ゲート電極17間及び制御ゲート電極より上方に形成された空隙19を有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】高い信頼性を有し且つ安価な不揮発性半導体記憶装置を提供する。

【解決手段】この不揮発性半導体記憶装置において、メモリストリングスは、基板に対して垂直方向に延びる一対の柱状部、及び前記一対の柱状部の下部を連結させるように形成された連結部を有する半導体層と、前記柱状部の側面を取り囲むように形成された電荷蓄積層と、前記柱状部の側面及び前記電荷蓄積層を含む第1の絶縁膜と、前記柱状部の側面及び前記第1の絶縁膜を覆うように形成された第1導電層と、前記連結部の周囲に形成される第2の絶縁膜と、前記連結部に前記ゲート絶縁膜を介して形成される第2導電層とを備える。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】短チャネル効果が抑制され、微細化を実現しつつ、安定した電気的特性を付与する半導体装置を提供する。また、上記半導体装置を作製する。

【解決手段】酸化物絶縁層に設けたトレンチに、トレンチに沿って成膜される酸化物半導体膜と、酸化物半導体膜と接するソース電極及びドレイン電極と、酸化物半導体膜上のゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有する半導体装置(トランジスタ)を設ける。該トレンチは下端コーナ部に曲面を有し、側部が酸化物絶縁層上面に対して略垂直な側面を有する。また、トレンチの上端の幅がトレンチの側面の幅の1倍以上1.5倍以下である。

(もっと読む)

半導体装置及びその製造方法

【課題】高品質な配線を有する半導体装置を提供する。

【解決手段】第1の領域100及び第2の領域200に設けられた第1の絶縁層10と、第1の領域に設けられた第1の絶縁層上に形成された第2の絶縁層11aと、第2の領域200に設けられた第1の絶縁層上に形成され、第2の絶縁層と略同一の高さを有する第3の絶縁層11cと、第1の領域に設けられた第1の絶縁層上及び第2の絶縁層の両方の側壁に形成された第1の配線層13aと、第2の領域に設けられた第1の絶縁層上、及び第3の絶縁層の上面及び側壁上に形成された第2の配線層13bと、第1の絶縁層、第2の絶縁層、第1の配線層、及び第2の配線層を覆う第4の絶縁層15と、第1の領域に設けられた第4の絶縁層内に形成され、第1の配線層に接続された第1のコンタクトプラグ17aと、第2の領域に設けられた第4の絶縁層内に形成され、第2の配線層に接続された第2のコンタクトプラグ17bと、を備える。

(もっと読む)

161 - 170 / 4,374

[ Back to top ]