国際特許分類[H01L29/788]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体装置の型 (42,689) | 整流,増幅またはスイッチされる電流を流さない電極に電流のみまたは電位のみを与えることにより制御できるもの (37,192) | ユニポーラ装置 (34,588) | 電界効果トランジスタ (34,488) | 絶縁ゲートによって生じる電界効果を有するもの (29,475) | 浮遊ゲートを有するもの (4,374)

国際特許分類[H01L29/788]に分類される特許

181 - 190 / 4,374

不揮発性半導体記憶装置

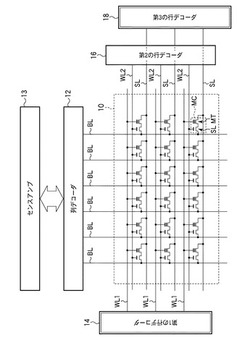

【課題】高速で動作し得る不揮発性半導体記憶装置を提供する。

【解決手段】選択トランジスタとメモリセルトランジスタMTとを有するメモリセルMCがマトリクス状に配列されて成るメモリセルアレイ10と、ビット線BLの電位を制御する列デコーダ12と、第1のワード線WL1の電位を制御する電圧印加回路14と、第2のワード線WL2の電位を制御する第1の行デコーダ16と、ソース線SLの電位を制御する第2の行デコーダ18とを有し、列デコーダは電圧印加回路及び第2の行デコーダより耐圧の低い回路により構成されており、第1の行デコーダは電圧印加回路及び第2の行デコーダより耐圧の低い回路により構成されている。ビット線と第2のワード線とが高速で制御され得るため、メモリセルトランジスタに書き込まれた情報を高速で読み出すことができる。

(もっと読む)

不揮発性半導体記憶装置

【課題】ビット線接続部の微細化を実現する不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、p型の半導体基板101と、半導体基板101内に形成され、メモリセルのビット線とセンスアンプ部を接続するビット線接続トランジスタHTkが形成されるp型の第1のPウェル102と、第1のPウェル102を囲み、第1のPウェル102を半導体基板101から電気的に分離するn型の第1のNウェル103と、を備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】正確に書き込み動作を行うことができる不揮発性半導体記憶装置を提供する。

【解決手段】

複数の素子分離絶縁膜は、半導体層中に形成され、第1方向を長手方向とする。複数の素子形成領域は、素子分離絶縁膜により分離して形成される。素子形成領域にはメモリストリングが形成される。複数の素子形成領域群が素子形成領域により構成される。メモリセルアレイは、第1方向と直交する第2方向において、前記素子形成領域群の間隔が前記素子形成領域群の中の前記素子形成領域の間隔より大きくされている。制御回路は、前記メモリセルアレイに対する書き込み動作を、前記素子形成領域群ごとに実行する。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置

を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極およびド

レイン電極と、酸化物半導体層、ソース電極およびドレイン電極を覆うゲート絶縁層と、

ゲート絶縁層上のゲート電極と、を有し、酸化物半導体層の厚さは1nm以上10nm以

下であり、ゲート絶縁層は、ゲート絶縁層に用いられる材料の比誘電率をεr、ゲート絶

縁層の厚さをdとして、εr/dが、0.08(nm−1)以上7.9(nm−1)以下

の関係を満たし、ソース電極とドレイン電極との間隔は10nm以上1μm以下である半

導体装置である。

(もっと読む)

不揮発性半導体記憶装置

【課題】データの劣化を抑制した不揮発性半導体記憶装置を提供する。

【解決手段】メモリセルは、半導体層、電荷蓄積層、及び導電層を備える。半導体層は、半導体基板に対して垂直方向に延び、メモリセルのボディとして機能する。電荷蓄積層は、半導体層の側面に設けられ、電荷を蓄積する。導電層は、半導体層と電荷蓄積層を挟むよう設けられ、メモリセルのゲートとして機能する。制御回路は、第1プログラム動作の後、第2プログラム動作を実行する。第1プログラム動作は、メモリセルのボディに第1電圧を印加し且つメモリセルのゲートに第1電圧よりも大きい第2電圧を印加することによりメモリセルの閾値電圧を正方向に移動させる動作である。第2プログラム動作は、メモリセルのボディをフローティングにし且つメモリセルのゲートに正の第3電圧を印加する動作である。

(もっと読む)

メモリ用シフトレジスタ及びその製造方法

【課題】大容量で、信頼性が高く、少ない工程数で製造可能なメモリ用シフトレジスタを提供する。

【解決手段】一の実施形態によれば、メモリ用シフトレジスタは、基板の主面に平行な第1方向に延び、前記第1方向に垂直な第2方向に向かい合う第1及び第2の制御電極を備える。さらに、前記レジスタは、前記第1及び第2の制御電極間において、前記第1の制御電極側に一列に設けられた複数の第1の浮遊電極を備える。さらに、前記レジスタは、前記第1及び第2の制御電極間において、前記第2の制御電極側に一列に設けられた複数の第2の浮遊電極を備える。さらに、前記第1及び第2の浮遊電極の各々は、前記第1方向に垂直な平面に対し、鏡面非対称な平面形状を有する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】制御ゲートの低抵抗化を図ることができる半導体記憶装置及びその製造方法を提供することである。

【解決手段】実施形態に係る半導体記憶装置は、シリコンを含む基板と、前記基板上に形成され、浮遊ゲートと、前記浮遊ゲート上に形成されたゲート間絶縁膜と、前記ゲート間絶縁膜上に形成された制御ゲートと、を有した複数のメモリセルと、を備えている。そして、前記制御ゲートは、前記制御ゲートの上層に形成されニッケルシリサイドを含む上層部と、前記上層部の下方に形成されポリシリコンを含む下層部と、前記上層部と前記下層部との間に形成されヒ素およびアンチモンの少なくともいずれかを偏析させた偏析部と、を有している。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高集積化に適した不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1乃至第3のフィン型積層構造Fin1〜Fin3を有する。第1乃至第3のフィン型積層構造Fin1〜Fin3は、第1の方向に積み重ねられる第1及び第2の半導体層Sm1,Sm2を備える。第1及び第2のアシストゲート電極AG1,AG2は、第3の方向に並んで配置され、第3のフィン型積層構造Fin3の第1の方向にある表面上で互いに分断される。第1のアシストゲートトランジスタAGT1は、第1及び第3のフィン型積層構造Fin1,Fin3内に形成され、第2のアシストゲートトランジスタAGT2は、第2及び第3のフィン型積層構造Fin2,Fin3内に形成される。

(もっと読む)

不揮発性半導体記憶装置

【課題】選択ゲートトランジスタのゲート電極間の間隔の縮小を実現する不揮発性半導体記憶装置を提供する。

【解決手段】実施の形態の不揮発性半導体記憶装置は、半導体基板と、第1の方向に伸長する複数の第1の素子領域と、第1の素子領域を互いに分離する第1の素子分離領域と、第1の方向に伸長する複数の第2の素子領域と、第2の素子領域を互いに分離する第2の素子分離領域と、第1の素子領域と第2の素子領域との間に設けられ、第1および第2の素子領域に接続され、第1の方向と直交する第2の方向に伸長する第3の素子領域と、第1および第3の素子領域上にまたがり、第2の方向に伸長する第1の選択ゲート電極と、第2および第3の素子領域上にまたがり、第1の選択ゲート電極に隣接して平行に配置される第2の選択ゲート電極と、第1および第2の選択ゲート電極間の第3の素子領域に接続されるコンタクト電極を有する。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】SiN膜等の犠牲膜の残存を防止する。

【解決手段】一の実施形態による不揮発性半導体記憶装置の製造方法では、基板上に、複数のメモリセルトランジスタと、複数の選択トランジスタとを形成する。さらに、前記方法では、前記メモリセルトランジスタ間と、前記メモリセルトランジスタと前記選択トランジスタとの間と、前記選択トランジスタ間に、第1から第5の絶縁膜を順に埋め込む。さらに、前記方法では、前記選択トランジスタ間の前記第2及び第4の絶縁膜が一部残存するように、第1のエッチング処理により、前記第2及び第4の絶縁膜を除去する。さらに、前記方法では、前記選択トランジスタ間に残存した前記第2及び第4の絶縁膜を、前記第1のエッチング処理後に行う第2のエッチング処理により除去する。

(もっと読む)

181 - 190 / 4,374

[ Back to top ]