国際特許分類[H01L29/788]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体装置の型 (42,689) | 整流,増幅またはスイッチされる電流を流さない電極に電流のみまたは電位のみを与えることにより制御できるもの (37,192) | ユニポーラ装置 (34,588) | 電界効果トランジスタ (34,488) | 絶縁ゲートによって生じる電界効果を有するもの (29,475) | 浮遊ゲートを有するもの (4,374)

国際特許分類[H01L29/788]に分類される特許

201 - 210 / 4,374

半導体装置

【課題】良好な特性を維持しつつ微細化を達成した半導体装置の提供と、さらに、これらの微細化を達成した半導体装置の良好な特性を維持しつつ、3次元高集積化を図る。

【解決手段】絶縁層中に埋め込まれた配線と、絶縁層上の酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極及びドレイン電極と、酸化物半導体層と重畳して設けられたゲート電極と、酸化物半導体層と、ゲート電極との間に設けられたゲート絶縁層と、を有し、絶縁層は、配線の上面の一部を露出するように形成され、配線は、その上面の一部が絶縁層の表面の一部より高い位置に存在し、且つ、絶縁層から露出した領域において、ソース電極またはドレイン電極と電気的に接続し、絶縁層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根粗さが1nm以下である半導体装置である。

(もっと読む)

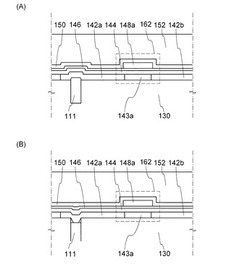

半導体記憶装置

【課題】制御ゲート電極と浮遊ゲート電極との間のカップリングを確保しつつ、浮遊ゲート電極間の干渉を抑制することができる半導体記憶装置を提供する。

【解決手段】アクティブエリア12上に設けられたトンネル膜13と、前記トンネル膜上に設けられた浮遊ゲート電極14と、前記浮遊ゲート電極上に設けられ、前記第1方向に対して交差した第2方向に延びる電極間絶縁膜18と、制御ゲート電極19と、前記第2方向において隣り合う前記アクティブエリア間、前記トンネル膜間及び前記浮遊ゲート電極間に設けられた下側絶縁部16と、前記下側絶縁部と前記電極間絶縁膜との間に設けられ、上面が前記浮遊ゲート電極の上面よりも上方に位置している上側絶縁部17と、を備える。前記下側絶縁部は気体部分を有する。そして、前記上側絶縁部の比誘電率は前記下側絶縁部の比誘電率よりも高く、前記電極間絶縁膜の比誘電率は前記上側絶縁部の比誘電率よりも高い。

(もっと読む)

半導体装置及びその製造方法

【課題】積層構造物の傾きまたは崩壊を防止するのに適する半導体装置及びその製造方法を提供する。

【解決手段】パイプゲート内に埋め込まれたパイプチャンネル及びパイプチャンネルと繋がれた一対のドレインサイドチャンネル、及びソースサイドチャンネルを含むチャンネルを含むメモリブロックと、隣合うメモリブロックの間に位置された第1スリットと、一対のソースサイドチャンネルとドレインサイドチャンネルの間に位置された第2スリットと、を含む。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供する。

【解決手段】酸化物絶縁膜上に、半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてバンドギャップの異なる少なくとも2層の酸化物半導体層を含む酸化物半導体積層を用いる。酸化物半導体積層には、酸素又は/及びドーパントを導入してもよい。

(もっと読む)

半導体装置の作製方法

【課題】トランジスタの微細化を達成し、電界緩和がなされた、酸化物半導体を用いた半導体装置を提供することを課題の一とする。

【解決手段】ゲート電極の線幅を微細化し、ソース電極層とドレイン電極層の間隔を短縮する。ゲート電極をマスクとして自己整合的に希ガスを添加し、チャネル形成領域に接する低抵抗領域を酸化物半導体層に設けることができるため、ゲート電極の幅、即ちゲート配線の線幅を小さく加工しても位置精度よく低抵抗領域を設けることができ、トランジスタの微細化を実現できる。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】選択ゲートトランジスタのゲート電極間の間隔の縮小を実現する不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】実施の形態の不揮発性半導体記憶装置の製造方法は、半導体基板に、複数の第1の素子領域と、素子分離領域と、第2の素子領域を形成する。第1の素子領域上に、メモリセルゲート電極、2本の選択ゲート電極を形成し、第2の素子領域に周辺ゲート電極を形成する。第1の絶縁膜を形成し、周辺ゲート電極の側壁部上が開口される第1のレジストパターンを形成し、第1のエッチング処理を行い、側壁絶縁膜を形成する。第2のレジストパターンを形成し、第2のエッチング処理を行い、選択ゲート電極側壁部の第1の絶縁膜を除去する。第2の絶縁膜を堆積し、第3の絶縁膜を堆積する。2本の選択ゲート電極間上が開口される第3のレジストパターンを形成し、第3のエッチングおよび第4のエッチング処理を行い、コンタクトホールを形成する。

(もっと読む)

半導体メモリ装置

【課題】酸化物半導体のようなバンドギャップが大きな半導体を用いたメモリ装置の保持特性を高める。

【解決手段】ビット線の一端にバックゲートを有するトランジスタ(バックゲートトランジスタ)を直列に挿入し、そのバックゲートの電位は常に十分な負の値となるようにする。また、ビット線の最低電位はワード線の最低電位よりも高くなるようにする。電源が切れた際には、ビット線はバックゲートトランジスタによって遮断され、ビット線に蓄積された電荷が流出することが十分に抑制される。この際、セルトランジスタのゲートの電位は0Vであり、一方で、そのソースやドレイン(ビット線)の電位は、ゲートよりも十分に高いので、セルトランジスタは十分なオフ状態であり、データを保持できる。

(もっと読む)

半導体装置の作製方法

【課題】信頼性の高い半導体装置及び、信頼性の高い半導体装置の作製方法を提供する。また、消費電力が低い半導体装置及び消費電力が低い半導体装置の作製方法を提供する。また、量産性の高い半導体装置及び量産性の高い半導体装置の作製方法を提供する。

【解決手段】酸素欠損を生じることなく酸化物半導体層に残留する不純物を除去し、酸化物半導体層を極めて高い純度にまで精製して使用すればよい。具体的には、酸化物半導体層に酸素を添加した後に加熱処理を施し、不純物を除去して使用すればよい。特に酸素の添加方法としては、高エネルギーの酸素をイオン注入法またはイオンドーピング法などを用いて添加する方法が好ましい。

(もっと読む)

半導体装置の作製方法

【課題】高いオン特性を有する酸化物半導体を用いたトランジスタを提供する。高速応答及び高速駆動の可能なトランジスタを有する高性能の半導体装置を提供する。

【解決手段】チャネル形成領域を含む酸化物半導体膜を有するトランジスタの作製工程において、該酸化物半導体膜に、金属元素を含む膜と接した状態で加熱処理することにより導入された金属元素と、注入法により該金属元素を含む膜を通過して導入されたドーパントとを含む低抵抗領域を形成する。低抵抗領域はチャネル長方向においてチャネル形成領域を挟んで形成する。

(もっと読む)

半導体装置

【課題】浮遊状態の配線と洗浄水との間において高い密度で電荷が移動することに起因する配線の高抵抗化を防ぐ。

【解決手段】半導体製造装置の製造工程中において、半導体基板1Sなどと絶縁された浮遊状態となる銅配線である第1層配線L1の上面に、電気的に機能する接続ビアPL2と電気的に機能しないダミービアDP2とを接続させて形成する。これにより、第1層配線L1の上面に接続ビアPL2を形成するためのビアホールを形成した後の洗浄工程中に、第1層配線L1に溜まった電荷が洗浄水中に移動する際、前記電荷をダミービアDP2形成用のビアホールにも分散させることで、接続ビアPL2形成用のビアホールの底部のみに前記電荷が集中することを防ぐ。

(もっと読む)

201 - 210 / 4,374

[ Back to top ]