国際特許分類[H01L45/00]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 電位障壁または表面障壁をもたず,整流,増幅,発振またはスイッチングに特に適用される固体装置,例.誘電体三極素子;オブシンスキー効果装置;それらの装置またはその部品の製造または処理に特に適用される方法または装置 (1,392)

国際特許分類[H01L45/00]の下位に属する分類

固体進行波装置

国際特許分類[H01L45/00]に分類される特許

1,311 - 1,320 / 1,392

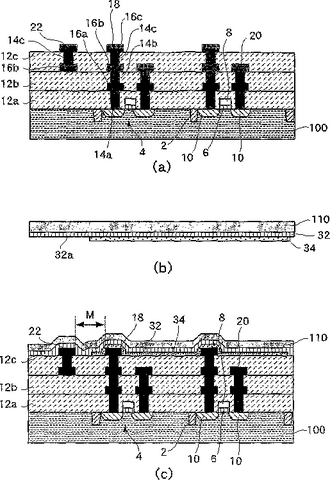

不揮発性メモリおよびその製造方法

第1の基板(100)と、第2の基板(110)とを備え、第1の基板(100)は、マトリクス状に配置された複数のスイッチング素子(4)と、各スイッチング素子(4)に電気的に接続された複数の第1の電極(18)とを有し、第2の基板(110)は、導電膜(32)と、電気的パルスが印加されることにより抵抗値が変化する記録層(34)とを有しており、

複数の第1の電極(18)は、記録層(34)により一体的に覆われており、これによって、複数の第1の電極(18)と導電膜(32)との間に記録層(34)が挟持され、第1の基板(100)は、第2の電極(22)をさらに備え、第2の電極(22)は、導電膜(32)と電気的に接続され、記録層(34)への通電時に一定電圧に保持される不揮発性メモリである。この不揮発性メモリによれば、高集積度を低コストで実現することができる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 カルコゲナイド膜の剥離を有効に防止し、かつ、隣接するビット情報の位置でディスターブの影響を抑圧可能な信頼性の高い半導体装置を提供する。

【解決手段】 本発明の半導体装置は、半導体基板10上に前記相変化材料と良好な接着性を有する絶縁材料を用いて堆積された絶縁膜25と、絶縁膜25におけるビット情報毎に分離された領域に設けたホール内にカルコゲナイド系の相変化材料を埋め込んで形成されたカルコゲナイド膜26と、各々のカルコゲナイド膜26からなる相変化素子に電流を供給するための電極構造23、24、27とを備えている。これにより、カルコゲナイド膜26の剥離を防止し、かつ隣接するビット情報の位置のカルコゲナイド膜26の間でディスターブを抑圧することができる。

(もっと読む)

スイッチング素子と線路切り換え装置及び論理回路

【課題】 クロスバー回路等に用いられ、消費電力の低減及び小型化をはかる。

【解決手段】 ON/OFFを切り替えるためのスイッチング素子であって、基板上に相互に離間して配置された一対の電極21,22と、これらの電極21,22にそれぞれ接して設けられ、加熱履歴によって抵抗値が変化する相変化膜23と、相変化膜を加熱する加熱機構25とを備えた。

(もっと読む)

半導体装置

【課題】不揮発性であって、作製が簡単であり、追記が可能な記憶回路を有する半導体装置の提供を課題とする。

【解決手段】本発明の半導体装置は、複数のトランジスタと、前記トランジスタのソース配線又はドレイン配線として機能する導電層と、前記複数のトランジスタのうちの1つの上に設けられた記憶素子及びアンテナとして機能する導電層とを有し、前記記憶素子は、第1の導電層と、有機化合物層又は相変化層と、第2の導電層とが順に積層された素子であり、アンテナとして機能する前記導電層と前記複数のトランジスタのソース配線又はドレイン配線として機能する導電層とは、同じ層上に設けられていることを特徴とする。

(もっと読む)

相変化ナノ粒子を含む相変化物質層を備える相変化メモリ素子及びその製造方法

【課題】相変化ナノ粒子を含む相変化物質層を備える相変化メモリ素子及びその製造方法を提供する。

【解決手段】相互に対向配置される第1電極40及び第2電極48と、第1電極と第2電極との間に介在されるものであって、相変化ナノ粒子を含む相変化物質層46と、第1電極に電気的に連結されるスイッチング素子30と、を備える相変化メモリ素子である。

(もっと読む)

相変化記憶セル及びその製造方法

【課題】相変化記憶セル及びその製造方法を提供する。

【解決手段】相変化記憶セルは半導体基板上に形成された下部層間絶縁膜及び前記下部層間絶縁膜を貫通する下部導電性プラグを具備する。前記下部導電性プラグは前記下部層間絶縁膜上に提供された相変化物質パターンと接触する。前記相変化物質パターン及び前記下部層間絶縁膜は上部層間絶縁膜で覆われている。前記相変化物質パターンは前記上部層間絶縁膜を貫通するプレートラインコンタクトホール内の導電膜パターンと直接接触する。前記相変化記憶セルの製造方法も提供される。

(もっと読む)

急激な金属−絶縁体転移素子及びその製造方法

【課題】急激な金属−絶縁体転移素子及びその製造方法を提供する。

【解決手段】急激な金属−絶縁体転移素子の電極をNi(またはCr)/In/Mo(またはW)/Auの積層膜で構成する。Ni(またはCr)/Inは、低抵抗コンタクトのためなものであり、熱処理過程時に界面反応により形成される化合物を利用して、急激な金属−絶縁体転移物質膜と電極との間のポテンシャルバリアを低くして電流流入効率を増大させる。そして、高出力素子動作時、高温動作時にも熱的に安定化させる役割を行う。Mo(またはW)はInとAuとの間に導入されて素子高温動作過程でAuの熱拡散によるオーミック特性抵抗を防止する。  (もっと読む)

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】 本発明の課題は、カルコゲナイド膜を用いた相変化メモリ半導体集積回路装置において、相変化温度が低いため長期間記憶保持を保証可能な動作温度が低いという問題と同時に抵抗が低いためメモリ情報書き換えに大電流を要するため装置の消費電力が高いという問題を解決することにある。

【解決手段】 カルコゲナイドの構成元素の一部を窒化物、酸化物あるいは炭化物にするとともに、これらをカルコゲナイド膜と下地電極である金属プラグ界面およびカルコゲナイド結晶の粒界に形成せしめることにより相変化温度を上昇させるとともに該膜の抵抗を高くすることにより低電流でも高いジュール熱を発生可能とすることにより書き換えに要する電力を低減する。

(もっと読む)

チャンネルの物性が印加電圧によって可変的なトランジスタとその製造及び動作方法

【課題】チャンネルの物性が印加電圧によって可変的なトランジスタとその製造及び動作方法を提供する。

【解決手段】基板40上にライン状に備えられた第1導電層42と、第1導電層42上に順次に積層された相変化層44及び第2導電層46と、第2導電層46上に離隔形成された第1及び第2電流方向制限手段48、49と、第1及び第2電流方向制限手段48、49上に各々形成された第3及び第4導電層50、52と、第3導電層50に連結されたワードライン60と、第4導電層52に連結されたビットライン56と、ワードライン60に連結された電圧降下手段Rと、を備えることを特徴とするトランジスタである。

(もっと読む)

不揮発性メモリ

不揮発性メモリ(50)を開示する。第2電極(56)が設けられる。第1電極(51)も設けられる。抵抗値が可変の複数の相変化セル(54)を有する記録層が第1電極(51)及び第2電極(56)間に設けられる。記録層と第1電極の各々に隣接して不均一トンネルバリヤ(540)が設けられる。使用中、第1電極が不均一トンネルバリヤと通電し、第1電極が不均一トンネルバリヤを経て第2電極と通電する。  (もっと読む)

(もっと読む)

1,311 - 1,320 / 1,392

[ Back to top ]