国際特許分類[H01L45/00]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 電位障壁または表面障壁をもたず,整流,増幅,発振またはスイッチングに特に適用される固体装置,例.誘電体三極素子;オブシンスキー効果装置;それらの装置またはその部品の製造または処理に特に適用される方法または装置 (1,392)

国際特許分類[H01L45/00]の下位に属する分類

固体進行波装置

国際特許分類[H01L45/00]に分類される特許

1,321 - 1,330 / 1,392

半導体メモリおよびその製造方法

【課題】相変化メモリは結晶状態で使い始める必要が有るが、基板加熱製膜では表面が荒れずに製膜できる基板温度が100℃付近の狭い温度範囲に限られ、マージンが無い。製膜後のプロセスで加熱されることによる結晶化では結晶粒径が大きくなって接着性が低下し、洗浄工程などで剥離の可能性が大きい。また、結晶粒径が下部電極サイズと同程度またはそれより大きく特性バラツキの原因になる。また、結晶形がメモリ書き換え時の結晶形と大きく異なり、1回目からの安定な書換えができない。

【解決手段】上記目的を達成するため、膜の両側の電極のうちの、相変化膜との接触領域の最大幅が小さい方の電極の接触領域最大幅よりも結晶粒の膜面に平行な断面での平均幅が小さい相変化膜とする。初期結晶化後の400℃のプロセスで結晶形が大きく変化しないようカルコゲナイド相変化膜の組成と組合せる。初期結晶化時に表面を薄い電極材料層や絶縁物層で保護する。

(もっと読む)

2成分系金属酸化膜をデータ保存物質膜として採用する交差点不揮発性記憶素子及びその製造方法

【課題】2成分系金属酸化膜をデータ保存物質膜として採用する交差点不揮発性記憶素子及びその製造方法を提供する。

【解決手段】基板内に複数の平行なドーピングラインが配置される。複数の平行な上部電極が前記ドーピングラインと重畳される部分に交差点を形成するように前記ドーピングラインの上部を横切る。前記ドーピングラインと前記上部電極の間の前記交差点に複数の下部電極が位置する。データ保存物質膜として提供される2成分系金属酸化膜が前記上部電極と前記下部電極との間に介在している。前記ドーピングラインとともにダイオードを構成し、前記ドーピングラインと反対の導電型を有するドーピング領域が前記下部電極及び前記ドーピングラインの間に介在している。前記不揮発性記憶素子を製造する方法も提供する。

(もっと読む)

抵抗性メモリ素子およびその製造方法

【課題】探針アレイを有する抵抗性メモリ素子およびその製造方法を提供する。

【解決手段】本発明の抵抗性メモリ素子は、第1基板101および第2基板300と、前記第1基板101上に形成された底電極層100および強誘電層200を備えるメモリ部10と、前記第2基板300上に固定され、前記強誘電層200と対向するようにチップ部分が設けられた、前記強誘電層200へのデータ記録および再生のための抵抗性探針400を備える探針部20と、前記抵抗性探針400を前記強誘電層200上につかんで固定させる結合層500と、を備える構成とした。

(もっと読む)

多様な抵抗状態を呈する抵抗体を利用した不揮発性メモリ素子、及び、その駆動方法

【課題】簡単な構造を有し、低電力駆動及び高速の動作が可能で、かつ1つの抵抗体及び1つのスイッチを備えた不揮発性半導体メモリ素子、及び、その駆動方法を提供する。

【解決手段】本発明の不揮発性半導体メモリ素子は、スイッチング構造体と、前記スイッチング構造体と電気的に接続され、1つのリセット抵抗状態及び少なくとも2つ以上のセット抵抗状態を呈する抵抗体(12)と、を備えることを特徴とする。更に、本発明の不揮発性半導体メモリ素子の駆動方法は、前記抵抗体(12)の抵抗状態がリセット抵抗状態からセット抵抗状態に変化する途中に、前記抵抗体(12)に流れる電流値を調節することにより、前記抵抗体(12)の抵抗状態を制御するステップを含むことを特徴とする。

(もっと読む)

レーザ結晶化装置

【課題】相変化不揮発性メモリセル用の相変化材料に関し、素子作成プロセス中に前記相変化材料近傍において剥離などの破壊を生じさせない初期結晶化を行い、書き換えの初期から特性を安定させる結晶化装置を提供する。

【解決手段】 大出力レーザによる加熱結晶化を行う。シリコンウェハ8の搬送は、1方向の搬送を基本とする。その搬送方向に垂直な方向にレーザヘッド6を往復運動させてレーザ照射する。回転運動を加えてもよい。ウェハ受け9周辺部にウェハを位置決めする立ち上がり部分が有り、その一部に横からウェハを持ち上げる操作部が入る切り欠きを持つ。レーザスポット面積と照射時間を所定の範囲内とする。装置の一部が真空製膜装置の中にあってもよい。

(もっと読む)

不揮発性メモリ素子、不揮発性メモリ素子アレイ、及び不揮発性メモリ素子アレイの動作方法

【課題】簡単に製造することができ、低電力での駆動と高速動作が可能な不揮発性メモリ素子を提供する。

【解決手段】トランジスタ構造体と、前記トランジスタ構造体の第1不純物領域及び第2不純物領域とそれぞれ電気的に接続されると共に、印加される電圧に応じて異なる抵抗値特性を示す抵抗層とを備えた不揮発性メモリ素子であって、

前記トランジスタ構造体は、基板上に互いに所定間隔離隔させた状態で形成された第1不純物領域及び第2不純物領域と、前記基板上に設けられており、前記第1不純物領域と前記第2不純物領域とに接続されたゲート絶縁層と、前記ゲート絶縁層上に形成されたゲート電極層とを備えている。

(もっと読む)

他の素子の処理の間のメモリセルの活性層の保護

導電層(102)を設け、その導電層(102)を覆うように誘電体(100)を設け、その誘電体(100)を貫通する第1および第2の開口(104,106)を設け、第1および第2の開口(104,106)内にそれぞれ第1および第2の導電体(108,110)を設けかつ第1および第2の導電体(108,110)を導電層(102)に接触させ、その第1の導電体(108)を覆うようにメモリ構造(126)を設け、そのメモリ構造(126)を覆うように保護要素(134)を設け、その第2の導電体(110)上に処理を施すことによる電子構造の製造方法。  (もっと読む)

(もっと読む)

半導体メモリ装置とそのプログラミング方法

【課題】一つの選択トランジスタ及び8の倍数から構成された相変化可変抵抗素子から形成されたメモリセルを備える半導体メモリ装置の構造と、そのプログラミング方法とを提供する。

【解決手段】相変化メモリセルは、それぞれ、一端が対応するビットラインに連結され、他端が共通で選択トランジスタのドレインに連結され、8の倍数から構成された複数の相変化可変抵抗素子と、ゲートが対応するワードラインに連結され、ソースが基準電圧に連結された選択トランジスタと、を備える複数の相変化メモリセルを備える半導体メモリ装置である。これにより、半導体メモリ装置は、一つのメモリセルが8の倍数個の相変化可変抵抗素子を備えることにより、半導体装置の集積度を高めうる。

(もっと読む)

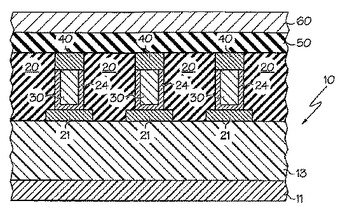

カルコゲニド型メモリ・デバイスのための金属キャップの無電解メッキ

カルコゲニド型メモリ・デバイスにおいて導電性相互接続部の上側に金属キャップを形成する方法が提供され、該方法は、基板10の上側に第1導電性材料の層21を形成する工程と、基板及び第1導電性材料の上側に絶縁層20を堆積させる工程と、絶縁層に開口22を形成して、第1導電性材料の少なくとも一部分を露出させる工程と、絶縁層の上側に且つ開口内に第2導電性材料30を堆積させる工程と、第2導電性材料を部分的に除去して開口内に導電性区域を形成する工程と、開口内の導電性区域を絶縁層の上面よりも低い高さまで凹ます工程と、開口内の凹まされた導電性区域の上側に第3導電性材料のキャップ40を形成する工程と、キャップの上側にカルコゲニド型メモリ・セル材料のスタックを堆積させる工程と、カルコゲニド型メモリ・セル材料のスタックの上側に導電性材料を堆積させる工程とを備え、第3導電性材料は、コバルト、銀、金、銅、ニッケル、パラジウム、白金、及びそれらの合金の群の中から選択される。  (もっと読む)

(もっと読む)

半導体装置

【課題】非晶質化のために必要な電流(リセット電流)を低減した相変化メモリを提供する。

【解決手段】相変化膜で構成されるメモリセル30と、メモリセル30の下主面にその一端が直接に接続され、他端がMOSトランジスタ10の一方のソース・ドレイン層3に接続されて、当該ソース・ドレイン層3とメモリセル30とを電気的に接続するとともに、メモリセル30の下部電極となるプラグ電極CP1と、メモリセル30の上主面にその一端が直接に接続され、他端がメモリセル30を覆うように配設された層間絶縁膜9上に配設されたビット配線層WRに接続されて、当該ビット配線層WRとメモリセル30とを電気的に接続するとともに、メモリセル30の上部電極となるプラグ電極CP10とを備えている。

(もっと読む)

1,321 - 1,330 / 1,392

[ Back to top ]