国際特許分類[H01L45/00]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 電位障壁または表面障壁をもたず,整流,増幅,発振またはスイッチングに特に適用される固体装置,例.誘電体三極素子;オブシンスキー効果装置;それらの装置またはその部品の製造または処理に特に適用される方法または装置 (1,392)

国際特許分類[H01L45/00]の下位に属する分類

固体進行波装置

国際特許分類[H01L45/00]に分類される特許

1,331 - 1,340 / 1,392

相変化メモリ

【課題】

本発明の第一の目的は、信頼性の高い相変化メモリを提供することにある。また、本発明の第二の目的は、書換え繰返し耐性の高い相変化メモリを提供することにある。

【解決手段】

基板の一主面側に形成された相変化記録膜を含む相変化メモリにおいて、相変化記録膜のアモルファス相の原子配列と同様の原子配列を持つアモルファス材料を相変化記録膜に接触させ、なおかつ相変化記録膜に引張りひずみを与える。

(もっと読む)

調整可能なエネルギバンドギャップを有する半導体装置

本発明は、エネルギバンドギャップが可逆的に変化されることができる半導体装置に関する。本発明の発想は、例えば、相変化材料307のような、適切にアドレス指定された場合に体積の可逆的変化を呈する材料307と機械的に接触状態にある半導体材料306に基づく装置を提供することにある。前記装置は、例えば、発光、スイッチ及びメモリの用途において実施されることができる。前記半導体材料は、前記相変化材料に局所的な体積の変化を生じさせることにより、可逆的に歪まされることができる。前記半導体材料の得られるバンドギャップの変化は、例えばLED又はレーザから、発せられる光の色を調整するのに利用されることができる。他の分野の用途においては、半導体接合における接触抵抗が制御されることができ、このフィーチャは、メモリ及びスイッチにおいて非常に有利である。  (もっと読む)

(もっと読む)

相変化メモリ装置

相変化メモリ装置は、半導体基板と、前記半導体基板上に積層形成された、それぞれ相変化により決まる抵抗値をデータとして記憶するマトリクス配列された複数のメモリセル、マトリクスの第1の方向に並ぶ複数のメモリセルの一端を共通接続するビット線及びマトリクスの第2の方向に並ぶ複数のメモリセルの他端を共通接続するワード線を有する複数のセルアレイと、前記半導体基板の前記セルアレイの下に位置するように形成された、前記セルアレイのデータの読み出し及び書き込みを行うための読み出し/書き込み回路と、前記セルアレイが積層されるセル配置領域を区画する前記第1の方向の第1及び第2の境界に沿ってそれぞれ配置されて、隣接する2セルアレイのビット線をそれぞれ前記読み出し/書き込み回路に接続する第1及び第2の垂直配線と、前記セル配置領域を区画する前記第2の方向の第3及び第4の境界の一方に沿って配置されて、前記各セルアレイのワード線を前記読み出し/書き込み回路に接続する第3の垂直配線と、を有する。  (もっと読む)

(もっと読む)

マルチレベル相変化メモリ、及びその動作方法並びに製造方法

【課題】 新規相変化メモリ構造を提供する。

【解決手段】 マルチレベル相変化メモリ、及びその動作方法と製造方法である。相変化メモリは、2個の相変化層と電極を含み、メモリセルを形成するために並列構造で構成される。電圧駆動モードは、マルチレベルメモリ状態が異なる電圧レベルを印加することによって達成され得るようにメモリを制御及び駆動するために使用される。他の実施の形態は、2個の相変化層と電極を含み、メモリセルを形成するように直列構造に構成される。電流駆動モードは、マルチレベルメモリ状態が異なる電流レベルを印加することによって達成され得るようにメモリを制御及び駆動するために使用される。提供されたマルチレベル相変化メモリは、単一相変化層を有するメモリよりも多くのビット及びより高い容量を有する。更に、直列構造は、セル面積及びデバイスの大きさを減少する。

(もっと読む)

プログラム可能な不揮発性抵抗切り替えデバイス

【課題】 複数の抵抗状態の間で可逆的に切り替えることができるメモリ素子を含むデバイスのような超小型電子デバイスを提供する。

【解決手段】 メモリ素子は、第1の数の電極と、2電極のサブグループ間の第2の数の導電性チャネルとを含み、チャネルは、異なる状態間で可逆的に切り替え可能な電気抵抗を呈し、前記第1の数は2より大きく、前記第2の数は前記第1の数を2で割った数より多い。導電性チャネルは、遷移金属酸化物材料において与えられ、それは、電極と遷移金属酸化物材料との間の界面における切り替え現象に起因する可逆的に切り替え可能な抵抗を呈する。

(もっと読む)

抵抗スイッチング半導体メモリー

本発明の目的は、CBRAMメモリーセルを有し、上記CBRAMメモリーセルが、AgドープされたGeSe層とAGトップ電極との間に、化学的に不活性な境界層を有し、上記境界層が、CBRAMメモリーセルの切り替え特性を改善する不揮発性半導体メモリーを提供することである。この目的は、本発明に基づいて、メモリーセルを活性マトリックス材料層が、ガラス状のGeSe層とアモルフGe:H層とを有するGeSe/Ge:H二重層を備え、アモルフGe:H層が、GeSe層と第2電極との間に配置されていることによって達成される。その結果、Agドーピング層および/または電極層におけるAgSe塊の形成が抑制される。その結果、堆積が防止され、銀ドーピング層を均一に堆積できる。GeSe/Ge:H二重層組織により、一方ではCBRAMメモリーセルの抵抗不揮発性メモリー作用が得られ、他方では、薄いGe:H層を用いて、薄いGe:H層上に設けられる上部電極の化学的安定性が保証される。  (もっと読む)

(もっと読む)

相変化材料を有する電子デバイスおよびその製造方法

電子デバイス(100)は、第1相と第2相の間で変化することが可能な相変化材料を備える抵抗器(107)を有するボディ(102)を持つ。抵抗器(107)は、相変化材料が第1相にあるときは第1電気抵抗を、相変化材料が第2相にあるときは、第1電気抵抗とは異なる第2電気抵抗を、有する。相変化材料は、第1接触エリアと第2接触エリアの間の導電パスを構成する。導電パスの断面は、第1接触エリア(124)および第2接触エリア(132)よりも小さい。ボディ(102)は、第1相から第2相への遷移を可能にする電流を伝えることができる発熱体(106)を、さらに有してもよい。発熱体(106)は、好ましくは抵抗器(107)と並列して配置される。  (もっと読む)

(もっと読む)

相変化材料を有するナノワイヤを有する電気デバイス

本発明の方法は、本発明の電気デバイス(100)の製造方法に関する。当該電気デバイス(100)は、抵抗器を有する主部(102)を有する。その抵抗器は、第1相と第2相との間で変化可能な相変化材料を有する。その抵抗器は、その相変化材料が第1相のときに、第1電気抵抗を有し、その相変化材料が第2相のときに、第1電気抵抗とは異なる第2電気抵抗を有する。その抵抗器は、第1導体(172,120)及び第2導体(108,121)と電気的に接続するナノワイヤ(NW)である。本発明の方法は、第1導体(172,120)を有する主部(102)を供する工程、第1導体(172,120)にナノワイヤ(NW)を供することで、前記ナノワイヤ(NW)と前記第1導体(172,120)とを電気的に接続する工程、及び前記ナノワイヤ(NW)に第2導体(108,121)を供することで、前記ナノワイヤ(NW)と前記第2導体(108,121)とを電気的に接続する工程、を有する。  (もっと読む)

(もっと読む)

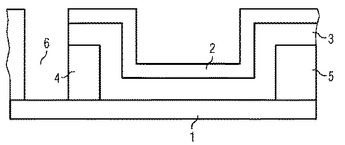

相変化材料および並列ヒータを有する電子デバイス

電子デバイス(1,100)は、第1相と第2相の間で変化することが可能な相変化材料を備える抵抗器(7,107)を有するボディ(2,102)を持つ。抵抗器(7,107)は、相変化材料が第1相にあるときは第1電気抵抗を、相変化材料が第2相にあるときは、第1電気抵抗とは異なる第2電気抵抗を有する。ボディ(2,102)は、第1相から第2相への遷移を可能にする電流を伝えることができる発熱体(6,106)を、さらに有する。発熱体(6,106)は、抵抗器(7,107)と並列して配置される。  (もっと読む)

(もっと読む)

相変化材料を備える電子デバイス

電子デバイス(1,100)は、第1相と第2相の間で変化することが可能な相変化材料を備える抵抗器(7,250)を有するボディ(2,101)を持つ。抵抗器(7,250)は、相変化材料が第1相か第2相かに依存する電気抵抗を有する。抵抗器(7,250)は、第1相から第2相への遷移を可能にする電流を伝えることができる。相変化材料は、高速成長材料(fast growth material)であり、式Sb1−cMcの組成物としても良く、ここで、cは、0.05≦c≦0.61を満たし、Mは、Ge、In、Ag、Ga、Te、ZnおよびSnの群から選択された1つまたは複数の元素であり、あるいは、式SbaTebX100−(a+b)の組成物としても良く、ここで、a、bおよび100−(a+b)は、1≦a/b≦8および4≦100−(a+b)≦22を満たす原子百分率を表わし、Xは、Ge、In、Ag、GaおよびZnから選択された1つまたは複数の元素である。  (もっと読む)

(もっと読む)

1,331 - 1,340 / 1,392

[ Back to top ]