国際特許分類[H01L45/00]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 電位障壁または表面障壁をもたず,整流,増幅,発振またはスイッチングに特に適用される固体装置,例.誘電体三極素子;オブシンスキー効果装置;それらの装置またはその部品の製造または処理に特に適用される方法または装置 (1,392)

国際特許分類[H01L45/00]の下位に属する分類

固体進行波装置

国際特許分類[H01L45/00]に分類される特許

1,341 - 1,350 / 1,392

オボニック閾値スイッチを有する相変化メモリ

【課題】 相変化メモリはメモリ要素と選択要素とを有する。

【解決手段】 メモリ要素は誘電体中に埋め込まれ、少なくとも1つのサブリソグラフィック寸法を有する抵抗性要素と抵抗性要素と接触している記憶領域とを有する。選択要素は誘電体中に埋め込まれたカルコゲン材料を有する。カルコゲン材料及び記憶領域は共通のエッチング端部を有するスタックの一部である。

(もっと読む)

電界で分極される材料

本書に記載する発明には、供与体サブユニット(12);受容体サブユニット(16);及び芳香族架橋性サブユニット(20)であって、1つ又は複数の芳香族架橋性サブユニット20を含み且つ受容体サブユニット16を芳香族架橋性サブユニット20に結合するための芳香族架橋性サブユニット(20)、を含んで成る分子スイッチ(10)が包含され、この場合、芳香族架橋性サブユニット20は、低い電界電圧において分子スイッチ10を分極及び脱分極させるように配座する。 (もっと読む)

メモリ及びアクセス装置

本発明の実施の形態によれば、メモリ100が提供される。メモリ100は、メモリ素子130及び該メモリ素子130に結合される第一のアクセス装置120を含んでいる場合がある。第一のアクセス装置120は、第一のカルコゲナイド材料940を有している。メモリ100は、第一のアクセス装置120に結合される第二のアクセス装置125を更に含んでいる場合がある。  (もっと読む)

(もっと読む)

アンチモン前駆体、相変化メモリ素子およびその製造方法

【課題】 リセット/セットプログラミングのための消費電流値を低くし得る相変化物質のアンチモン前駆体、それを利用した相変化メモリ素子およびその製造方法を提供する。

【解決手段】 Ge−Sb−Te相変化膜形成用のアンチモン前駆体において、アンチモン前駆体は、アンチモン、窒素およびシリコンを含むことを特徴とする。また、相変化メモリ素子は、半導体基板20と、半導体基板20に形成された第1不純物領域21aおよび第2不純物領域21bと、第1不純物領域21aと第2不純物領域21bとの間のチャンネル領域上に形成されたゲート構造体と、第2不純物領域21bと連結された下部電極26と、下部電極26上に形成され、窒素およびシリコンが含まれたGe2Sb2Te5物質含む相変化膜27と、相変化膜27上に形成された上部電極28と、を備える。

(もっと読む)

相変化メモリを形成する方法

相変化メモリ(10)は改善された特性を示し、平面的な構成において相変化材料層(14)を形成することにより一部の場合にコストを低減させる。ヒータ(16)は、相変化をもたらす材料(14)を適切に加熱するために相変化材料層(14)の下に備えられる。ヒータ(16)は適切な導体に結合されている。  (もっと読む)

(もっと読む)

積層構造体、磁気記録媒体及びその製造方法、磁気記録装置及び磁気記録方法、並びに、該積層構造体を用いた素子

【課題】 磁気記録媒体をはじめ、不揮発メモリ、巨大磁気抵抗効果素子、スピンバルブ膜、トンネル効果膜、各種センサー、ディスプレイ、光学素子等の各種分野に好適な積層構造体、磁気ヘッドの書込み電流を増やすことなく高密度記録・高速記録が可能で大容量であり、オーバーライト特性に優れ、均一な特性を有し、特に媒体飽和磁化(tBr)・異方性磁界(Hd)に優れた高品質な磁気記録媒体等の提供。

【解決手段】 金属ナノピラーの材料で形成されかつその長さが略一定である複数の金属ナノピラーによって貫通され、絶縁層の材料で形成された絶縁層を複数積層した状態で有してなる積層構造体である。基板上に、前記積層構造体を有してなり、該基板面に対し略直交する方向に、磁性材料で形成された金属ナノピラーが位置している磁気記録体である。

(もっと読む)

垂直積層ポア相変化メモリ

相変化メモリ(10)用の垂直積層ポア構造は、孔部(46)を有し、この孔部の底部には、底部電極(24、26)が設置され、底部電極は、孔部(46)内で相変化材料(18)と接続される。底部電極は、高抵抗底部電極(24)と、高抵抗底部電極(24)の下側にある低抵抗底部電極(26)とで構成される。このためある実施例では、相変化材料(18)のより均一な加熱が可能となり、ある場合には、より好ましい接続が可能となる。  (もっと読む)

(もっと読む)

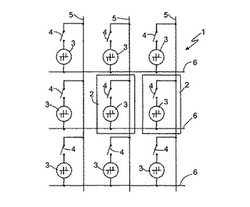

半導体メモリ装置及びリード動作方法

【課題】リード動作の時に漏洩電流を補償することができる相変化メモリ装置を提供する。

【解決手段】ワードラインとビットラインとの交差点に位置する複数個のメモリセルと、ダミービットラインに連結された複数個のダミーセルと、前記ダミービットラインに連結され漏洩補償電流を前記ビットラインに出力する漏洩補償回路と、第1制御信号に応じてリード動作時に必要なリード電流を前記ビットラインに出力する理度電流供給回路と、を備える。

(もっと読む)

分子メモリとそのプロセスシステムおよびプロセス方法

分子メモリ、すなわち、電荷蓄積用分子を組み込んだメモリについて開示した。分子メモリセル、分子メモリアレイ、および分子メモリを含む電子デバイスについても開示した。また、分子メモリ製造のためのプロセスシステムおよびプロセス方法についても同様に開示した。さらに、半導体デバイスおよび相互配線を分子メモリとモノリシックに製造することを可能にする分子メモリ製造方法についても開示した。  (もっと読む)

(もっと読む)

混合原子価導電性酸化物を用いたメモリ

【課題】

【解決手段】混合原子価導電性酸化物を用いたメモリが開示されている。そのメモリは、酸素欠乏状態で導電性が下がる混合原子価導電性酸化物と、酸素に対する電解質であり、酸素イオンの移動を引き起こすのに有効な電場を促進する電解質トンネル障壁と、を備える。

(もっと読む)

1,341 - 1,350 / 1,392

[ Back to top ]