国際特許分類[H01L45/00]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 電位障壁または表面障壁をもたず,整流,増幅,発振またはスイッチングに特に適用される固体装置,例.誘電体三極素子;オブシンスキー効果装置;それらの装置またはその部品の製造または処理に特に適用される方法または装置 (1,392)

国際特許分類[H01L45/00]の下位に属する分類

固体進行波装置

国際特許分類[H01L45/00]に分類される特許

1,381 - 1,390 / 1,392

記憶素子、メモリ回路、半導体集積回路

【解決手段】第1の可変抵抗(5)は、第1の端子(7)と第3の端子(9)との間に接続され、第1の端子(7)と第3の端子(9)との間に印加されるパルス電圧の極性に応じてその抵抗値を増加/減少させる。第2の可変抵抗(6)は、第3の端子(9)と第2の端子(8)との間に接続され、第3の端子(9)と第2の端子(8)との間に印加されるパルス電圧の極性に応じてその抵抗値を増加/減少させる。第1の端子(7)と第3の端子(9)との間および第3の端子(9)と第2の端子(8)との間に所定のパルス電圧を印加して第1および第2の可変抵抗(5,6)の抵抗値を可逆的に変化させることにより1ビットあるいは多ビットの情報を記録する。 (もっと読む)

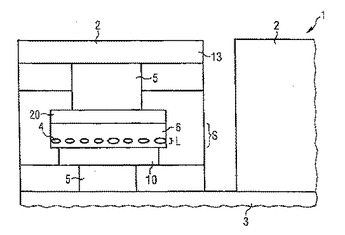

半導体集積メモリーおよび半導体集積メモリーの製造方法

本発明は、2つの電極(10,20)間に配置された記憶媒体(6)を備えた半導体集積メモリー(1)に関する。上記記憶媒体(6)は、例えば相変化媒体であってもよい。記憶媒体(6)は、電流によって第1状態または第2状態に設定される。その結果、情報項目を記憶させることができる。本発明によれば、材料(4)からなる不純物粒子が注入された面(L)が設けられている。その結果、記憶媒体における電流密度が局部的に上昇し、プログラミングのために必要とされるプログラミング電流を低減できる。その結果、相変化媒体を含むメモリー素子の電流消費を低減できる。したがって、相変化媒体を含むメモリー素子を、トランジスタなどの他の部品と共に、最小構造寸法で実施することができ、単一の半導体回路に集積することができ、別個のサブ回路に配置する必要がなくなる。  (もっと読む)

(もっと読む)

スイッチング素子

転移確率を高くしてスイッチング特性を安定化した、双安定特性を持つスイッチング素子を提供する。

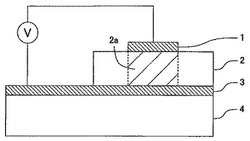

少なくとも2つの電極間に、印加される電圧に対して2種類の安定な抵抗値を持つ有機双安定化合物を含む有機双安定材料層30を配置してなるスイッチング素子であって、基板10上に、第1電極層20a、電荷注入抑制層40、有機双安定材料層30、第2電極層20bの順に薄膜として形成され、電荷注入抑制層40が、第1電極層20aから有機双安定材料層30への電荷注入量を、電荷注入抑制層40を設けずに第1電極層20aから有機双安定材料層30へ直接電荷注入する場合に比べて小さくする導電層からなる。

(もっと読む)

高密度高分子メモリ素子アレイにおけるサイドウォール形成方法

リソグラフィー形状に関連付けて、メモリセルの数を増加させるシステム及び方法が開示されている。システムは、種々の堆積プロセス及びエッチングプロセスを用いることにより、リソグラフィー形状のサイドウォール上に作製されたメモリ素子を備えている。サイドウォールメモリセル(115)はウェハ(806)のビット線(610)を第1の電極(104,1502)として持つことが可能であり、形成された第2の電極(110,1504)とともに、その間に形成された有機物質の一部を作動させるように動作可能である。  (もっと読む)

(もっと読む)

抵抗変化素子、その製造方法、その素子を含むメモリ、およびそのメモリの駆動方法

本発明は、低消費電力、高速メモリとして期待されているRRAMの駆動電圧を低くし、かつ同じ抵抗変化を実現するための電気パルスの幅のバラツキを抑制する。本発明は、第1電極と、第1電極の上に形成され、電気パルスを印加することにより抵抗が変化しうる層と、この層の上に形成された第2電極と、を含み、上記層がペロブスカイト構造を含み、上記層が、第1電極および第2電極から選ばれる少なくとも一方の電極との界面において、凹部および凸部から選ばれる少なくとも一方を有する抵抗変化素子、を提供する。 (もっと読む)

相変化メモリ、相変化メモリアセンブリ、相変化メモリセル、2D相変化メモリセルアレイ、3D相変化メモリセルアレイおよび電子部品

本発明の相変化メモリは、相変化材料から成るメモリ材料層と相互に距離を置いて配置された第1および第2電気接点とを有し、この接点を通って電流信号がメモリ材料層のスイッチングゾーンを横断する。前記電流信号を利用して結晶相とアモルファス相の間の相変化、したがってスイッチングゾーンの相変化材料の抵抗変化を誘発する。本発明の相変化メモリの新しい概念はスイッチングゾーンが第1および第2電気接点の間の相変化メモリの水平方向に沿って配置され、電流信号が前記水平方向に沿ってスイッチングゾーンを通って伝導される。 (もっと読む)

記憶装置用材料及びセル構造

本発明はメモリ用組成物に関し、同組成物と、2つの電極とからなるメモリセルに関する。さらに本発明は、微細電子部品の製造方法及び微細電子部品の製造における本発明の組成物の使用に関する。 (もっと読む)

多重ビット・カルコゲナイド記憶デバイス

多重ビット又は非2進法ビット記憶容量を有する、多端子カルコゲナイド記憶素子、並びにそれをプログラミングする方法。記憶素子は、カルコゲナイド材料の入った空孔領域と、それと電気的に接続している三端子又はそれ以上の電気端子とを共に含んでいる。端子の形状は、多重ビット記憶をさせるため選択的且つ独立してプログラムできるように、カルコゲナイド材料の領域を空間的に明確に区分する。一対の端子間への電気信号(例えば、電流又は電圧パルス)の印加は、カルコゲナイド材料の空間的に区分された部分の一つにおける構造転移をもたらす。カルコゲナイド・デバイス内の別の端子対への電気信号の印加は、カルコゲナイド材料の異なる部分に構造転移をもたらす。構造転移によって生成される構造状態は、2進法又は非2進法(例えば、多値レベル)系における情報値の記憶に用いられる。端子の選択は、カルコゲナイド材料の連続的体積内において特定の区分された部分の、選択的プログラミングをもたらし、選択的にプログラミングされた各部分は、単一2進法又は非2進法ビットの記憶を提供する。三つ又はそれ以上の端子を有するデバイスにおいて、二つ又はそれ以上の選択的にプログラミングできる部分が、空孔領域を占めるカルコゲナイド材料の体積内に存在し、それによって多重ビット記憶が実現される。更に本発明は、2進法又は非2進法系において多重ビット情報を記憶することを目指す、三つ又はそれ以上の端子を有するカルコゲナイド記憶素子のプログラミング方法を含んでいる。  (もっと読む)

(もっと読む)

メモリ用相変化アクセス装置

メモリは、カルコゲナイド材料を用いて形成されたアクセス装置を有する。アクセス装置は、アクセスされた対応メモリ素子の読み出しを妨害するスナップバック電圧を生じない。相変化メモリ素子の場合、スナップバック電圧は、層変化メモリ素子の閾値電圧よりも小さい。  (もっと読む)

(もっと読む)

スイッチング素子

【課題】 転移確率を高くしてスイッチング特性を安定化した、双安定特性を持つスイッチング素子を提供する。

【解決手段】 少なくとも2つの電極間に、印加される電圧に対して2種類の安定な抵抗値を持つ有機双安定化合物を含む有機双安定材料層を配置してなるスイッチング素子であって、基板10上に、第1電極層20a、金属微粒子含有層40、有機双安定材料層30、第2電極層20bの順に薄膜として形成され、金属微粒子含有層40が、金属微粒子と有機双安定化合物とを含む層である。

(もっと読む)

1,381 - 1,390 / 1,392

[ Back to top ]