国際特許分類[H01L45/00]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 電位障壁または表面障壁をもたず,整流,増幅,発振またはスイッチングに特に適用される固体装置,例.誘電体三極素子;オブシンスキー効果装置;それらの装置またはその部品の製造または処理に特に適用される方法または装置 (1,392)

国際特許分類[H01L45/00]の下位に属する分類

固体進行波装置

国際特許分類[H01L45/00]に分類される特許

1,351 - 1,360 / 1,392

小さな接点を有する相変化記憶素子の製造方法

【課題】小さな接点を有する相変化記憶素子の製造方法の提供。

【解決手段】半導体基板上に下部導電体パターン55を形成する段階と、前記下部導電体パターンの上部面を横切って下部導電体パターンの一部領域を露出させる第1絶縁膜パターンを形成する段階と、第1絶縁膜パターンの側壁に下部導電体パターンと電気的に接続される導電性スペーサパターンを形成する段階と、第1層間絶縁膜を形成する段階と、第1層間絶縁膜及び前記導電性スペーサパターンを平坦化して下部電極60を形成する段階と、下部電極上部面を横切って下部電極の一部領域を露出させる第2絶縁膜パターンを形成する段階と、第2絶縁膜パターンの側壁に下部電極と電気的に接続される相変化物質スペーサを形成する段階と、第2層間絶縁膜を形成する段階と、第2層間絶縁膜及び相変化物質スペーサを平坦化して相変化物質パターン70を形成する段階と、を含む。

(もっと読む)

カルコゲニドクラッド法を使用する単一レベルの金属メモリーセル

基板上で第一コンダクタ(140)と第二コンダクタ(315)との間に配置された位相変化物質(290)の容量と、位相変化物質の容量及び第一コンダクタに結合された複数の電極(2300)とを含む装置は、プログラム可能なメモリーデバイスを構成して示される。さらに、基板上の第一コンダクタにわたって第一コンダクタに結合された複数の電極を導入することと、好ましくは、カルコゲニド型の位相変化物質を複数の電極での電気通信において複数の電極にわたって導入することと、及び第二コンダクタを位相変化物質に結合して位相変化物質上に導入することと、を含む作製方法が記載される。  (もっと読む)

(もっと読む)

可変データ保持時間を有するポリマーメモリ

ポリマーメモリセル(102、200)がその内部に記憶されたデータ用の可変保持時間を呈することができるようにするシステムおよび手法が提供される。保持時間のそのような設定は、ポリマーメモリセル(102、200)に採用されたプログラミングモードおよび/または材料のタイプに依存し得る。短い保持時間は、低電流または低電界によってポリマーメモリセル(102、200)をプログラミングすることによって得ることができる。同様に、長い保持時間は、ポリマーメモリセル(102、200)をプログラミングするために高電流または高電界を採用することによって得ることができる。  (もっと読む)

(もっと読む)

ビア構造体の形成方法及びこのようなビア構造体を合併させた相変化記憶素子の製造方法

【課題】多数の導電層パターンからビアプラグのような導電プラグ構造体の形成方法、及び相変化記憶素子の製造方法のような半導体メモリ素子を含む半導体素子の製造方法を提供する。

【解決手段】半導体基板上に導電層を形成してビア構造を形成する方法はモールディング絶縁膜を導電層上に形成する。ビアホールを絶縁膜内に形成して導電層の一部位を露出させる。第1ビア充填膜の形成及び部分的に除去して予備ビアプラグを形成する。本発明は相変化物質膜の形成及び除去を繰り返してマルチ層構造としてビアホールを埋め込むマルチ層プラグ構造を形成することで、通常の方法により形成されるプラグ構造よりも欠陷及びダメージが低減できるメリットがある。

(もっと読む)

ポリマーメモリセルのプログラミングしきい値を調節するためのシステムおよび方法

ポリマーメモリセル(215、640)の動作に関連するしきい値を、作製後の段階中に調整された電界および/または電圧パルス幅をそれに印加することによって調節するためのシステムおよび方法が提供される。プログラミングしきい値のそのようなカスタマイゼーションは通常、回路設計の柔軟性を高めるために、メモリセル(215、640)をプログラミングするどのサイクルででも得ることができる。したがって、この発明は、電流−電圧ドメインおよび/または周波数−時間ドメインの双方を供給して、ポリマーメモリセル(215、640)のプログラムしきい値の調節を容易にする。  (もっと読む)

(もっと読む)

抵抗可変メモリ・ディバイスと製造方法

【構成】抵抗可変メモリ・ディバイスのアグロメレーション防止および温度安定性を実現する方法および装置である。一実施形態によれば,少なくとも1つの錫−カルコゲナイド層と少なくとも1つのカルコゲナイド・ガラス層とが近接した抵抗可変メモリ・ディバイスが提供される。この発明はさらに,そのようなメモリ・ディバイスの形成方法に関する。 (もっと読む)

不揮発性メモリ

【課題】 対向する電極間に電気抵抗値が変化する金属酸化物を設け、低消費電力で駆動する低コスト、大記憶容量の低クロストークの特に携帯用機器のメモリとして最適な不揮発性メモリを提供する。

【解決手段】 本発明の不揮発性メモリは、クロスポイントメモリ構造または三次元構造を有する不揮発性メモリであって、対向する電極間に電気抵抗値が変化する金属酸化物を設け、前記対向する両電極のうち少なくとも一方の電極の金属酸化物と接触する面に電界集中部を設けたものである。

(もっと読む)

不揮発性メモリとその製造方法

【課題】 対向する電極間に電気抵抗値が変化する金属酸化物を設け、低消費電力で駆動する低コスト、大記憶容量の低クロストークの特に携帯用機器のメモリとして最適な不揮発性メモリとその製造方法を提供する。

【解決手段】 本発明の不揮発性メモリの製造方法は、対向する電極間に未結晶状態又は不完全な結晶化状態の金属酸化物を設け、前記電極間に高電界エネルギーを印加することにより、発生するジュール熱のエネルギーによって結晶化した金属酸化物からなるメモリ・セル(メモリ領域)を形成する。

(もっと読む)

相変化メモリ装置及びプログラム方法

【課題】相変化メモリ装置におけるプログラム時のピーク電流を低減する。

【解決手段】複数の相変化メモリセルと複数の順次リセットパルスを出力するために構成されたリセットパルス発生信号を含んだ相変化メモリ装置が提供される。それぞれの順次リセットパルスは対応される複数のリセットラインに出力される。複数のライトドライバ回路は対応の相変化メモリセルと対応のリセットパルス発生回路のリセットラインに連結される。順次リセット制御信号を用いて相変化メモリ装置をプログラムする方法が提供される。

(もっと読む)

自己スイッチングメモリデバイス

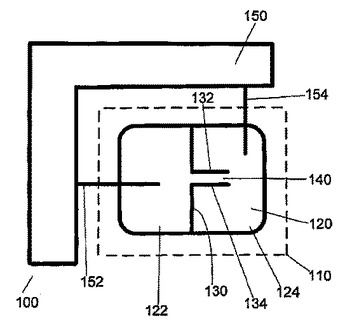

メモリデバイス、及び関連する製造及び動作の方法を説明している。該メモリデバイスは、移動電荷キャリアを支持する基板(120)を具えている少なくとも1つのメモリユニットを含む。該基板表面上には絶縁部(130、132、134)が形成され、該絶縁部の両側に第1及び第2基板領域(122、124)を形成している。該第1及び第2基板領域は、絶縁部によって形成された細長チャネル(140)によって接続されている。メモリユニットは、前記第1及び第2領域間の所定の電位差でチャネルが第1及び第2領域間に第1のコンダクタンスを与える第1の状態と、前記所定の電位差でチャネルが第1及び第2領域間に第2の異なるコンダクタンスを与える第2の状態との間で切り換え可能である。メモリユニットを第1の状態に変更するため、前記メモリユニットの第1及び第2領域に第1の電位差を、そしてメモリユニットを第2の状態に変更するため第2の異なる電位差を印加するよう、書き込み回路(150)が構成されている。メモリユニットの状態を読み出すため、メモリユニットの第1及び第2領域に前記所定の電位差を印加するよう、読み出し回路(150)が構成されている。  (もっと読む)

(もっと読む)

1,351 - 1,360 / 1,392

[ Back to top ]