国際特許分類[H03F1/42]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 増幅器 (10,074) | 増幅素子として電子管のみ,半導体装置のみまたは汎用素子のみを用いた増幅器の細部 (3,631) | 帯域幅を拡げるための増幅器の変形 (88)

国際特許分類[H03F1/42]の下位に属する分類

国際特許分類[H03F1/42]に分類される特許

21 - 30 / 56

広帯域増幅器

【課題】広帯域にわたって良好なインピーダンス整合を与えることができ、高調波処理を高い効率で可能とする広帯域増幅器を得る。

【解決手段】高周波信号を増幅するトランジスタ1と、トランジスタ1の出力端子に一端が直列接続された直列インダクタ6と、直列インダクタ6の他端に一端が並列接続されたショートスタブ2と、ショートスタブ2の他端を高周波短絡するためのキャパシタ3と、直列インダクタ6の他端に一端が並列接続されたオープンスタブ7と、ショートスタブ2の一端及びオープンスタブ7の一端の接続点に一端が接続されたインピーダンス変成器4とを備え、インピーダンス変成器4は、使用周波数の1/4波長の長さの線路であり、トランジスタ1の効率最適負荷インピーダンスは、50Ωより低く、容量性の領域にあり、前記接続点とインピーダンス変成器4の間のインピーダンスは、効率最適負荷インピーダンスと50Ωの間である。

(もっと読む)

増幅回路、半導体集積回路、無線伝送システム、通信装置

【課題】広帯域に亘って良好な利得を得ることができる増幅回路にする。

【解決手段】入力抵抗112,114を有する入力部3、差動構成の増幅セル120,140,160を縦続接続した増幅セル部4、増幅セル140の差動出力を増幅セル120の入力へ帰還する帰還抵抗182,184を有する直流帰還部5を設ける。増幅セル120はNMOS122,124と負荷抵抗126,128と電流源132を有する。増幅セル140はNMOS142,144と負荷抵抗146,148と電流源152を有する。増幅セル160はNMOS162,164と負荷抵抗166,168と電流源172を有する。差動接続された一対のNMOSの負荷としてインダクタンスやPMOSを用いずに負荷抵抗を使用した増幅セルを複数段縦続接続して利得を稼ぐとともに、後段側の増幅セルの出力から前段側の増幅セルの入力に対して帰還をかけることで負帰還増幅回路を構成する。

(もっと読む)

オペアンプ

【課題】新規なオペアンプの回路を示す。

【解決手段】オペアンプの、負の入力端子と出力端子の間に、直列にRc1とRc2を、Rc1とRc2の間のノードと正の入力端子の間にCc1を、正の入力端子とグラウンド端子の間に位相補償容量Cc2を、つないだことを特徴とするオペアンプ回路を示す。容量値、抵抗値はいずれも使用プロセスにおける、チップ面積の極端な増大につながらない範囲内の値で設定できる。また設計後に事後的に容量、容量と抵抗を追加でき、チップ外部に接続することも出来る。

(もっと読む)

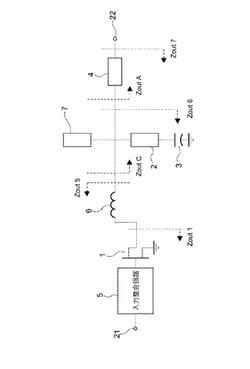

広帯域増幅器

【課題】チップ面積の増大を招くことなく、低損失で広帯域な出力整合を実現する。

【解決手段】増幅対象の信号を相互に180度の位相差を有する信号に分配する180°ハイブリッド1と、180°ハイブリッド1から出力された一方の分配信号がゲート電極Gに与えられるトランジスタ3と、180°ハイブリッド1から出力された他方の分配信号がゲート電極Gに与えられ、ドレイン電極Dがトランジスタ3のドレイン電極Dと接続されているトランジスタ4とを設け、180°ハイブリッド6がトランジスタ3のドレイン電極Dから出力された信号とトランジスタ4のドレイン電極Dから出力された信号の位相を揃えて合成する。

(もっと読む)

マイクロ波、ミリ波帯増幅回路及びそれを用いたミリ波無線機

【課題】トランジスタの最高発振周波数fmaxに近く、その性能に余裕のない高い周波数領域において、平坦な利得を広い帯域に渡って保持する広帯域な増幅回路を得るには、大きな損失のため整合回路に抵抗素子を用いることができないため、無損失素子のみを用いて、できるだけ簡便な回路構成にする必要がある。

【解決手段】入力から出力に向かって、サイズが段階的に大きくなるトランジスタ11、12・・・1nを縦続接続させたn段増幅回路において、整合回路21、22・・・2nが、ハイパス特性を持つように設計されており、そのカットオフ周波数(低域遮断周波数)f1, f2・・・fnが、入力から出力に向かって、段階的に低くなるように構成する。

(もっと読む)

高周波半導体増幅器

【課題】 スタブを用いることなく高調波インピーダンスの調整を行い、高調波処理可能な高効率で広帯域の高周波半導体増幅器を提供する。

【解決手段】 半導体増幅素子5と、マイクロ波の1/4波長の長さで形成した第1インピーダンス変成器1と、マイクロ波の1/4波長の長さで形成した第2インピーダンス変成器2と、第1及び第2インピーダンス変成器とで変成されたインピーダンスと整合する高調波インピーダンス調整線路3と、誘導性リアクタンス成分でインピーダンス変換する素子近傍整合回路4と、抵抗器を備え、高調波インピーダンス調整線路3は高調波に対するインピーダンス変換を行い、素子近傍整合回路4は基本波に対しては半導体増幅素子5のインピーダンスと整合するようにインピーダンス変換して収束させ、高調波に対しては開放インピーダンス近傍となるようにインピーダンス変換して収束させるようにした。

(もっと読む)

伝送線路トランス及びこれを備える増幅ユニット

【課題】インピーダンス特性の調整操作の操作性を良好にする。

【解決手段】磁性体からなるコア材2と、伝送線路3と、を備える伝送線路トランス1である。コア材2は、伝送線路3が巻回された本体部4と、本体部4に対して当接したまま移動させる操作が可能な可動部5と、からなる。伝送線路トランス1は基板6上に設けられるものである。可動部5の少なくとも一部(例えば、頭部11)は、本体部4に対して基板6の反対側に位置する。可動部5は、可動部5の少なくとも一部(例えば、頭部11)に対する操作によって、本体部4に対し移動される。

(もっと読む)

電力増幅装置及び電力増幅装置のバイアス制御方法

【課題】伝送信号の広帯域化に柔軟に対応してアイドル電流を自動調整し得る電力増幅装置及び電力増幅装置のバイアス制御方法を提供する。

【解決手段】電力増幅装置1内にインタフェース部14,15を内蔵させ、かつ制御部16に送信周波数情報とアイドル電流のデフォルト値とを対応付けて記憶するメモリ161を備えて、インタフェース部14,15に接続される上位の送信制御装置2またはパーソナル・コンピュータ3から送信周波数情報が送られたときに、制御部16にてこの送信周波数情報に対応するアイドル電流のデフォルト値をメモリから読み出して、このデフォルト値に基づいて、FET12に与えられるアイドル電流がデフォルト値になるようにFET12のバイアス電圧を調整するようにしている。

(もっと読む)

増幅回路および光変調器用ドライバ回路

【課題】大振幅出力および広帯域周波数特性を確保することができ、特に光変調器のドライバICに適用可能な増幅回路を提供する。

【解決手段】増幅回路は、入力段トランジスタ11と出力段トランジスタ12とを含み、入力された信号を入力段トランジスタ11および出力段トランジスタ12で増幅して出力する多段増幅部10と、多段増幅部10の出力を、該多段増幅部における出力段トランジスタ12の入力に帰還する帰還部20と、を備える。帰還部20は、第1帰還トランジスタ21a、第2帰還トランジスタ21bおよび帰還抵抗RFを含み、多段増幅部10の出力を、第1帰還トランジスタ21a、第2帰還トランジスタ21bおよび帰還抵抗RFを介して出力段トランジスタ12の入力に帰還する。

(もっと読む)

ジョセフソン分布出力増幅器のための方法および装置

本開示は、概して高速、低信号電力増幅を提供する方法および装置に関する。1つの例示的実施形態において、本開示は、第1の伝送線を第2の伝送線と並列に形成することによる、信号の広帯域増幅を提供する方法に関し、第1の伝送線および第2の伝送線の各々は、複数の超伝導伝送要素を有し、各伝送線は伝送線遅延を有し、複数の増幅段を第1の伝送線と第2の伝送線との間に挿入し、各増幅段は共振回路遅延を有する共振回路を有し、複数の増幅段のうちの少なくとも1つに対する共振回路遅延を超伝導伝送線のうちの少なくとも1つの伝送線遅延と、実質的に整合させる。  (もっと読む)

(もっと読む)

21 - 30 / 56

[ Back to top ]