国際特許分類[H03F1/42]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 増幅器 (10,074) | 増幅素子として電子管のみ,半導体装置のみまたは汎用素子のみを用いた増幅器の細部 (3,631) | 帯域幅を拡げるための増幅器の変形 (88)

国際特許分類[H03F1/42]の下位に属する分類

国際特許分類[H03F1/42]に分類される特許

11 - 20 / 56

ジャイレータ回路、広帯域増幅器及び無線通信装置

【課題】差動増幅器が持つ周波数帯域を広げることができるジャイレータ回路、及びこのジャイレータ回路を有する広帯域増幅器及び無線通信装置を提供すること。

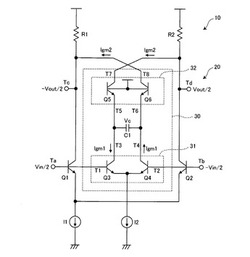

【解決手段】ベースを差動入力端子T1,T2とし、コレクタを差動出力端子T3,T4とする一対のトランジスタQ3,Q4からなる第1のトランスコンダクタンスアンプ31と、第1のトランスコンダクタンスアンプ31の差動出力端子T3,T4間に接続されたコンデンサC1と、エミッタを差動入力端子T5,T6とし、コレクタを差動出力端子T7,T8とする一対のトランジスタQ5,Q6からなる第2のトランスコンダクタンスアンプ32とを有し、第1のトランスコンダクタンスアンプ31の差動入力端子T1,T2と第2のトランスコンダクタンスアンプ32の差動出力端子T7,T8とを分離した状態としてジャイレータ回路を構成する。

(もっと読む)

低音増幅回路

【課題】 簡易な構成で低域を増強する。

【解決手段】 LPF41を通過した入力信号は、高周波音発生部42からの帯域外の高周波音が加算器43で加算される。D/A44でアナログに変換された加算器43からの出力はアナログボリューム45で調整され、アナログボリューム45の出力から高周波音の成分をHPF48により抽出する。抽出された高周波音の成分のレベルA’と、加算器43で加算された高周波音のレベルAとのレベル比A’/Aに応じてLPF41における高域の減衰特性を制御する係数を決定する。

(もっと読む)

増幅器および信号増幅方法

【課題】超広帯域応用のために高い電圧利得および利得帯域幅を有するCMOS型の増幅器を提供する。

【解決手段】CMOS増幅器300は、第1電源VDDと第2電源GNDとの間でフィードバック動作を行うNチャンネルMOSFET N1,N2を用いることにより、ゼロ位置を追加して利得を増加させる能動負荷回路310と、能動負荷回路310に連結されて共通バイアスVCを受ける電流制御回路320と、電流制御回路320に連結されて差動入力信号VIN+,VIN−を受ける信号入力回路330と、第2電源GNDと信号入力回路330との間に連結された第1電流源と、を備え、差動入力信号VIN+,VIN−を受けて増幅し、電流制御回路320の二つのMOSFETと能動負荷回路310との間の二つの接点VOUT+,VOUT−を介して差動信号を出力する。

(もっと読む)

広帯域高出力増幅器

【課題】広帯域増幅器の出力不整合と周波数切り替え回路で発生する不整合を調整し、高効率化を図ることができる広帯域高出力増幅器を得る。

【解決手段】少なくとも2倍高調波が広帯域増幅器1自身の帯域に含まれる広帯域高出力増幅器において、広帯域増幅器1の後段に、周波数帯域に応じた信号出力の切り替えを行う周波数切り替え回路2と、インピーダンス不整合を調整する整合回路5と、周波数帯域に応じて高調波成分を抑制するフィルタ回路4とを順次接続し、インピーダンス調整用整合回路5は、広帯域増幅器1の出力不整合と周波数切り替え回路2で発生する不整合を調整する。

(もっと読む)

アナログ高速増幅器及びそれを使用するイメージセンサ

【課題】消費電力の増加を抑制しつつスルーレートを向上させる一方飽和画素の影響を低減し、高い線形性を実現することができるアナログ高速増幅器を提供する。

【解決手段】本発明に係るアナログ高速増幅器は、所定のクロック周期で独立したレベルの信号を入力し増幅するアナログ高速増幅器において、増幅部本体と、前記クロック周期をサンプリング期間とリセット期間に分割し、前記信号を前記サンプリング期間中に前記増幅部本体に入力するサンプリング手段と、前記リセット期間中に、前記増幅部本体の出力を所定のリセット電位にリセットするリセット手段と、前記サンプリング期間のうち、前記サンプリング期間の開始時点から前記サンプリング期間よりも短い所定の期間を電流増加期間とし、前記電流増加期間中は、前記増幅部本体に供給する動作電流を前記電流増加期間以外の期間よりも増加させる、動作電流制御手段と、を備えたことを特徴とする。

(もっと読む)

高周波増幅回路

【課題】高周波増幅回路において、LC共振を用いずにピーキングをかけること。

【解決手段】高周波増幅回路は、1段目にトランジスタTr1を用いたエミッタ接地増幅回路、2段目にダーリントン接続のトランジスタTr2、Tr3を用いたエミッタ接地回路の2段増幅の構成となっている。トランジスタTr1のエミッタとトランジスタTr2のコレクタとの間には容量素子が挿入されている。容量素子は、ダイオード接続のトランジスタTr4であり、トランジスタTr4のエミッタはトランジスタTr2のコレクタに、トランジスタTr4のベースおよびコレクタはトランジスタTr1のエミッタに接続されている。ダイオード接続のトランジスタTr4によって位相をずらしてフィードバックすることにより、高域での利得を向上させることができる。

(もっと読む)

半導体集積回路およびそれを用いた差動増幅器およびバッファアンプ

【課題】バイアス信号を切りかえに伴う動作特性の悪化を低減した半導体集積回路を提供する。

【解決手段】半導体集積回路10は、入力電流Iinを受け、それに応じた出力電流Iout1を別の回路に供給する。第1可変抵抗R1の第1端子は、入力端子P1と接続される。第1トランジスタM1および第2トランジスタM2は、電源端子と第1可変抵抗R1の第2端子の間に順に直列に設けられる。第3トランジスタM3および第4トランジスタM4は、電源端子と出力端子P2との間に順に直列に設けられる。第1トランジスタM1および第3トランジスタM3それぞれのゲートは第1可変抵抗R1の第2端子に接続される。第2トランジスタM2および第4トランジスタM4それぞれのゲートは入力端子P1に接続されている。第1可変抵抗R1は、その抵抗値が入力電流Iinに応じて切りかえ可能に構成される。

(もっと読む)

電力増幅回路

【課題】それぞれが異なる周波数帯域を有する複数の無線信号を最適なバイアス条件で電力増幅できる電力増幅回路を提案する。

【解決手段】電力増幅回路11は、それぞれが異なる周波数帯域を有する複数の無線信号の中から選択された何れか一つの無線信号を電力増幅する増幅器20と、選択された一つの無線信号の周波数帯域に応じて増幅器20に供給されるバイアス電圧を可変設定するバイアス制御回路61を備える。

(もっと読む)

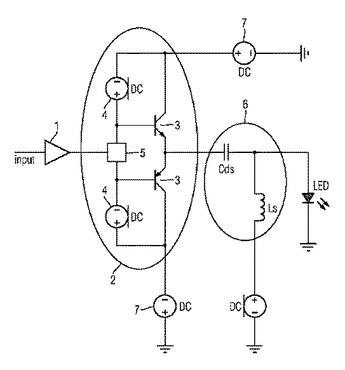

高い出力性能とコンパクトな構造を有する広帯域高線形性LED増幅器

本発明は、発光ダイオードを駆動制御する増幅回路に関する。この増幅回路は、約3オームの小さい出力インピーダンスと、200KHzの下方境界周波数と例えば5MHzの上方境界周波数とを備えた広い帯域幅と、例えば数100mAの出力電流振幅とを有する。この増幅回路は、直流電流供給部(6)によって発光ダイオードを駆動制御するドライバー回路(2)を駆動制御する入力段を有している、という特徴を有している。  (もっと読む)

(もっと読む)

可変インダクタ、電圧制御発振器、複合型PLL回路、フィルタ回路および増幅回路

【課題】制御電圧入力端子の個数を減少させることができる新規な可変インダクタならびにその新規な可変インダクタを備える電圧制御発振器、複合型PLL回路、フィルタ回路および増幅回路を提供する。

【解決手段】本発明の可変インダクタ5においては、複数のインダクタンス素子61、62、63、64におけるそれぞれの接続点とグランド10との間にそれぞれ接続された複数のスイッチダイオード7A、7B、7Cのそれぞれの一端側に対して、複数の定電圧入力端子8A、8B、8Cを介して、互いに異なる定電圧がそれぞれ供給されている。また、本実施形態の可変インダクタ5においては、複数のスイッチダイオード7A、7B、7Cにおけるそれぞれの他端側に対して、1個の制御電圧入力端子9を介して、制御電圧が供給されている。

(もっと読む)

11 - 20 / 56

[ Back to top ]