国際特許分類[H03F3/195]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 増幅器 (10,074) | 増幅素子として電子管のみまたは半導体装置のみをもつ増幅器 (6,434) | 高周波増幅器,例.無線周波増幅器 (626) | 半導体装置のみをもつもの (431) | 集積回路におけるもの (122)

国際特許分類[H03F3/195]に分類される特許

1 - 10 / 122

CMOS集積回路及び増幅回路

【課題】SOI基板にLNA回路を形成した場合や、バルクCMOSプロセスを用いてLNA回路を形成した場合に、NFの劣化の回避と高い線形性の達成とを実現することが可能なCMOS集積回路を提供する。

【解決手段】ゲート電極に信号入力端子が、ドレイン電極に電源端子が、ソース電極に接地端子がそれぞれ接続された電界効果トランジスタを備え、前記電界効果トランジスタはSOI(Silicon−On−Insulator)基板上に形成し、ボディ電位と、ソース電位以下の電位との間を、抵抗素子で接続することを特徴とする、CMOS集積回路が提供される。かかるCMOS集積回路を用いることで、NFの劣化の回避と高い線形性の達成とを実現することが可能となる。

(もっと読む)

高周波増幅器

【課題】ユニットセルの組み合わせで形成されるすべてのループ発振を抑制することができる高周波増幅器を提供する。

【解決手段】実施の形態に係る高周波増幅器は、入力された信号を分配する分配回路と、分配回路が分配した信号を増幅するFETセルと、分配回路とFETセルのゲート端子との間に直列に接続され、キャパシタと抵抗との並列回路から構成される安定化回路と、FETセルが増幅した信号を合成する合成回路とを備え、安定化回路をFETセルごとに配置する。

(もっと読む)

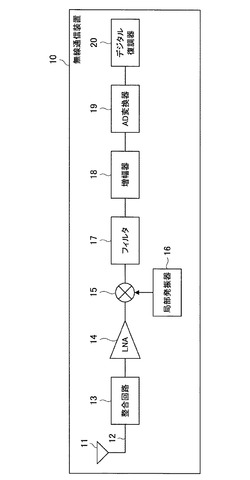

回路定数調整器及びそれを用いた低雑音増幅装置

【課題】 安定した発振抑制効果が得られると共に高精度に発振が抑制できるように回路定数が調整できるようにする。

【解決手段】 回路定数を調整する回路定数調整器16であって、終端が開放端に形成されたスタブ16eと、一端17bがスタブ16eに接続されると共に、他端17aが回路定数調整対象の回路12に接続され、かつ、抵抗値が設定可能に設けられた可変抵抗器16aと、可変抵抗器16aに制御信号を出力して、当該可変抵抗器16aの抵抗値を設定する抵抗値設定器16cと、を備える。

(もっと読む)

高線形性相補型増幅器

【課題】サブミクロンCMOSプロセスで製造されることができかつ良好な線形性および信頼性を有する相補型増幅器を提供する。

【解決手段】PMOSトランジスタ422とそれにスタック結合されたNMOSトランジスタ412で構成した相補型増幅器400で、NMOSトランジスタ412およびPMOSトランジスタ422は、別々のバイアス電圧を有し、それらのバイアス電圧は、各トランジスタの相互コンダクタンスの低高および高低遷移をオーバーラップさせるように選択され、各トランジスタの幅および長さ寸法は、中反転領域におけるNMOSトランジスタ412の入力容量の変化および相互コンダクタンスの変化を中反転領域におけるPMOSトランジスタ422の入力容量の変化および相互コンダクタンスの変化と整合させるように選択される。それによりほぼ一定の総入力容量およびほぼ一定の総相互コンダクタンスを有しうる。

(もっと読む)

バイアス回路を一体化した金属酸化膜半導体デバイス

【課題】デバイスの温度変動および/またはプロセス変動に起因するMOSデバイスのバイアス条件の変動を正確に補償できる技術を提供する。

【解決手段】ICデバイスがゲート端子、ソース端子およびドレイン端子を有するMOSデバイスを備え、ゲート端子はICデバイスの入力部に動作可能に結合され、ドレイン端子はICデバイスの出力部に動作可能に結合され、ソース端子は負電圧供給源に結合している。ICデバイスは、さらに、MOSデバイスのゲート端子に動作可能に結合されているバイアス発生器を備え、このバイアス発生器は、MOSデバイスにほぼ一定の静止動作点でバイアスをかけるバイアス電圧および/またはバイアス電流を発生する。バイアス発生器は、バイアス電圧および/またはバイアス電流がMOSデバイスの接合温度の関数として変化するように構成されている。このようにして、バイアス発生器が、MOSデバイスの1つまたは複数の動作条件を正確にたどり、それによってデバイスの性能を向上させる。

(もっと読む)

アクティブポストディストーション線形化を有する差動増幅器

【課題】電力消費量を低下させ、回路面積を縮小した線形性がより高いLNAを提供する。

【解決手段】差動増幅器300の一腕は第1トランジスタ310及び第2トランジスタは320、第1のカスケード対として結合され、第3トランジスタ330及び第4トランジスタ340は、第2のカスケード対として結合される。第3トランジスタ330は、第2トランジスタ320のソースに結合したゲートを有し、第4トランジスタ340は、第2トランジスタ320のドレインに結合したドレインを有する。第3トランジスタ330は、第1トランジスタ310によって生成される3次歪み成分を除去するのに用いられる歪み成分を生成する。誘導子350は、第1トランジスタ310に対してソースディジェネレーションを提供し、歪み除去を向上させる。第2トランジスタ320及び第3のトランジスタ330の大きさは、利得損失を低減させるために選択される。

(もっと読む)

低雑音増幅器及び無線通信機

【課題】ゲインの切替えを行っても入力インピーダンスが変化することがなく安定した受信性能を得ることができる低雑音増幅器及び無線通信機を得る。

【解決手段】受信側のローノイズアンプ20を、ゲイン切替え機能を備えたアンプ部201と、アンプ部201をローゲインに設定したときのローノイズアンプ20の入力インピーダンスがハイゲインに設定したときの入力インピーダンスに合うようなインピーダンス素子202と、インピーダンス素子202のアンプ部201の入力端への接続/切り離しを行うスイッチ203とで構成し、アンプ部201をローゲインに設定したときにインピーダンス素子202をアンプ部201の入力端に接続するようにした。これにより、アンプ部201のゲインの切替えを行ってもローノイズアンプ20の入力インピーダンスを一定に保つことができる。

(もっと読む)

定電圧回路及び増幅回路

【課題】ゲート容量が大きなトランジスタを有する増幅器に接続しても発振を防止できる定電圧回路及び増幅回路を提供する。

【解決手段】定電圧回路40は、所定の電圧が印加される第1の入力端子44と、出力端子46に接続された第2の入力端子とを備えた差動増幅部41と、ソースが接地され、ドレインが出力端子46に接続され、ゲートに差動増幅部41の出力が与えられるトランジスタT46を備えたソース接地型増幅器42とを有する。そして、トランジスタT46のゲートとドレインとの間には、抵抗47とコンデンサ48とが直列に接続されている。定電圧回路40から出力される電圧Vgは、増幅器20のバイアス端子26bからバイアス給電用インダクタ25a,25bを介してトランジスタT3,T4に供給される。

(もっと読む)

半導体集積回路および受信装置

【課題】低コストかつノイズの影響を受けにくい半導体集積回路およびこれを用いた受信装置を提供する。

【解決手段】実施形態によれば、半導体集積回路は、トランスコンダクタンス回路と、第1の負荷回路と、第2の負荷回路とを備える。前記トランスコンダクタンス回路、前記第1の負荷回路および前記第2の負荷回路の少なくとも1つは、下式のパラメータPが低減されるようにインピーダンスを調整するインピーダンス調整部を有する。P=Z01*Z04−Z02*Z03。ここで、Z01は前記第1の出力端子から見た前記トランスコンダクタンス回路のインピーダンス、Z02は前記第2の出力端子から見た前記トランスコンダクタンス回路のインピーダンス、Z03は前記第1の負荷回路のインピーダンス、Z04は前記第2の負荷回路のインピーダンス。

(もっと読む)

集積フィルタを備えた増幅器

【課題】良好な雑音性能を有しかつ大きい干渉信号に対処できる増幅器を提供する。

【解決手段】集積フィルタを備えた増幅器320b(例えば,LNA)は利得ステージ330、フィルタ・ステージ340およびバッファ・ステージ350を含んでいてもよい。利得ステージは、入力信号に対して信号増幅を提供する。フィルタ・ステージは、入力信号に対してフィルタリングを提供する。バッファ・ステージは、フィルタ・ステージからのフィルタされた信号をバッファする。増幅器は、第2のフィルタ・ステージ360及び第2のバッファ・ステージ370をさらに含んでいてもよい。

(もっと読む)

1 - 10 / 122

[ Back to top ]