国際特許分類[H03H19/00]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | インビーダンス回路網,例.共振回路;共振器 (15,336) | 時間変化要素を用いる回路網,例.N一路フィルター (94)

国際特許分類[H03H19/00]に分類される特許

31 - 40 / 94

フィルタ回路および通信装置

【課題】フライングキャパシタを備え、急峻な減衰特性を備えた上でさらにQ値を可変にすることが可能なフィルタ回路の提供。

【解決手段】入力端から出力端へ切り替わる場合には極性を維持し、出力端から入力端へ切り替わる場合には極性が反転するフライングキャパシタと、フライングキャパシタの入力端にフライングキャパシタと並列に設けられる第1のキャパシタCh1と、フライングキャパシタの出力端にフライングキャパシタと並列に設けられる第2のキャパシタCh2と、を備え、フライングキャパシタは、出力端から入力端へ切り替わってから所定の時間遅延して入力端から出力端へ切り替わり、入力端から出力端へ切り替わってから所定の時間遅延して出力端から入力端へ切り替わる、フィルタ回路。

(もっと読む)

サンプリングフィルタ

【課題】単極性の電圧電流変換回路を並列に接続することなく、正のタップ係数と負のタップ係数を同時に実現することができるサンプリングフィルタを提供する。

【解決手段】制御信号生成回路が充放電部3を構成しているスイッチ11〜17を制御して、電圧電流変換回路2から出力される電流を充放電部3を構成している2つのキャパシタ21,22に供給することで、キャパシタ21,22に電荷を充電させる一方、充放電部3を構成しているスイッチ11〜17を制御して、キャパシタ21,22に充電されている電荷を出力端子5,6に放電させる。

(もっと読む)

受動無線受信機

入力信号を受信しその入力信号を受動的に処理して出力信号を発生する受動無線受信機。この受動受信機の実施例は入力回路、ダイナミックスイッチング回路、スイッチ信号発生器を含む。この入力回路は入力信号を受信して第1の出力信号を発生するように構成される。入力回路はその入力信号に条件付けするように構成された受動ネットワークを含む。このダイナミックスイッチング回路は第1の出力信号に対して周波数変換を行なうように構成される。スイッチ信号発生器は、周波数制御回路によって制御され安定化されるサンプリング周波数でダイナミックスイッチング回路を活性化及び非活性化するようにダイナミックスイッチング回路を駆動するように構成される。 (もっと読む)

サンプルホールド回路

【課題】キャパシタを用いたサンプルホールド回路において、サンプリング時におけるキャパシタの充電状態をホールド状態とするためにオフされるべきスイッチにリーク電流が生じる。

【解決手段】サンプルホールド回路10は、オペアンプ12の反転入力端子IN−に一方端を接続されたキャパシタC1にサンプリング電圧に応じた電荷を蓄積する。その際、C1のIN−側の端子はスイッチ回路14を介して出力端子VOUTに接続し、所定電位に設定する。ホールド状態ではスイッチ回路14はオフされ、それが接続されたC1の端子をフローティング状態とする。スイッチ回路14は、IN−とVOUTとの間に直列に接続され同相でオン・オフされるMOSトランジスタスイッチS11,S12と、それら相互の接続点と接地電位との間に接続されたキャパシタC2とからなる。

(もっと読む)

離散時間型マルチ・レート・アナログ・フィルタ

【解決手段】レシーバ及び他の電子デバイスでの使用に適した離散時間型アナログ・フィルタが明細書に記載されている。一デザイン例の装置は、トランスコンダクタンス増幅器、サンプラ、及び離散時間型アナログ・フィルタを備え得る。トランスコンダクタンス増幅器は、電圧入力信号を増幅しアナログ信号を提供し得る。サンプラは、サンプリング・レートでアナログ信号をサンプリングし、アナログ・サンプルを提供し得る。離散時間型アナログ・フィルタは、ノン・デシメート・フィルタのサンプリング・レート、またはデシメート・フィルタのサンプリング・レートよりも低い出力レートでアナログ・サンプルをフィルタリングし、フィルタリングされたアナログ・サンプルを提供し得る。離散時間型アナログ・フィルタはまた、レクタンギュラ・フィルタの均等な重み、または重み付けフィルタの少なくとも二つの異なる重みでアナログ・サンプルをフィルタリングし得る。 (もっと読む)

アナログスイッチおよびスイッチトキャパシタフィルタ

【課題】MOSトランジスタの接合部における漏れ電流を抑制することができるアナログスイッチおよびこれを用いたスイッチトキャパシタフィルタを提供する。

【解決手段】スイッチトキャパシタフィルタ8を構成するアナログスイッチSW5の基板電位を切り替え可能に構成する。基板電位切替回路13は、キャパシタCs1からキャパシタCf1に電荷が転送される期間中には、PチャネルMOSトランジスタQp5の基板電位を電源電圧Vccに固定するとともにNチャネルMOSトランジスタQn5の基板電位を接地電位に固定する。

(もっと読む)

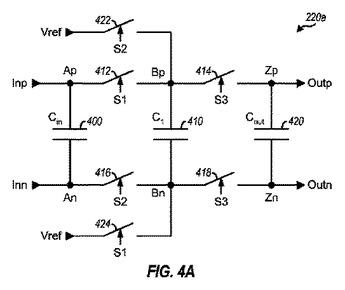

スイッチドキャパシタデシメータ

出力サンプルレートの奇数高調波における望ましくない信号成分を減衰させることができるスイッチドキャパシタデシメータが、説明される。スイッチドキャパシタデシメータは、少なくとも1つのサンプリングキャパシタと、複数のスイッチと、を含む。各サンプリングキャパシタでは、上部プレートは、キャパシタが上部充電のために選択されるときに、第1の入力信号で充電され、下部プレートは、キャパシタが下部充電のために選択されるときに、第2の入力信号で充電される。各サンプリングキャパシタでは、キャパシタが読取りのために選択されるときに、上部プレートは、その蓄積された電荷を第1の出力信号へと供給し、下部プレートは、その蓄積された電荷を第2の出力信号へと供給する。スイッチは、充電のためには第1および第2の入力信号に、読取りのためには第1および第2の出力信号に、少なくとも1つのサンプリングキャパシタを結合する。  (もっと読む)

(もっと読む)

ローパスフィルタおよび半導体圧力センサ装置

【課題】カットオフ周波数が低い場合であっても、電源オンの後速やかに出力を安定させる。

【解決手段】電源オンから整定化時間Tsが経過するまでは、フィルタ動作有効化信号φ3をオフにするとともに第1相、第2相クロックパルスφ1、φ2をともにオンにして、アナログスイッチS11〜S26をオン、アナログスイッチS37をオフにする。整定化時間Tsが経過した後は、フィルタ動作有効化信号φ3をオンにするとともに第1相、第2相クロックパルスφ1、φ2を互いにオン期間が異なるように2相動作させ、スイッチトキャパシタフィルタとして動作させる。

(もっと読む)

スイッチトキャパシタ回路を用いた積分回路、ローパスフィルタおよび電子機器

【課題】 カットオフ周波数が極めて低いスイッチトキャパシタ積分回路を、オペアンプの入力容量とオペアンプの帰還容量の比を大きくすることなく、高精度に実現する。

【解決手段】 積分回路50の入力部100に含まれるスイッチトキャパシタ回路(SC回路)は、第1のスイッチ回路SW1と、第1のキャパシタ部TS(1)と、第2のスイッチ回路SW2と、第2のキャパシタ部TS(2)と、第3のスイッチ回路SW3と、第4のスイッチ回路SW4と、を有し、第1のキャパシタ部TS(1)は、T字形に結線されたキャパシタGA1,GA2およびGA3を有し、第2のキャパシタ部TS(2)は、T字形に結線されたキャパシタGB1,GB2およびGB3を有する。

(もっと読む)

集積回路装置及び電子機器

【課題】周波数帯域、振幅、DCオフセット等が異なる様々な入力信号に対応してA/D変換を実現できる集積回路装置及びこれを含む電子機器の提供。

【解決手段】集積回路装置は、入力信号VIが入力され、入力信号CIのDCオフセットに応じたオフセット調整と、入力信号VIの振幅に応じたゲイン調整を行う増幅回路10と、増幅回路10の後段側に設けられ、入力信号VIの周波数帯域に応じてカットオフ周波数が可変に設定されるフィルタ38と、フィルタ38の後段側に設けられ、増幅回路10により増幅された信号に対するA/D変換を行うA/D変換器50と、増幅回路10でのオフセット調整の設定と、増幅回路10でのゲイン調整の設定と、フィルタ38でのカットオフ周波数の設定を行う制御回路70を含む。

(もっと読む)

31 - 40 / 94

[ Back to top ]