国際特許分類[H03K19/0944]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 論理回路,すなわち,1出力に作用する少なくとも2入力を持つもの;反転回路 (4,821) | 特定の構成要素を用いるもの (1,730) | 半導体装置を用いるもの (1,065) | 電界効果トランジスタを用いるもの (1,019) | MOSFETを用いるもの (616)

国際特許分類[H03K19/0944]の下位に属する分類

CMOSを用いるもの (413)

国際特許分類[H03K19/0944]に分類される特許

81 - 90 / 203

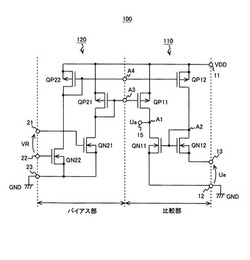

コンパレータ回路

【課題】出力電圧信号の振幅を十分にとれない場合があった。

【解決手段】本発明は、参照電圧を入力する第1、第2の端子と、基準電圧を入力する第3の端子と、検出すべき電圧を入力する第4の端子と、参照電圧の電位差に応じた電流をそれぞれ流す第1、第2のトランジスタ(以下、Tr)と、第1のTrと直列接続される第3のTrと、第2のTrと直列接続される第4のTrと、第3のTrの流す電流に応じたミラー電流を流す第5のTrと、第4のTrの流す電流に応じたミラー電流を流す第6のTrと、第6のTrと第4の端子との間に接続される第7のTrと、第5のTrと第3の端子との間に接続され、第7のTrの流す電流に応じたミラー電流を流す第8のTrと、を有し、第5、第8のTrの中間ノードの電圧に応じた電圧を出力信号として出力するコンパレータ回路である。

(もっと読む)

半導体装置

【課題】スタンバイ時の電流消費をより低減する。

【解決手段】機能回路13a、13bと、電源電位Vxを機能回路に供給するか否かを制御するPMOSトランジスタMP1、MP2と、電源電位GNDを機能回路に供給するか否かを制御するNMOSトランジスタMN1、MN2と、第3の電源電位が供給される外部端子VDD2と、第3の電源電位よりも高い電位レベルの第4の電源電位が供給される外部端子VDD1と、PMOSトランジスタMP1、MP2の導通状態及び非導通状態を制御するように、第4の電源電位を振幅とする制御信号CONT1をPMOSトランジスタMP1、MP2に供給すると共に、NMOSトランジスタMN1、MN2の導通状態及び非導通状態を制御するように、第3の電源電位を振幅とする制御信号CONT2をNMOSトランジスタMN1、MN2に供給する電源制御回路12と、を備える。

(もっと読む)

半導体装置

【課題】ヒューズの切断と検出を安定的に高い信頼性で行う。

【解決手段】半導体集積回路にトリミング用のヒューズF3と参照用のヒューズF1、F2を設ける。ヒューズF3の切断時には、外部端子V2にヒューズ切断用の高電圧Vhhを印加しながら、トランジスタN6をオン状態に制御してノードV5に接地電圧GNDを印加する。ヒューズF3の検出時には、トランジスタN1で構成されたクランプ回路と抵抗R1を用いてヒューズF1に流れる電流I1の量を決定し、カレントミラー回路M1〜M3を用いて電流I1を電流I2〜I4にコピーする。好適なカレントミラー比を設定し、ヒューズF3に流れる電流をヒューズF1に流れる電流よりも少なくする。

(もっと読む)

CML信号の論理ファミリ間の変換を行うシステムおよび方法

【課題】CML信号論理ファミリ間の変換を行うシステムおよび方法を提供すること。

【解決手段】システムは、第1のバイアス信号および第1のCML論理ファミリの第1のCML信号を受け取るように構成される第1のCMLバッファを備える。第1のCMLバッファは、第1のCML信号および第1のバイアス信号に基づいて、第1のCML論理ファミリの第2のCML信号を生成する。第1の結合コンデンサ・モジュールは、第1のCMLバッファに結合している。第1の結合コンデンサ・モジュールは、第2のCML信号を受け取り、第2のCML信号に基づいて第3のCML信号を生成する。第2のCMLバッファは、結合コンデンサ・モジュールに結合しており、第2のバイアス信号および第3のCML信号を受け取って、第2のCML論理ファミリの第4のCML信号を生成する。帰還モジュールは、第2のCMLバッファに結合しており、第4のCML信号を受け取って第5のCML信号を生成する。第2のCMLバッファは、第2のバイアス信号、第3のCML信号、および第5のCML信号に基づいて第4のCML信号を生成する。

(もっと読む)

電子回路および電圧検出回路

【課題】回路の動作電圧より低い電圧を用いた場合であっても出力が不定になるのを防止でき、チップ面積を小さくできコスト低減ができる電子回路を提供。

【解決手段】インバータ22の入力がゲートに接続されたデプレッション型Pchトランジスタ32と、インバータ22の出力がゲートに接続されたデプレッション型Nchトランジスタ31を設け、デプレッション型Nchトランジスタ31のソースをデプレッション型Pchトランジスタ32のソースに接続し、デプレッション型Pchトランジスタ32のドレインを第二の端子2に接続し、デプレッション型Nchトランジスタ31のドレインを第三の端子(出力端子)102が接続する。電源4の電圧が低下してインバータ22を構成するエンハンスメント型Pchトランジスタ51とエンハンスメント型Nchトランジスタ52が動作できなくなっても回路の出力102をLレベルとすることができる。

(もっと読む)

二重絶縁ゲート型電界効果トランジスタを用いたゲート回路、SRAMセル回路、多入力CMOSゲート回路、CMOS−SRAMセル回路、集積回路

【課題】高速動作と消費電力の減少を両立させた二重絶縁ゲート型電界効果トランジスタを用いた回路を提供する。

【解決手段】第一の四端子二重絶縁ゲート電界効果トランジスタは、一方のゲートを入力端子、ソースを第一の電源に接続し、ドレインを出力端子、該ドレインを負荷素子を介して第四の電源に接続し、他方のゲートに第一の三端子絶縁ゲート電界効果トランジスタのドレインを接続し、前記第一の三端子絶縁ゲート電界効果トランジスタは、ソースを第二の電源に接続し、ゲートを第三の電源に接続し、前記三端子絶縁ゲート電界効果トランジスタのドレインとソースの間の抵抗と前記四端子二重絶縁ゲート電界効果トランジスタの一方のゲートと他方のゲートの間のゲート絶縁膜容量と前記両ゲートに挟まれた半導体の容量で微分回路を構成したゲート回路で、前記第一の四端子二重絶縁ゲート電界効果トランジスタの一方のゲートと他方のゲート間を容量で接続する。

(もっと読む)

二重絶縁ゲート電界トランジスタを用いたMOSトランジスタ回路およびそれを用いたCMOSトランジスタ回路、SRAMセル回路、CMOS−SRAMセル回路、集積回路

【課題】単位回路の、高速動作と未使用時(電源電圧は印加されているが、所望の回路構成には用いられていないMOSトランジスタ群)または定常時または待機時における消費電力の減少を両立させた二重絶縁ゲート電界トランジスタを用いたMOSトランジスタ回路およびそれを用いたCMOSトランジスタ回路、SRAMセル回路、CMOS−SRAMセル回路、集積回路を提供する。

【解決手段】四端子二重絶縁ゲート電界効果トランジスタからなるMOSトランジスタ回路において、前記四端子二重絶縁ゲート電界効果トランジスタの一方のゲートを入力端子とし、他方のゲートに抵抗の一方の端を接続し、ソースを第一の電源に接続し、ドレインを出力端子とすると供に負荷素子を通して第二の電源に接続し、前記抵抗の他端を一定電位の第三の電源に接続する。

(もっと読む)

バッファ回路

【課題】出力トランジスタのオンオフを切り替えるタイミングを制御して、出力信号が受ける外部環境の影響を抑制し、出力特性を安定にすることが可能なバッファ回路を提供すること。

【解決手段】出力用PチャネルMOSトランジスタと、出力用NチャネルMOSトランジスタと、出力用PチャネルMOSトランジスタを駆動するPチャネル駆動部と、出力用NチャネルMOSトランジスタを駆動するNチャネル駆動部と、出力用PチャネルMOSトランジスタのゲート電圧が閾値電圧を超過したことを検出するPチャネル検出部と、出力用NチャネルMOSトランジスタのゲート電圧が閾値電圧を超過したことを検出するNチャネル検出部と、出力用PチャネルMOSトランジスタをオン状態に制御するPチャネル制御部と、出力用NチャネルMOSトランジスタをオン状態に制御するNチャネル制御部と、を備える構成とする。

(もっと読む)

出力バッファ回路及び半導体装置

【課題】インピーダンスコードを更新して出力インピーダンスの調整を行う際、インピーダンスコードの更新に影響されない安定した出力を得ることが可能な出力バッファ回路及び半導体装置を提供すること。

【解決手段】pチャネルMOSFET及びnチャネルMOSFETを備える複数のドライバ回路が並列に接続されたバッファ部を備え、ドライバ回路の動作数により出力インピーダンスを調整するためのインピーダンスコードが供給される出力バッファ回路において、ドライバ回路のドライブ状態を示す状態情報信号に応じて、システムクロックに同期して、pチャネルMOSFET及びnチャネルMOSFETに対してインピーダンスコードを更新するコード更新制御回路を備える構成とする。

(もっと読む)

出力バッファ回路

【課題】伝送路にノイズが入った場合でも正常に通信ができる通信装置を提供する。

【解決手段】帰還増幅回路(2)と、帰還増幅回路(2)から供給される内部信号に応答して出力ノード(N1)に外部出力信号を供給する出力回路(3)と、帰還増幅回路(2)に対する帰還信号の供給を禁止する帰還遮断回路(4)とを具備する出力バッファ回路(1)を構成する。ここで、帰還増幅回路(2)は、入力端(N2)に入力される送信信号(TXD)と外部出力信号を帰還した帰還信号とに基づいて、内部信号の波形を制御する。そして、帰還遮断回路(4)は、出力ノード(N1)のノイズに基づいて生成される帰還遮断命令に応答して、帰還増幅回路(2)への帰還信号の供給を禁止する。

(もっと読む)

81 - 90 / 203

[ Back to top ]