国際特許分類[H03K19/0944]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 論理回路,すなわち,1出力に作用する少なくとも2入力を持つもの;反転回路 (4,821) | 特定の構成要素を用いるもの (1,730) | 半導体装置を用いるもの (1,065) | 電界効果トランジスタを用いるもの (1,019) | MOSFETを用いるもの (616)

国際特許分類[H03K19/0944]の下位に属する分類

CMOSを用いるもの (413)

国際特許分類[H03K19/0944]に分類される特許

41 - 50 / 203

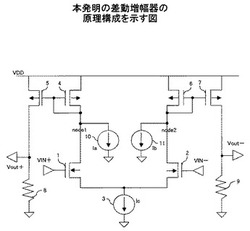

差動増幅器

【課題】負荷側に出力を電流で受け渡すカレントミラー回路を備える差動増幅器の動作を高速化する。

【解決手段】差動増幅器を構成し、差動増幅器に対する2つの入力の内のそれぞれ1つが与えられる各トランジスタの端子の内で、差動増幅器の出力点となりうるそれぞれの端子の間に接続される回路素子を備える差動増幅器は、カレントミラー回路においてモニタ電流が流れるトランジスタに接続されるとともに、カレントミラー回路においてコピー電流が流れる第1のトランジスタと、前記出力が受け渡される負荷としての抵抗との間に接続される前記2つの入力のうちいずれか1つが与えられるトランジスタへの入力がLの時にオフとなる第2のトランジスタと、第1のトランジスタと第2のトランジスタとの接続点とアースとの間に接続される電流源とをさらに備えることにより、上記課題の解決を図る。

(もっと読む)

消費電力錯乱型論理回路及び情報記憶媒体

【課題】入力信号の組合せにより充電経路の平均数が異なるため、及び後段のゲートの動作タイミングが異なるために生じる電力消費波形の変化を低減する。

【解決手段】論理回路1は、入力信号X、Yと乱数信号rとに基づいて生成される出力論理状態を出力線Z1に出力する論理演算回路10と、制御信号en1に応じて出力線Z1の出力状態を制御し、論理演算回路10の出力論理状態を無効とする出力無効状態である場合に、出力線Z1から電源線VDDに通じる経路を遮断し、電源線VDDの電位により出力線Z1を充電する出力制御部20と、出力線Z1の出力状態に基づいて出力する状態を無効とするマスク状態に、制御信号en2に応じて切り替える出力段回路30とを備える。

(もっと読む)

半導体集積回路装置

【課題】入力容量および雑音を小さくした半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置は、入力信号が入力される入力端子と出力信号が出力される出力端子とを有する増幅器と、バイアス電流を生成する第1のトランジスタを有し、前記バイアス電流により動作し、前記出力信号を入力してフィードバック信号を前記入力端子に供給するフィードバック回路と、を備え、前記第1のトランジスタのゲートに、前記出力信号とは逆相の信号が入力されることを特徴とする。

(もっと読む)

半導体スイッチ及び無線機器

【課題】オフ歪みを低減した半導体スイッチを提供する。

【解決手段】負の第1の電位を生成する電圧生成回路と、外部から入力される端子切替信号に応じて前記第1の電位を変化させる電圧制御回路と、電源電圧または電源電圧よりも高い正の第2の電位と前記第1の電位とが供給され、前記端子切替信号を入力し前記端子切替信号に基づいて前記第1の電位及び前記第2の電位の少なくとも一方を出力する駆動回路と、SOI基板に設けられ、前記駆動回路の出力により端子間の接続を切り替えるスイッチ部と、を備えたことを特徴とする半導体スイッチが提供される。

(もっと読む)

デューティサイクル補正を行う方法

【課題】不均一なデューティサイクルを有する入力信号のデューティサイクル補正を行う方法を提供する。

【解決手段】不均一なデューティサイクルを有する入力信号をコンデンサ・デジェネレイティング差動対回路に入力し、前記回路内の1つ以上のコンデンサの両端に、前記入力信号のデューティサイクルの正の部分と負の部分との継続時間の差を表わす直流電圧を形成し、差動対回路のスイッチング動作を通じてデューティサイクルを有する出力信号を形成し、それによって出力信号のデューティサイクルの正の部分と負の部分の継続時間が、入力信号とスイッチングレベルとの交差点により規定される。必要に応じて、出力信号のデューティサイクルが少なくとも実質的に均一になるまで、信号(およびスイッチングレベル)が調整される。

(もっと読む)

半導体回路、及びコンピュータシステム

【課題】半導体素子の製造ばらつきや動作環境による特性変動の影響を低減し、安定した動作を可能にする半導体回路、及びコンピュータシステムを提供することにある。

【解決手段】降圧回路100は、制御電圧Vrefが供給されるNMOSトランジスタ101が電流源として駆動するカレントミラー回路20が、制御電圧Vrefに応じて出力電圧を変化させるNMOSトランジスタ102を駆動し、更に、補償回路30は、NMOSトランジスタ101と102の特性変動によって生じる降圧電位VDDIの変動を低減する。

(もっと読む)

プリエンファシス機能を含む出力回路と半導体装置

【課題】プリエンファシス機能を有する出力回路において、デエンファシス時における差動出力信号のコモンモード電圧のプリエンファシス時のコモンモード電圧からの変動を抑制する。

【解決手段】入力信号とその相補信号とを差動入力して差動出力し、差動出力信号のうち高電位側の出力信号にデエンファシスをかける際に、当該デエンファシス電流を供給するトランジスタ(N3、N4)に流れる電流を絞る回路(N5、N6、R3)を備え、デエンファシス時の前記出力信号のハイレベルの前記出力信号のプリエンファシス時のハイレベルからの変化量を縮減させ、デエンファシス時の前記差動出力信号のコモンモード電圧をプリエンファシス時のコモンモード電圧に近づける。

(もっと読む)

送信ドライバ回路

【課題】フリーホイールダイオードを用いることなく、より低い電圧のアンダーシュートでも低減できる送信ドライバ回路を提供する。

【解決手段】PチャネルMOSFET22のドレインをグランドに接続して、NチャネルMOSFET21,PチャネルMOSFET22のソースをそれぞれ信号線3H,3Lに接続する。第1データ電圧設定部41は、信号出力部がハイレベル信号を出力すると、ゲート21G,22G間の電位差を(2・R1・Iref)にする電圧信号を設定し、第2データ電圧設定部42は、信号出力部がロウレベル信号を出力すると、ゲート21G,22G間の電位差をゼロにする電圧信号を設定する。これらの作用により、伝送線路3を構成する信号線3H,3L間の電圧を変化させて差動信号を伝送する。

(もっと読む)

複数の集積回路にインタフェース信号を供給する方法および回路

【課題】複数の集積回路間にインタフェース信号を供給する方法を提供する。

【解決手段】第1および第2の集積回路(IC)間にインタフェース信号を発生する回路で、基準信号を供給する基準回路と、インタフェース回路と、回路要素とを含む。インタフェース回路は、第1のICに実装され、作動するように基準回路に結合し、基準信号およびデータ入力を受信し、インタフェース信号を発生する。回路要素は、第2のICに実装され、作動するように制御回路に結合し、インタフェース信号を受信し、出力信号を供給する。基準信号は、電圧あるいは電流信号であってもよく、第1あるいは第2のICで発生できる。インタフェース回路は、スイッチアレイに結合される電流ミラーで実装でき、フィルタリング要求を容易にするために過サンプリングできる。

(もっと読む)

半導体集積回路

【課題】固定電位と入力信号を比較するカレントミラー型差動増幅器において、入力信号の立ち下り時に出力信号の遷移の遅れを改善して入力信号の立ち上がり時と立ち下がり時で出力信号の遷移時間差を少なくする。

【解決手段】カレントミラー型差動増幅器1-1 のミラートランジスタの共通ゲート端子のノードGPと定電流源回路TNCSの一端との間に、差動増幅器の出力信号OUTnをゲート入力とするトランジスタTNK1と、差動増幅回路の出力信号とは逆の論理の信号OUTpをゲート入力とするトランジスタTNK2とを直列に接続する。

(もっと読む)

41 - 50 / 203

[ Back to top ]