国際特許分類[H03K19/0944]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 論理回路,すなわち,1出力に作用する少なくとも2入力を持つもの;反転回路 (4,821) | 特定の構成要素を用いるもの (1,730) | 半導体装置を用いるもの (1,065) | 電界効果トランジスタを用いるもの (1,019) | MOSFETを用いるもの (616)

国際特許分類[H03K19/0944]の下位に属する分類

CMOSを用いるもの (413)

国際特許分類[H03K19/0944]に分類される特許

11 - 20 / 203

加算器

【課題】新たなロジックインメモリ構造を提供する。また、より消費電力の低い信号処理回路を提供する。また、より消費電力の低い電子機器を提供する。

【解決手段】オフ電流の低いトランジスタを用いて記憶素子を構成することで、記憶機能と演算機能を組み合わせた回路を提供する。オフ電流の低いトランジスタを用いることで、オフ電流の低いトランジスタのソースまたはドレインの一方と、他のトランジスタのゲートとの間などに電荷を保持することができる。そのため、オフ電流の低いトランジスタのソース又はドレインの一方と、他のトランジスタのゲートと、の間のノード等を記憶素子として用いることができる。また、加算器の動作に伴うリーク電流を著しく低減することができる。これにより、消費電力の低い信号処理回路を構築することが可能である。

(もっと読む)

半導体装置

【課題】InやZnなどを含む酸化物半導体をチャネル領域に用いたトランジスタを、P型トランジスタのように駆動できる半導体装置を提供する。

【解決手段】トランジスタとインバータを有し、インバータの出力はトランジスタのゲートに入力され、トランジスタのチャネル領域はIn、Zn若しくはSnを含む酸化物半導体膜を有し、インバータを構成するトランジスタのチャネル領域はシリコンを有し、インバータにハイ電圧を入力すると、インバータからロー電圧が出力されるとともにトランジスタのゲートにロー電圧が入力されてトランジスタはオフし、インバータにロー電圧を入力すると、インバータからハイ電圧が出力されるとともにトランジスタのゲートにハイ電圧が入力されてトランジスタはオンする半導体装置によって解決する。

(もっと読む)

半導体集積回路

【課題】効果的に雑音レベルを低減した半導体集積回路を提供する。

【解決手段】差動入力トランジスタであるPチャネル型MOSトランジスタM1,M2は、雑音レベルを低減するために薄いゲート酸化膜を有している。これらのPチャネル型MOSトランジスタM1,M2を過電圧から保護する保護回路は、Pチャネル型MOSトランジスタM3,M4を含んで構成されている。Pチャネル型MOSトランジスタM3はPチャネル型MOSトランジスタM1を過電圧から保護する第1の保護トランジスタであり、Pチャネル型MOSトランジスタM1のドレイン側に直列に接続されている。Pチャネル型MOSトランジスタM4は、Pチャネル型MOSトランジスタM2を過電圧から保護する第2の保護トランジスタであり、Pチャネル型MOSトランジスタM2のドレイン側に直列に接続されている。

(もっと読む)

イネーブル信号生成回路

【課題】後段のイネーブル回路を確実に制御し、また電源電圧が高くなっても消費電流が増大しないようにする。

【解決手段】制御入力端子1にゲートが接続されソースがトランジスタMN2を介して接地に接続されたトランジスタMN1と、トランジスタMN1のドレインと電源VDDとの間に接続された抵抗R2と、抵抗R2の両端にソースとドレインが接続されたトランジスタMP1と、トランジスタのMP1ゲートとソース間に接続された抵抗R3と、ソースがトランジスタMP1のゲートに接続されゲートがトランジスタMP1のドレインに接続されドレインが負荷回路3に接続されたトランジスタMP2とを備え、トランジスタMP2のゲートを制御出力端子2に接続した。

(もっと読む)

記憶回路

【課題】消費電力を抑えることができる記憶回路の提供を目的の一つとする。

【解決手段】記憶回路に電源が供給されない間は、揮発性のメモリに相当する記憶部に記憶されていたデータを、不揮発性のメモリに相当する記憶部に設けられた容量素子によって保持する記憶回路である。不揮発性記憶部では、酸化物半導体層にチャネルが形成されるトランジスタを用いることによって、容量素子に保持された信号は長期間にわたり保持することができる。こうして、記憶回路は電源の供給が停止している間も論理状態(データ信号)を保持することが可能である。また酸化物半導体層にチャネルが形成されるトランジスタのゲートに印加する電位を、電源電位を供給する配線と前記トランジスタのゲートとの間に設けられた昇圧回路によって高くすることで、1つの電源電位であっても誤動作なくデータ信号の保持を行うことが可能である。

(もっと読む)

半導体装置

【課題】トランジスタが仮にディプレッション型である場合でも、安定して動作することができる半導体装置を提供する。

【解決手段】開示する発明の一態様の半導体装置は、第1の電位を第1の配線に供給する機能を有する第1のトランジスタと、第2の電位を第1の配線に供給する機能を有する第2のトランジスタと、第1のトランジスタのゲートに第1のトランジスタがオンをオンにするための第3の電位を供給した後、第3の電位の供給を止める機能を有する第3のトランジスタと、第2の電位を第1のトランジスタのゲートに供給する機能を有する第4のトランジスタと、第1の信号にオフセットを施した第2の信号を生成する機能を有する第1の回路と、を有し、第4のトランジスタのゲートには、第2の信号が入力され、第2の信号の最小値は、第2の電位未満の値である。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】消費電力を抑えることができる、プログラムユニットを用いた半導体装置を提供する。また、信頼性の高い、プログラムユニットを用いた半導体装置を提供する。さらに集積度の高い、プログラムユニットを用いた半導体装置を提供する。

【解決手段】PLD等のロジックセル間の接続構造を変更する機能を有する半導体回路において、ロジックセル間を接続や切断、あるいはロジックセルへの電源の供給を、オフ電流またはリーク電流が小さい絶縁ゲート電界効果型トランジスタを用いたプログラムユニットによって制御する。プログラムユニットにはトランスファーゲート回路を設けてもよい。駆動電圧を下げるため、プログラムユニットには容量素子を設けて、その電位をコンフィギュレーション時と動作期間とで異なるものとしてもよい。

(もっと読む)

論理回路および半導体装置

【課題】微細化に適し、且つ演算処理を行う各種論理回路において、演算処理を実行中に電源をオフする場合でも、電源をオフする直前に入力された電位を保持できる論理回路を提供することである。また、該論理回路を有する半導体装置を提供することである。

【解決手段】入力端子および出力端子と、入力端子および出力端子に電気的に接続された主要論理回路部と、入力端子および主要論理回路部に電気的に接続されたスイッチング素子を有し、スイッチング素子の第1端子は入力端子と電気的に接続されており、スイッチング素子の第2端子は主要論理回路を構成する1以上のトランジスタのゲートと電気的に接続されており、スイッチング素子は、オフ状態におけるリーク電流がチャネル幅1μmあたり1×10−17A以下のトランジスタとする論理回路である。また、このような論理回路を有する半導体装置である。

(もっと読む)

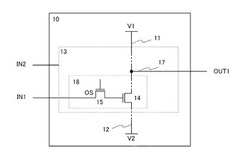

インバータ回路および表示装置

【課題】消費電力を抑えることの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】入力端子IN1から印加される電圧に応じてオンオフするトランジスタT3を介して、入力電圧Vin2がトランジスタT2のゲートに入力される。そのため、入力電圧Vin1,Vin2がともにハイとなったときだけ、トランジスタT1,T2の双方のゲートにオン電圧が印加される。

(もっと読む)

半導体装置

【課題】出力回路のSSN(Simultaneous Switching Noise)の振動ノイズの低減を可能とする半導体装置の提供。

【解決手段】第1及び第2の電源線と、前記第1の電源線VDDQと前記第2の電源線VSSQとの間に配置された出力回路12と、前記第1の電源線と前記第2の電源線との間に配置されたノイズキャンセル回路13とを備え、前記ノイズキャンセル回路13は、前記出力回路の前記出力ノードの論理レベルへの切り替え時に発生する所定の周期で指数関数的に減衰振動する電源ノイズに対して、前記電源に、前記振動から半周期分遅れ、前記振動と逆向きに減衰振動する電源ノイズを発生し、互いに打ち消し合わせる。

(もっと読む)

11 - 20 / 203

[ Back to top ]