国際特許分類[H03K19/0944]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 論理回路,すなわち,1出力に作用する少なくとも2入力を持つもの;反転回路 (4,821) | 特定の構成要素を用いるもの (1,730) | 半導体装置を用いるもの (1,065) | 電界効果トランジスタを用いるもの (1,019) | MOSFETを用いるもの (616)

国際特許分類[H03K19/0944]の下位に属する分類

CMOSを用いるもの (413)

国際特許分類[H03K19/0944]に分類される特許

21 - 30 / 203

半導体装置

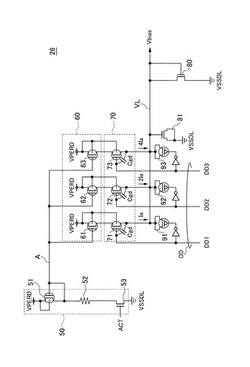

【課題】切り替えスイッチのオンオフに伴うノイズがバイアスラインに重畳するのを防ぐ。

【解決手段】バイアス電流が流れるバイアスラインVLと、バイアス電流の量を制御信号DDに基づいて切り替える切り替えスイッチ70と、制御信号DDが供給される制御ラインとバイアスラインVLとの間の寄生容量を介して制御信号DDの変化時に生じるバイアスラインVLの電位変動を相殺する相殺回路91〜93とを備える。本発明によれば、切り替えスイッチ70のオンオフに伴ってバイアスラインVLに生じるノイズを相殺することが可能となる。

(もっと読む)

ラッチ回路、CDR回路、および受信装置

【課題】 消費電力を抑えた受信回路を提供する。

【解決手段】 本発明では、差動信号を差動増幅させる際に、差動入力によって発生する電流を対となる差動出力により遮断することで差動信号をラッチする回路を提供する。該ラッチ回路の適用により、受信信号の差動信号電圧差が小さい場合でも伝送データを受信できる為、増幅用アンプの削減が可能となり、受信装置の消費電力の低減を図ることができる。

(もっと読む)

多入力差動増幅器

【課題】各動作モードにおいてレベルシフト回路を用いることなく所望の入力電圧範囲となる多入力差動増幅器を提供する。

【解決手段】差動部1は、バイアス部2と出力部3との間に設けられ、第一入力部10と第二入力部20とを有する。第一入力部10は、ソースがバイアス部2と接続され、ドレインが出力部3と接続された1個のn型MOSFET(M11)からなる。第二入力部20は、直列接続される2個のn型MOSFET(M21)、(M22)と、直列接続される2個のn型MOSFET(M23)、(M24)とが2列に並列接続される。また、入力端INaはM11のゲートに接続され、入力端INxはM22とM23のゲートに接続され、入力端INyはM21とM24のゲートに接続される。バイアス部2は1つの定電流源21を有し、出力部3は2つのp型MOSFET(Q1、Q2)で構成のカレントミラー回路を有する。

(もっと読む)

反転電圧出力回路

【課題】入力信号の変化に応じて直流電源の非接地電圧と接地電圧の間で反転する電圧を出力する回路であり、非接地端子に接続されている電源線に生じる電圧変動を抑制する。

【解決手段】電流制限素子14とスイッチング回路16が直列に接続されており、電流制限素子とスイッチング回路の中間点22の電圧を出力する。スイッチング回路の導通時にスイッチング回路を流れる電流が電流制限素子によって制限される。直流電源の非接地端子に接続されている電源線12に生じる電圧変動が抑制され、電源線12に接続されているアナログ回路等の動作が安定する。

(もっと読む)

半導体装置およびその検査方法

【課題】本発明の実施形態は、高周波スイッチ回路の高周波特性の良否を簡便に判定することができる半導体装置およびその検査方法を提供する。

【解決手段】実施形態に係る半導体装置は、複数の高周波端子と、共通高周波端子と、の間の信号経路を、前記高周波端子と前記共通高周波端子との間に直列に設けられた複数のFETにより切り替える高周波スイッチ回路を有する半導体装置であって、前記共通高周波端子に接続された複数のFETを含む半導体スイッチと、前記半導体スイッチを介して前記共通高周波端子に接続された発振回路と、前記発振回路の出力を入力とする検波回路と、前記検波回路の出力端子と、を備える。

(もっと読む)

セレクタ回路、プロセッサシステム

【課題】本実施例におけるセレクタ回路は、所定ノードに対する充電と放電により入力信号の選択動作を行う前段の選択回路において余計な消費電流が生じるのを防止し、回路の消費電力を低減することを目的とする。

【解決手段】本実施例におけるセレクタ回路は、第1選択制御信号に基づいて複数の入力信号のうちの1つを選択して第1出力信号を出力する複数の第1選択回路と、第2選択制御信号に基づいて複数の第1出力信号のうちの1つを選択して出力する第2選択回路を含み、第1選択回路の各々が、第1期間に第1ノードと第1電源を電気的に接続して第1ノードを充電する充電回路と、第1ノードと第2電源の間に設けられ、第1期間の後に続く第2期間に第1選択制御信号、複数の入力信号及び第2選択制御信号に基づいて、第1ノードと第2電源を電気的に接続して、充電された第1ノードを放電させる否かを制御する放電制御回路を含むことを特徴とする。

(もっと読む)

スイッチングトランジスタの制御回路

【課題】イネーブル信号をHIGHにしてから急速にスイッチングトランジスタをオンし、かつ突入電流を防止することが可能なスイッチングトランジスタの制御回路を提供すること。

【解決手段】イネーブル信号によりトランジスタM2はオフする。トランジスタM8はオフし、ノードCTの電位はグラウンドと等電位になり、反転器の出力ACTはHIGHとなり、トランジスタM9はオンする。イネーブル信号の反転信号によりトランジスタM5はオフし、トランジスタM3、M4、M6のゲート電位はM4とIBIASで決まる電位VBIASと等電位となってトランジスタM3、M4、M6はオンとなり、並列接続されたトランジスタM3、M6の能力に応じたIGD(大)が流れる。トランジスタM1、M7は、電流IGD(大)によって急速にゲート容量へ電荷が蓄えられて急速にオンになり、電流IOUT、IDETが流れる。

(もっと読む)

半導体装置のトリミング方法、及びトリミング制御回路

【課題】スイッチ素子の製造バラツキを排除し、より均一で確実な溶断が行える半導体装置のトリミング方法、及びトリミング制御回路を提供すること。

【解決手段】電位が異なる第1電源(電源端子c)と第2電源(接地端子d)との間にて直列接続された第1スイッチ素子S1〜S3およびフューズF1〜F3を内蔵した半導体装置101における第1スイッチ素子S1〜S3をオン制御することでフューズF1〜F3に電圧を印加してフューズF1〜F3を溶断する半導体装置101のトリミング方法であって、第1スイッチ素子S1〜S3をターンオン制御することにより、第1電源(電源端子c)からフューズF1〜F3を溶断させない第1電圧値を所定時間印加するステップと、第1電圧値の印加が完了した後、第1電源(電源端子c)からフューズF1〜F3を溶断させる第2電圧値を印加するように切り替えるステップと、を含む。

(もっと読む)

電源検知回路

【課題】電源検知回路において、BT劣化によって比較回路のミスマッチが増大することに起因する電源検知信号の精度の劣化を抑制する。

【解決手段】検知用比較回路104は、入力切替信号生成回路112によって、その出力の活性状態と非活性状態との切替時付近では、入力信号102と基準電圧103とを入力して、その両者の比較を行う。一方、前記切替時付近以外では、比較回路非使用時入力電圧110が検知用比較回路104に入力されて、その差動入力が同電位に固定される。従って、BT劣化による電源検知精度の経年劣化が有効に抑制される。

(もっと読む)

半導体装置

【課題】小型化、低電圧・低電力化ならびに高速化が可能なセンスアンプを提供する。

【解決手段】増幅作用をする交差結合された第1のMOSトランジスタと第2のMOSトランジスタのそれぞれのソースに直列に第3のMOSトランジスタと第4のMOSトランジスタを接続し、第3及び第4のMOSトランジスタの電流供給能力を第3及び第4のMOSトランジスタの制御電極に与える制御電圧で制御する。データ保持期間において、制御電圧により第3及び第4のMOSトランジスタに、データ保持に必要な最小限のサブスレッショルド電流を流し、ビット線電位を保持する。

(もっと読む)

21 - 30 / 203

[ Back to top ]