国際特許分類[H03K19/0948]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 論理回路,すなわち,1出力に作用する少なくとも2入力を持つもの;反転回路 (4,821) | 特定の構成要素を用いるもの (1,730) | 半導体装置を用いるもの (1,065) | 電界効果トランジスタを用いるもの (1,019) | MOSFETを用いるもの (616) | CMOSを用いるもの (413)

国際特許分類[H03K19/0948]に分類される特許

51 - 60 / 413

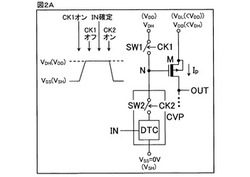

CMOS回路及び半導体装置

【課題】しきい電圧VTが小さくてもリーク電流が小さく、また高速にかつ小さな電圧振幅で動作するCMOS回路さらには半導体装置を提供することである。

【解決手段】ゲートとソースを等しい電圧にしたときにドレインとソース間に実質的にサブスレショルド電流が流れるようなMOST(M)を含む出力段回路において、その非活性時には、前記MOST(M)のゲートとソース間を逆バイアスするように該MOST(M)のゲートに電圧を印加する。すなわち、MOST(M)がpチャンネル型の場合にはp型のソースに比べて高い電圧をゲートに印加し、また、MOST(M)がnチャンネル型の場合にはn型のソースに比べて低い電圧をゲートに印加する。活性時には、入力電圧に応じて該逆バイアス状態を保持するかあるいは順バイアス状態に制御する。

(もっと読む)

半導体装置およびその制御方法

【課題】半導体装置のデータ入力回路における消費電力を削減すること。

【解決手段】半導体装置は、クロック信号の立ち上がりエッジおよび立ち下がりエッジの少なくともいずれか一方の近傍の期間において活性状態となる制御信号を生成して出力する制御信号生成回路と、制御信号が活性状態である期間においてデータ信号を受信可能な活性状態となり、それ以外の期間において非活性状態となるデータ入力回路と、を備えている。

(もっと読む)

スイッチ回路装置

【課題】従来技術によるスイッチ回路装置では、ドライバ回路がアンテナ端子とポートとの間に振幅の大きい高周波信号を入力した際に、ドライバ回路内部でリーク電流が発生し、スイッチ回路装置の消費電力が増大する、という問題がある。

【解決手段】ドライバ回路の出力部に、リーク電流抑制回路部を設ける。本発明のスイッチ回路装置によれば、リーク電流抑制回路部が高周波信号の侵入を抑制するので、ドライバ回路は出力状態を保持することが出来て、リーク電流の問題が解決される。

(もっと読む)

リーク電流低減回路

【課題】 間欠動作する論理回路の動作停止時(待機時)のリーク電流を低減するとともに、さらに論理回路の動作時の駆動電流を十分に供給可能とする。

【解決手段】 論理回路と電源の間に接続のパワースイッチを論理回路の間欠動作に合わせて制御する構成において、2つのパワースイッチは論理回路と正の電源電位との間にnMOSトランジスタを接続し、論理回路と接地電位との間にpMOSトランジスタを接続した構成とし、論理回路の動作停止時にpMOSトランジスタのゲート端子を正の電源電位に接続して非導通とし、論理回路の動作時にpMOSトランジスタのゲート電位を接地電位に接続して導通させるスイッチを備え、論理回路の動作停止時にnMOSトランジスタのゲート端子を接地電位に設定して非導通とし、論理回路の動作時にnMOSトランジスタのゲート端子を正の電源電位以上の電位に設定して導通させる電圧変換器を備える。

(もっと読む)

半導体デバイス回路

【課題】MTCMOS回路を用いた半導体デバイス回路において、アクセススピードを損なわず、スタンバイ電流が少なく、スタンバイ状態からの復帰が早い半導体デバイス回路を提供する。

【解決手段】第1のPMOSFETと第1のNMOSFETとを含む機能回路を備えた半導体デバイス回路において、アクティブモード時に第1のPMOSFETを電源電圧源に接続し、スタンバイモード時に電源電圧源に接続しないように制御する第2のPMOSFETと、アクティブモード時に第1のNMOSFETを接地側電圧源に接続し、スタンバイモード時に接地側電圧源に接続しないように制御する第2のNMOSFETと、電源電圧源に接続されかつ第1のPMOSFETに並列に接続されその出力信号を保持する第3のPMOSFETと、接地側電圧源に接続されかつ第1のNMOSFETに並列に接続されその出力信号を保持する第3のNMOSFETとを備えた。

(もっと読む)

二段電圧レベルシフト

【課題】追加の大きなハードウェア要件なしに、ブースト電圧レベルを提供できるようにする。

【解決手段】第1の電圧レベルから第2の電圧レベルに、次に追加のブーストされた第2の電圧レベルに出力信号をシフトするための電圧レベルシフタが開示される。電圧レベルシフタは、入力信号を受信するための入力、出力信号を出力するための出力、前記第1の電圧レベルを供給する第1の電圧源に接続するための第1のパワーサプライ入力、前記第2の電圧レベルを供給する第2の電圧源に接続するための第2のパワーサプライ入力、前記ブーストされた第2の電圧レベルを供給する第3の電圧源に接続するための第3のパワーサプライ入力を含み、前記電圧レベルシフタは、前記出力から前記第1のパワーサプライ入力を隔離するため、及び前記出力に前記第2のパワーサプライ入力を接続するために前記入力信号の所定の変化に応える。

(もっと読む)

半導体装置

【課題】外部電圧が変動したときにも半導体装置の動作安定性を維持する。

【解決手段】入力信号判定部116は、第1電流源122から供給される電源電位によって動作する。入力信号判定部116は、入力信号VINと参照電位Vrefを比較する。比較結果はインバータINV1により反転され、出力信号V0となる。電源センサ回路120は、第1の電源ラインVDDIの電位を監視する。外部電位VDDIが基準電位VXよりも低くなると、電源センサ回路120は第2電流源124をオンする。第2電流源124がオンされると、判定部126には、第1電流源122に加えて第2電流源124からも動作電流が供給される。

(もっと読む)

通信信号生成装置及び通信装置

【課題】集積回路の実装面積を抑えつつ通信信号の通信波形のリンギングを抑制する。

【解決手段】トランスミッタ130において、出力バッファ制御信号生成部131は、トランジスタ132a〜132d,133a〜133dをすべてオンにして第1通信線11及び第2通信線12に電流を流すことによりドミナントを表す通信信号を生成し、トランジスタ132a〜132d,133a〜133dをすべてオフにして第1通信線11及び第2通信線12に電流を流さないことによりレセッシブを表す通信信号を生成する。そして、出力バッファ制御信号生成部131は、ドミナントを表す通信信号の1ビット時間において、トランジスタ132a〜132d,133a〜133dを順にオフにして出力バッファ(第1のトランジスタ群132及び第2のトランジスタ群133)の各インピーダンスを徐々に高くする。

(もっと読む)

トランスミッタ、インタフェイス装置、車載通信システム

【課題】電源電圧の変動に起因する入力信号と出力信号のデューティばらつきを抑制する。

【解決手段】トランスミッタ10は、一端から充電電圧Vaが引き出されるコンデンサ105と、コンデンサ105の充電電流I1を生成する第1定電流源103と、コンデンサ103の放電電流I2を生成する第2定電流源104と、送信入力信号INの論理レベル、及び、充電電圧Vaと基準電圧Vrefとの比較結果に基づいて、コンデンサ105の充放電制御を行う充放電制御部(101、102、106)と、充電電圧Vaに応じてスルーレートが設定され、出力側電源電圧V2に応じて信号振幅が設定される送信出力信号OUTを生成する出力段(109〜116)と、出力側電源電圧V2に依存して基準電圧Vrefを変動させる基準電圧生成部107と、基準電圧Vrefに依存して充電電流I1及び放電電流I2の各電流値を変動させる定電流制御部108と、を有する。

(もっと読む)

半導体装置、電源スイッチの制御方法及びその設計方法

【課題】従来の半導体装置では、電源制御領域への突入電流の発生を抑制するためにチップ面積が増大する問題があった。

【解決手段】本発明にかかる半導体装置は、オン抵抗が大きな第1のスイッチトランジスタSWLと、オン抵抗が小さな第2のスイッチトランジスタSWSと、を有し、第1、第2のスイッチトランジスタSWL、SWSは、異なる領域に電流を供給し、第1のスイッチトランジスタSWSは、制御信号CONTを直列的に伝搬するように直列に接続され、第2のスイッチトランジスタSWLは、前記制御信号を直列的に伝搬するように直列に接続され、第2のスイッチトランジスタSWLのうち初段に配置される第2のスイッチトランジスタSWLは、第1のスイッチトランジスタSWSのうち最も後ろに配置される第1のスイッチトランジスタSWSが出力する制御信号CONTが入力される。

(もっと読む)

51 - 60 / 413

[ Back to top ]