国際特許分類[H03K19/0948]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 論理回路,すなわち,1出力に作用する少なくとも2入力を持つもの;反転回路 (4,821) | 特定の構成要素を用いるもの (1,730) | 半導体装置を用いるもの (1,065) | 電界効果トランジスタを用いるもの (1,019) | MOSFETを用いるもの (616) | CMOSを用いるもの (413)

国際特許分類[H03K19/0948]に分類される特許

41 - 50 / 413

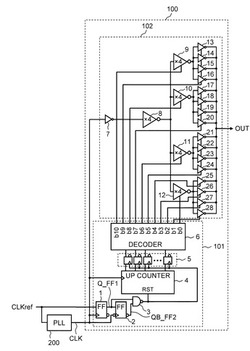

クロックバッファ回路及びクロック分配回路

【課題】クロック源の消費電力を増大させることなく、動作クロック周波数に応じて駆動能力を変化させることにより消費電力低減可能なクロックバッファ回路を提供すること。

【解決手段】クロック信号を伝達するバッファ部102と、クロック信号の参照クロック信号に対する逓倍数をカウントし、バッファ部102に対して逓倍数に基づいたイネーブル信号を出力する駆動能力切替部101と、を備え、バッファ部102は、当該バッファ部102の入力に接続された入力インバータ7と、イネーブル信号によりオンオフが可能であって、それぞれの出力が当該バッファ部の出力に共通に接続された複数の出力インバータ13〜28と、を備え、入力インバータ7が1個のCMOSインバータからなるクロックバッファ回路。

(もっと読む)

半導体集積回路

【課題】

CMOS回路に中間電圧の入力信号が長時間連続して入力された場合にも貫通電流の発生を短時間にとどめることができる半導体集積回路を提供する。

【解決手段】

本発明の一実施態様に係る半導体集積回路は、入力端子と、出力端子と、ゲートが前記入力端子に接続されソースが高電位電源配線に接続された第1PMOSトランジスタ及びゲートが前記入力端子に接続されソースが低電位電源配線に接続された第1NMOSトランジスタを含み、当該第1PMOSトランジスタと当該第1NMOSトランジスタとが同時に導通しないように構成された第1CMOS回路と、入力端が前記第1CMOS回路に接続され出力端が前記出力端子に接続された第2CMOS回路と、この第2CMOS回路の出力端とと高電位電源配線及び高電位電源配線との間にそれぞれ配置された第2PMOSトランジスタと第2NMOSトランジスタと、を備える。

(もっと読む)

電気信号の伝送回路、IC、プリント配線板、機器およびシステム

【課題】CMOS伝送回路において、レシーバの動作を不安定にしたり不要輻射を放出したりするリンギングの発生を抑制した電気信号の伝送回路を提供する。

【解決手段】本発明の一態様は、CMOSドライバと伝送線とCMOSレシーバとを有する電気信号の伝送回路において、CMOSドライバのPMOS FET1と並列にアノード電極がドライバ出力端子につながれるように第1のダイオード6を接続し、CMOSドライバのNMOS FET2と並列にカソード電極がドライバ出力端子につながれるように第2のダイオード7を接続し、PMOS FET1のデバイストランスコンダクタンスと第1のダイオード6の(飽和電流)/(理想係数×熱電圧)2とが等しくなるようにし、NMOS FET2のデバイストランスコンダクタンスと第2のダイオード7の(飽和電流)/(理想係数×熱電圧)2とが等しくなるようにしたことを特徴とする電気信号の伝送回路である。

(もっと読む)

電圧発生装置

【課題】低電源電圧状態で、ビットラインプリチャージ電圧又はセルプレート電圧を安定的に駆動し、待機電流IDD2P及び動作電流を最小化すること。

【解決手段】電源電圧のハーフレベルの基準電圧を利用し、異なるレベルのバイアス信号を生成するバイアス信号生成手段と、出力端の電圧レベルに応答してプルダウン駆動信号を生成する駆動信号生成手段と、駆動信号に応答して出力端を駆動する電圧駆動手段と、出力端の電圧レベルに応じてプルアップ駆動信号/プルダウン駆動信号を生成する駆動信号生成手段と、前記プルアップ駆動信号/プルダウン駆動信号に応答して前記出力端をプルアップ駆動/プルダウン駆動するプルアップPMOSトランジスタ/プルダウンNMOSトランジスタと、第1多重化手段と、第2多重化手段とを備える半導体メモリ素子の電圧発生装置。

(もっと読む)

二重絶縁ゲート電界トランジスタを用いたMOSトランジスタ回路およびそれを用いたCMOSトランジスタ回路、SRAMセル回路、CMOS−SRAMセル回路、集積回路

【課題】単位回路の、高速動作と未使用時(注を入れる)または定常時または待機時における消費電力の減少を両立させた二重絶縁ゲート電界トランジスタを用いたMOSトランジスタ回路およびそれを用いたCMOSトランジスタ回路、SRAMセル回路、CMOS−SRAMセル回路、集積回路を提供することである。

【解決手段】四端子二重絶縁ゲート電界効果トランジスタからなるMOSトランジスタ回路において、前記四端子二重絶縁ゲート電界効果トランジスタの一方のゲートを入力端子とし、他方のゲートに抵抗の一方の端を接続し、ソースを第一の電源に接続し、ドレインを出力端子とすると供に負荷素子を通して第二の電源に接続し、前記抵抗の他端を一定電位の第三の電源に接続したことを特徴とする。

(もっと読む)

二重絶縁ゲート電界トランジスタを用いたMOSトランジスタ回路およびそれを用いたCMOSトランジスタ回路、SRAMセル回路、CMOS−SRAMセル回路、集積回路

【課題】単位回路の、高速動作と未使用時(注を入れる)または定常時または待機時における消費電力の減少を両立させた二重絶縁ゲート電界トランジスタを用いたMOSトランジスタ回路およびそれを用いたCMOSトランジスタ回路、SRAMセル回路、CMOS−SRAMセル回路、集積回路を提供することである。

【解決手段】四端子二重絶縁ゲート電界効果トランジスタからなるMOSトランジスタ回路において、前記四端子二重絶縁ゲート電界効果トランジスタの一方のゲートを入力端子とし、他方のゲートに抵抗の一方の端を接続し、ソースを第一の電源に接続し、ドレインを出力端子とすると供に負荷素子を通して第二の電源に接続し、前記抵抗の他端を一定電位の第三の電源に接続したことを特徴とする。

(もっと読む)

パワーゲーティングCMOS回路及びスーパーカットオフCMOS回路におけるチャージリサイクリング

【課題】MTCMOS回路やSCCMOS回路等のパワーゲーティングされた回路におけるモード移行時のパワー消費の低減や、ウェークアップ時間や、パワーゲーティング構成により生じるノイズを低減する。

【解決手段】第1の回路ブロックと第1のスリープトランジスタとの間の第1の仮想グラウンドノードと、第2の回路ブロックと第2のスリープトランジスタとの間の第2の仮想グラウンドノードと、第1の仮想グラウンドノードを第2の仮想グラウンドノードに接続し、第1の回路ブロックによるアクティブモードからスリープモードへの移行、及び第2の回路ブロックによるスリープモードからアクティブモードへの移行、またはその逆の間に第1の回路ブロックと第2の回路ブロックとの間のチャージリサイクリングを可能とするトランスミッションゲート(TG)またはパストランジスタとを有する回路である。

(もっと読む)

半導体回路および半導体装置

【課題】簡易な構成で電荷の再利用効率を高め、複数のLSIを搭載したシステム全体のエネルギー効率を向上することが可能な半導体回路および半導体装置を提供する。

【解決手段】入力端子20にLレベルの信号が入力されたとき、回路素子10の出力端子22に接続される信号線24の配線容量Cpに正の電荷が充電される。入力端子20にHレベルの信号が入力されたとき、NMOSトランジスタNr1は、論理素子のNMOSトランジスタN1が導通するのと同時に導通する。これにより、信号線24から放電される電荷の一部が、NMOSトランジスタNr1およびダイオードD1を介して、電荷回収線2に移動する。電荷回収線2が回収した電荷は、電荷再利用端子3を介して半導体チップ1Aの外部に放出されると、電荷再利用線30に接続された電荷回収用の容量素子Cextに蓄積される。蓄積され電荷は、他の半導体回路等の電源端子に供給される。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】複数の基準電位を要する半導体装置、及び半導体装置の駆動において、より消費電力を軽減する。

【解決手段】電源線に直列に接続された複数の抵抗素子により、電源線に供給された電位を抵抗分割し、電源線と電気的に接続するスイッチトランジスタを介して所望の分割された電位を出力する電位分割回路を有する半導体装置であり、スイッチトランジスタのドレイン端子は出力側の回路に設けられたトランジスタのゲート端子(又は容量素子の一方の端子)と電気的に接続しノードを構成する。

(もっと読む)

TDC回路

【課題】解像度が小さく測定精度が高い時間測定を行うことができるTDC回路を提供する。

【解決手段】TDC回路1は、共通の構成を有する32個の単位セル110〜1131がリング状に接続されたリング部10等を備える。単位セル11は、第1インバータ回路111,第2インバータ回路112,スイッチSW0,スイッチSW1およびスイッチSW2を含む。第1インバータ回路111のPMOSトランジスタのゲート幅は、第2インバータ回路112のPMOSトランジスタのゲート幅のαp倍である。第2インバータ回路111のNMOSトランジスタのゲート幅は、第1インバータ回路112のNMOSトランジスタのゲート幅のαn倍である。αpおよびαnの双方が1より大きいか又は双方が1より小さい。

(もっと読む)

41 - 50 / 413

[ Back to top ]