国際特許分類[H03K19/0948]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 論理回路,すなわち,1出力に作用する少なくとも2入力を持つもの;反転回路 (4,821) | 特定の構成要素を用いるもの (1,730) | 半導体装置を用いるもの (1,065) | 電界効果トランジスタを用いるもの (1,019) | MOSFETを用いるもの (616) | CMOSを用いるもの (413)

国際特許分類[H03K19/0948]に分類される特許

21 - 30 / 413

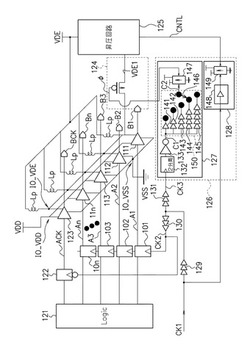

インターフェース回路

【課題】ノイズを低減することができるインターフェース回路を提供することを課題とする。

【解決手段】インターフェース回路は、電源電圧端子が第1の電源電圧ノードに接続され、入力信号を増幅する第1のバッファ(111)と、第2の電源電圧ノード及び前記第1のバッファの電源電圧端子間に接続されるスイッチ(124)と、前記第1のバッファの入力信号がローレベルからハイレベルに立ち上がると、遅延時間経過後に前記スイッチをオフからオンに切り換える第1の制御回路(127)とを有する。

(もっと読む)

スルーレートコントロール装置、スルーレートコントロール方法

【課題】クロック信号の出力バッファにおいて、クロック信号の周波数に応じたスルーレートの調整を行うことによりEMIノイズを抑制することが可能なスルーレートコントロール装置、およびスルーレートコントロール方法を提供すること。

【解決手段】変換ゲインGiに応じて、入力されるVCO入力電圧Viをクロック信号CKoに変換する電圧制御発振器15aを有するPLL回路24aと、VCO入力電圧Viおよび変換ゲインGiの各々に対して正の相関関係を有する制御電流Ibを出力する電圧電流変換器19aと、制御電流Ibに応じてドライブ電流を設定するバッファ制御回路21aと、ドライブ電流で、クロック信号CKoを出力する出力回路22aとを備える。よって、クロック信号CKoの周波数fに比例して出力回路22aのドライブ能力が大きくなる関係を有し、周波数fに応じて好適なスルーレートが決定することができる。

(もっと読む)

レベルシフト回路

【課題】伝播遅延時間を短縮する。

【解決手段】インバータINV1,INV2と、ラッチ回路1と、反転駆動回路2,3と、セレクタ4を備える。N1=VSS2、N2=VSS2、N3=VSS2、N4=VDD2のとき、入力端子INがVDD1→VSS1に変化したとき、トランジスタMP5をオンして大きな電流をVDD2からノードN1に流し高速にノードN1をVSS1→VDD2に変化させる。その後、トランジスタMP5はオフし、ノードN1はインバータINV4でVDD2に保持される。これで、N1=VDD2、N2=VDD2、N3=VDD2、N4=VSS2となる。次に入力端子INがVSS1→VDD1に変化したとき、トランジスタMN2がオンして大きな電流をノードN1からVSS2に流し高速にノードN1をVDD2→VSS2に変化させる。

(もっと読む)

制御信号発生回路およびそれを用いた半導体装置

【課題】半導体装置の制御に好適な制御信号発生回路を提供する。

【解決手段】ジョンソンカウンタ31は、フリップフロップFF1〜FF4およびゲート回路41〜44を含み、順次入力されるスタート信号ST1〜ST4に応答してそれぞれ制御信号C1〜C4を「H」レベルにした後、順次入力されるストップ信号SP1〜SP4に応答してそれぞれ制御信号C1〜C4を「L」レベルにする。したがって、多数のフリップフロップを用いることなく、所望の時間間隔で制御信号C1〜C4を順次「H」レベルにし、順次「L」レベルにすることができる。

(もっと読む)

半導体装置

【課題】高速動作が可能であり、且つ消費電力を低減することが可能な半導体装置を提供する。

【解決手段】レベルシフタ、第1のバッファ、及び第2のバッファと、第1のスイッチ及び第2のスイッチと、第1の端子、第1の端子から入力される信号の反転信号が入力される第2の端子、及び第1のスイッチ及び第2のスイッチの状態を制御するクロック信号が入力される第3の端子と、を備えるラッチ回路を有する。レベルシフタの第1の出力端子は、第1のスイッチを介して、第1のバッファ及び第2のバッファそれぞれの一の入力端子と接続し、レベルシフタの第2の出力端子は、第2のスイッチを介して、第1のバッファ及び第2のバッファそれぞれの他の入力端子と接続する。レベルシフタの第1の入力端子は、第1のバッファの出力端子と接続し、レベルシフタの第2の入力端子は、第2のバッファの出力端子と接続する。

(もっと読む)

半導体装置

【課題】半導体を用いた半導体装置として、論理回路がある。論理回路にはダイナミック論理回路とスタティック論理回路とがあり、トランジスタ等を用いて構成される。ダイナミック論理回路は情報を一定期間保持することができる。そのため、ダイナミック論理回路は、スタティック論理回路と比較して、トランジスタからのリーク電流が問題となる。

【解決手段】論理回路は、オフ電流が小さい第1のトランジスタと、ゲートが電気的に接続された第2のトランジスタと、を有し、第2のトランジスタのゲートのノードには第1のトランジスタを介して電荷が供給される。ノードに対して、第1及び第2の容量を介して電荷を供給する。電荷の状態に応じて、第2のトランジスタのオン、オフが制御される。第1のトランジスタは、チャネル形成領域に酸化物半導体を有する。

(もっと読む)

半導体装置

【課題】新たな構成の半導体装置を提供する。

【解決手段】半導体装置は、p型の第1のトランジスタ、n型の第2のトランジスタ、第3のトランジスタ及び第4のトランジスタを有する。第3のトランジスタのソース又はドレインの一方は、第1の電位を供給することができる機能を有する配線に接続され、他方は、第1のトランジスタのソース又はドレインの一方に接続される。第2のトランジスタのソース又はドレインの一方は、第1のトランジスタのソース又はドレインの他方と接続され、他方は、第4のトランジスタのソース又はドレインの一方に接続される。第4のトランジスタのソース又はドレインの他方は、第1の電位よりも低い第2の電位を供給することができる機能を有する配線に接続される。第3のトランジスタ及び第4のトランジスタのチャネル形成領域には酸化物半導体材料が用いられる。

(もっと読む)

半導体装置

【課題】貫通電流を少なくできる半導体装置を提供する。

【解決手段】データを出力する出力部を各々備えた複数の半導体チップと、出力部の各々と接続された配線と、配線を介して複数の半導体チップの各々からデータを受け付ける受付部と、を含み、出力部が順番に駆動する半導体装置にて、出力部の各々は、オン状態時の抵抗値を変更可能であり、自己の駆動開始時から自己の次に駆動を開始する出力部の駆動開始時の前のタイミングまでの第1期間の間は、オン状態時の抵抗値を第1抵抗値にしてデータを配線に出力し、第1期間が経過した時点から自己の駆動終了時までの第2期間の間は、オン状態時の抵抗値を第1抵抗値よりも大きい第2抵抗値にしてデータを配線に出力する。

(もっと読む)

半導体装置

【課題】 待機動作時のオフリーク電流を削減した論理回路を含む半導体装置を提供することを目的とする。

【解決手段】 半導体装置100は、第1の動作電圧または第1の動作電圧よりも小さい第2の動作電圧を供給する電源供給部110と、電源供給部110から第1または第2の動作電圧を受け取る低しきい値のP型トランジスタTpと、トランジスタTpと基準電位との間に接続されたN型トランジスタTnとを有し、トランジスタTp、Tnは、ゲートに入力された信号Dinに応じて出力信号Doutを生成する論理回路を構成する。電源供給部110は、通常動作時、第1の動作電圧をトランジスタTpのソースに供給し、待機動作時、第2の動作電圧をトランジスタTpのソースに供給する。第2の動作電圧は、トランジスタTp、Tnそれぞれのゲート・ソース間電圧の振幅がトランジスタTp、Tnのしきい値よりも大きくなるように設定される。

(もっと読む)

容量性スピーカ駆動回路

【課題】高音の音声信号が所定のレベル以上で所定時間以上入力されたときに、利得を低減させて高音過電流が発生することを防止する。

【解決手段】出力ドライバのパワートランジスタに流れる電流が所定時間以上にわたって所定値を超えた場合に高音過電流検出信号を発生する高音過電流検出手段と、前記高音過電流検出信号が発生されると前記プリアンプの通過周波数帯域を低くさせる通過周波数帯域切替手段とを設けた。

(もっと読む)

21 - 30 / 413

[ Back to top ]