国際特許分類[H03K19/0948]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 論理回路,すなわち,1出力に作用する少なくとも2入力を持つもの;反転回路 (4,821) | 特定の構成要素を用いるもの (1,730) | 半導体装置を用いるもの (1,065) | 電界効果トランジスタを用いるもの (1,019) | MOSFETを用いるもの (616) | CMOSを用いるもの (413)

国際特許分類[H03K19/0948]に分類される特許

31 - 40 / 413

容量性スピーカ駆動回路

【課題】高音の音声信号が所定のレベル以上で所定時間以上入力されたときに、利得を低減させて高音過電流が発生することを防止する。

【解決手段】出力ドライバのパワートランジスタに流れる電流が所定時間以上にわたって所定値を超えた場合に高音過電流検出信号を発生する高音過電流検出手段と、前記高音過電流検出信号が発生されると前記プリアンプの通過周波数帯域を低くさせる通過周波数帯域切替手段とを設けた。

(もっと読む)

出力バッファー回路

【課題】出力バッファーの面積・体積・部品点数の増加を抑制するとともに、ドライブ能力を向上させることが可能な出力バッファー回路を提供する。

【解決手段】第一駆動信号LINを伝達する第一入力経路4a、第二駆動信号RINを伝達する第二入力経路4b、第一入力経路4aと対応する第一出力バッファー6a及び第二入力経路4bと対応する第二出力バッファー6bを備える出力バッファー回路1において、入力経路切り替え手段8が、ステレオモード及びモノラルモードのうち、モノラルモードでは、第一入力経路4aと第一出力バッファー6a及び第二出力バッファー6bとを電気的に接続させ、出力経路切り替え手段10が、第一出力バッファー6a及び第二出力バッファー6bと、第一入力経路4a及び第一出力バッファー6aと対応する第一負荷2aとを、電気的に接続させる。

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えることの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】7Tr3Cで構成されるインバータ回路1において、入力端子IN1から印加される電圧に応じてオンオフするトランジスタT3と、制御素子10とを介して、入力電圧Vin2がトランジスタT2のゲートに入力される。入力電圧Vin1,Vin2がともにハイレベルの電圧Vddとなっている期間においては、入力電圧Vin3がハイレベルの電圧Vddとなっているときだけ、トランジスタT1,T2の双方のゲートにオン電圧が印加される。

(もっと読む)

半導体装置

【課題】入力信号が有する2値の電位に関わらず、正常に動作させることが可能なデジタ

ル回路の提案を課題とする。

【解決手段】半導体装置の一態様は、入力端子、容量素子、スイッチ、トランジスタ、配

線、及び出力端子を有し、前記入力端子は、前記容量素子の第1の電極に電気的に接続さ

れ、前記配線は、前記スイッチを介して前記容量素子の第2の電極に電気的に接続され、

前記トランジスタのゲートは、前記容量素子の第2の電極に電気的に接続され、前記トラ

ンジスタのソース又はドレインの一方は、前記配線に電気的に接続され、前記トランジス

タのソース又はドレインの他方は、前記配線に電気的に接続されていることを特徴とする

。

(もっと読む)

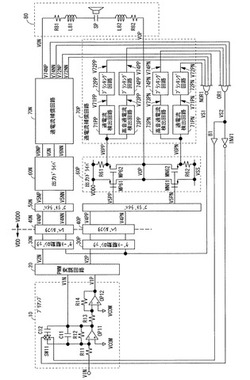

出力バッファ回路

【課題】 誘導性負荷を駆動する出力バッファ回路の電力損失を低減する。

【解決手段】 誘導性負荷2から出力バッファ回路100に電流が流入している場合、スルーレート制御部140は、出力バッファ回路100の出力信号VOUTの立ち上がり過程において低いスルーレートから高いスルーレートへ変化させる制御を行うとともに、出力信号VOUTの立ち下がり過程において高いスルーレートから低いスルーレートに変化させる制御を行う。また、出力バッファ回路100から誘導性負荷2に電流が流出している場合に、スルーレート制御部140は、出力信号VOUTの立ち上がり過程において高いスルーレートから低いスルーレートに変化させる制御を行うとともに、出力信号VOUTの立ち下がり過程において低いスルーレートから高いスルーレートに変化させる制御を行う。

(もっと読む)

信号デスキュー方法および装置

【課題】超低圧VDDデジタル回路においては、クロックスキューは厳密な時間収率の劣化を招く大きな原因であるが、コンピュータによる設計の高度な自動化(EDA)手段の様々なプロセスが存在する中でのスキュー調和がとれたクロックツリーを実現する。

【解決手段】参照信号およびローカル信号を受信し、それらを比較して位相差を検出するための位相比較器、位相差の値に関連して制御信号のオン/オフを切り替えるための制御回路、およびローカル信号バッファーを有し、前記ローカル信号バッファーはnMOSトランジスタおよび/またはpMOSトランジスタを有しており、前記制御信号に応じてホットキャリアインジェクションストレスをnMOSトランジスタまたはpMOSトランジスタに掛けてnMOSトランジスタまたはpMOSトランジスタのしきい値電圧を増加させる。

(もっと読む)

プリエンファシス回路及びこれを備えた差動電流信号伝送システム

【課題】プリエンファシス回路及びこれを備えた差動電流信号伝送システムを提供する。

【解決手段】本発明はプリエンファシス回路に関し、より詳細にはプリエンファシス回路を動作させるために必要なスイッチングトランジスタの数を減らして寄生抵抗及び寄生キャパシタを減少させ、それぞれのスイッチングトランジスタを制御するそれぞれのプリエンファシス制御信号を供給することによって望まない電流の発生を防止できるプリエンファシス回路及びこれを備えた差動電流信号伝送システムに関する。

(もっと読む)

電圧識別装置及び時計制御装置

【課題】回路規模及び消費電流の増大を抑制しながら識別対象電圧の大きさを精度良く識別することができる電圧識別装置及び時計用制御装置を提供する。

【解決手段】基準電圧生成回路12と、被印加線18並びに電圧線VSH及び接地線GNDが導通可能となるように電圧線VSHと接地線GNDとの間に挿入されると共に、被印加線18に印加された識別対象電圧の大きさに応じてスイッチングを行うスイッチング回路20を備え、被印加線18に印加された識別対象電圧の大きさと閾値とを比較することにより識別対象電圧の大きさを識別する識別回路14と、識別回路14に対して識別対象電圧の大きさを識別させる間、電圧線VSHと接地線GNDとの間に流れる電流の大きさが所定の大きさに保たれるようにスイッチング回路20と接地線GNDとの間の抵抗22を制御可能とする制御部16と、を含む。

(もっと読む)

出力回路

【課題】回路規模が小さく、出力トランジスタのしきい値電圧がばらついてもノイズを抑えつつターンオフ時間を短縮する。

【解決手段】駆動信号SdがLの時、トランジスタT1がオン、T2がオフしてVGS(T3)がほぼ電源電圧Vccに等しくなりトランジスタT3がオンする。駆動信号SdがHになるとトランジスタT1がオフ、T2がオンする。トランジスタT4がオンするので抵抗R2がバイパスされ、トランジスタT3のゲート電荷はトランジスタT4、T2を通して急速に放電する。VGS(T3)がVth(T4)+VDS(T2)よりも低下すると、トランジスタT4はオフとなり、以後はトランジスタT3のゲート電荷が抵抗R2とトランジスタT2を通して緩やかに放電する。トランジスタT3、T4のしきい値電圧は一致する傾向があるので、VGS(T3)がVTH(T3)に低下した時点でトランジスタT4をオフできる。

(もっと読む)

半導体装置

【課題】 ゲート−ソース逆バイアス駆動の動作原理を定量化し、MOSTのしきい電圧と動作電圧の関係を明らかにすることにより、逆バイアス駆動の原理を活用した複数のMOSTの組み合わせを用いて、動作電圧1V以下の高速低電圧動作を可能にする。

【解決手段】 低VtのMOSTを含む回路のリーク電流を、MOSTのゲート(G)とソース(S)を逆バイアスする各種の駆動方式によって低減する。低VtのMOSTに各種のG−S逆バイアスを加えることにより、リーク電流の少ない1V以下の高速低電圧CMOS論理回路、あるいはメモリ回路が実現される。

(もっと読む)

31 - 40 / 413

[ Back to top ]