国際特許分類[H03K19/0948]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 論理回路,すなわち,1出力に作用する少なくとも2入力を持つもの;反転回路 (4,821) | 特定の構成要素を用いるもの (1,730) | 半導体装置を用いるもの (1,065) | 電界効果トランジスタを用いるもの (1,019) | MOSFETを用いるもの (616) | CMOSを用いるもの (413)

国際特許分類[H03K19/0948]に分類される特許

81 - 90 / 413

レベルシフト回路

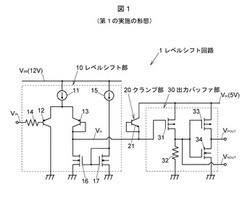

【課題】バッテリの電源投入時等の電源電圧の急激なオーバーシュートに対する耐性を向上させるレベルシフト回路を提供する。

【解決手段】レベルシフト回路1は、バッテリからの高電圧レベルの入力信号VINを入力するレベルシフト部10と、レベルシフト部10の中間信号Vmを一定以下に制限するクランプ部20と、中間信号をより低電圧のCMOSレベルで出力する出力バッファ部30とを備える。出力バッファ部30の初段においてpMOSトランジスタ31の負荷を抵抗32とすることにより、電源電圧のオーバーシュートに対する耐性を向上させる。

(もっと読む)

レベルシフト回路

【課題】レベル変換における動作範囲を広くする。

【解決手段】第1の電位(VDD1)の波高値を有する入力パルス信号(VIN)を入力するCMOSインバータ回路(P1、N1)と、第1の電位よりも高電位となる第2の電位(VDD2)の電源で動作し、一端(ND1)をCMOSインバータ回路の出力端に接続し、他端から第2の電位の波高値を有し入力パルス信号と同相の出力パルス信号(VOUT)を出力するラッチ回路(INV1、P3)と、第1の電位以上かつ第2の電位未満の電源供給をCMOSインバータ回路に対して行う電源供給回路(P2、INV2)と、を備え、電源供給回路は、入力パルス信号が少なくとも接地レベルとなる場合に電源供給を制限するように機能する。

(もっと読む)

PLD回路、集積回路装置及び電子機器

【課題】消費電力を低減できるPLD回路、集積回路装置及び電子機器等を提供すること。

【解決手段】PLD回路は、各トランジスター列が直列接続されたプログラマブルな複数のトランジスターを有する第1〜第m(mは2以上の整数)のトランジスター列TA1〜TAmを含む。第1〜第mのトランジスター列TA1〜TAmの一端に第1の非直流電源VS1が供給される。第1〜第mのトランジスター列TA1〜TAmの各トランジスター列は、複数の入力信号XP(X1P〜XiP)、XN(X1N〜XiN)によってオン・オフされる。第1の非直流電源VS1の電圧により規定される第1のホールド期間に、第1〜第mのトランジスター列TA1〜TAmの他端のノードである第1〜第mのノードNA1〜NAmの電圧レベルを各々出力する。

(もっと読む)

電源変動緩和回路を有する集積回路

【課題】

内部回路の一部の回路が起動または停止したときに内部電源電圧の変動が緩和されるようにした集積回路を提供する。

【解決手段】

電源が供給される集積回路において,電源が供給され内部電源を内部に供給する電源配線と,内部電源を供給される第1及び第2の内部回路と,第2の内部回路を非動作状態から動作状態に制御するイネーブル信号を第2の内部回路に供給するイネーブル信号供給回路とを有し,イネーブル信号供給回路は,イネーブル信号が非動作状態から動作状態に変化したときに動作状態の期間を間欠的に発生する調整イネーブル信号を生成し第2の内部回路に供給する。

(もっと読む)

半導体装置及びこれを備えるデータ処理システム

【課題】スタンバイ時における半導体装置の消費電力を低減する。

【解決手段】スタンバイ時においてハイレベルを出力すべき論理回路については、一対の電源ノードを擬似電源線VDDT1L,VSSTLに接続し、スタンバイ時においてローレベルを出力すべき論理回路については、一対の電源ノードを擬似電源線VDDTL,VSST1Lに接続する。スタンバイ時における擬似電源線VDDTL,VDDT1L,VSSTL,VSST1Lの電位VDDT,VDDT1,VSST,VSST1は、VDDT<VDDT1<VDD、VSST>VSST1>VSSを満たす。これにより、スタンバイ状態においてオンするトランジスタのゲート電極と基板との間を流れるリーク電流や、スタンバイ状態においてオフするトランジスタのドレインと基板との間を流れるリーク電流が低減される。

(もっと読む)

半導体装置

【課題】チップの製造プロセスの微細化にともなって各種リーク電流(サブスレッショルドリーク電流、ゲートトンネルリーク電流、GIDL(Gate-Induced Drain Leakage)電流などの接合リーク電流)が増大している。それらのリーク電流はチップの消費電流を増加する。

【解決手段】第1回路ブロックと、前記第1回路ブロックに接続される第1電源線及び第2電源線と、前記第1電源線と第1電位を供給する第1電位点とを接続するための第1トランジスタと、前記第1トランジスタのゲートに接続される第1駆動回路と、前記第1駆動回路より駆動力の大きい第2駆動回路とを有し、第1の状態から前記第1の状態よりも前記第1電源線と前記第2電源線の間の電位差が大きい第2の状態へ遷移する場合に、第1の期間において前記第1トランジスタを前記第1駆動回路によって駆動し、その後第2の期間において前記第1トランジスタを前記第2駆動回路によって駆動する。

(もっと読む)

駆動回路および表示装置

【課題】出力電圧の立ち上がるタイミングのばらつきを低減することの可能な駆動回路、およびこの駆動回路を備えた表示装置を提供する。

【解決手段】バッファ回路1は、互いに直列に接続されたインバータ回路10およびインバータ回路20を備えている。インバータ回路20は、3つのトランジスタTr21,Tr22,Tr23を有している。そのうちの2つのトランジスタTr21,Tr22は、デュアルゲート型のトランジスタである。これらトランジスタTr21,Tr22のバックゲートの電圧を調整することにより、トランジスタTr21,Tr22の閾値電圧を調整することができる。

(もっと読む)

単相差動変換回路

【課題】

正相出力信号と逆相出力信号とが180°の位相差で位相が一致する単相差動変換回路を提供する。

【解決手段】

単相差動変換回路は,単相入力信号が入力される入力端子と,正相出力信号が出力される正相出力端子と,正相出力信号と差動関係にある逆相出力信号が出力される逆相出力端子と,入力端子と正相出力端子との間に設けられ,直列に接続された第1,第2のインバータを少なくとも含む第1のインバータ列と,入力端子と逆相出力端子との間に設けられ,直列に接続された第3,第4,第5のインバータを少なくとも含み第1のインバータ列よりも段数が1段多い第2のインバータ列とを有し,第1のインバータ列は,さらに,第1のインバータの出力端子にドレインが接続され,導通しない電圧にゲートが接続されたトランジスタを有するダミーインバータを有する。好ましくは,第1,第2,ダミー,第3,第4,第5のインバータのゲート幅の比が,m/2:m2:m/2:1:m:m2であり,前記mはインバータの増倍率である。

(もっと読む)

半導体装置

【課題】終端抵抗のオンオフの切り替え時に外部端子にインピーダンスの急激な変化が生じることを低減する。

【解決手段】外部端子(図2のDQに相当)と、外部端子に接続され、出力信号を外部端子に出力可能とする出力回路(図2の21に相当)と、外部端子に終端抵抗をオンオフ可能に接続する終端回路(図2の22に相当)と、終端抵抗がオフ状態又はオン状態のいずれか一方の状態から他方の状態に変化するまでの時間を、データ出力時に出力信号が一方の論理レベルから他方の論理レベルへ変化するまでの時間以上となるように制御する第1のスルーレート制御回路(図2の23aに相当)と、を備える。

(もっと読む)

半導体装置

【課題】入力信号のHレベルまたはLレベルを正しく検知できる半導体装置を提供する。

【解決手段】半導体装置100は、閾値調整信号に基づいて論理閾値電位を調整可能な入力バッファ(入力CMOS回路11)と、入力バッファの入力と出力とが結線されたレプリカ(レプリカ12)と、予め設定された基準電位(ノードNdHの電位)を発生する基準電位発生回路(基準電位発生回路13)と、レプリカ(レプリカ12)の出力電位(ノードNdRの電位)と基準電位(ノードNdHの電位)とを比較し、閾値調整信号(閾値調整信号CTRL)を入力バッファ(入力CMOS回路11)とレプリカ(レプリカ12)とに出力する比較回路(比較回路14)と、を備える。

(もっと読む)

81 - 90 / 413

[ Back to top ]