国際特許分類[H03L7/099]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073) | 位相ロックループの細部 (2,372) | 主としてループ中の制御発振器に関するもの (282)

国際特許分類[H03L7/099]に分類される特許

1 - 10 / 282

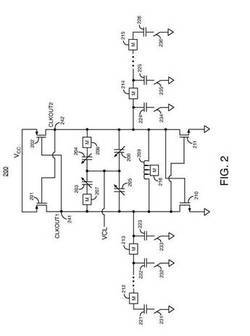

発振回路内で構成要素を接続するオプションコンダクタを提供する技術

【課題】発振回路内で構成要素を接続するオプションコンダクタの使用を可能とする技術の提供。

【解決手段】発振回路200は、第1の伝導層内でルーティングコンダクタを介して相互結合されるトランジスタを含む。発振回路はまた、第2の伝導層内に、バラクタ203〜206、コンデンサ221〜226、及びオプションコンダクタ207、208,212〜216も含む。オプションコンダクタは、トランジスタのうちの1つとコンデンサまたはバラクタとの間の接続の少なくとも一部を形成する。上記発振回路は、第1の伝導層内のルーティングコンダクタを介して前記複数の第1のトランジスタのうちの1つに結合されるインダクタと、該インダクタの第1の部分を形成する、前記第2の伝導層内の第2のオプションコンダクタとをさらに備え得る。

(もっと読む)

PLL回路

【課題】デジタル制御発振器を用いるPLL回路において高速に引き込みを行う。

【解決手段】PLL回路は、当該PLL回路の出力を分周する分周手段(11)と、基準クロック信号と分周手段(11)の出力信号との位相差を検出する位相検出器(12)と、位相検出器の出力信号をフィルタリングして、当該フィルタリング結果をデジタル値として出力するループフィルタ(13)と、デジタル値と固定値とのいずれか1つを選択するセレクタ(15)と、セレクタ(15)で選択された値に応じた周波数で発振するデジタル制御発振器(16)と、スタート信号を受けるまではセレクタ(15)に対して固定値の選択を指示し、スタート信号を受けてから基準クロック信号のエッジタイミングでセレクタ(15)に対してデジタル値の選択を指示するとともに分周手段(11)に対して出力の開始を指示する制御手段(17)とを備えている。

(もっと読む)

ディジタル制御発振装置および高周波信号処理装置

【課題】発振周波数遠方の雑音を低減することが可能なディジタル制御発振装置、ならびに高周波信号処理装置を提供する。

【解決手段】例えば、複数の単位容量ユニットCIU[1]〜CIU[k]を用いて分数容量を実現する。CIU[1]では、容量素子CFXp[1],CFXm[1]の一端がそれぞれ発振出力ノードOscP,OscMに接続される。一方、CIU[2]〜CIU[k]では、容量素子CFXp([2]〜[k]),CFXm([2]〜[k])の一端が固定電圧V6に接続される。CIU[1]〜CIU[k]の一方の容量素子の他端は共通接続され(SWFD)、他方の容量素子の他端も共通接続される(SWFS)。そして、CIU[1]〜CIU[k]内の各スイッチ(SWF1〜SWF3)のオン・オフは共通に制御される。

(もっと読む)

ディジタル制御発振装置および高周波信号処理装置

【課題】DNLの低減を実現可能なディジタル制御発振装置を提供する。

【解決手段】例えば、発振出力ノードOscP,OscM間に並列に結合されるアンプ回路ブロックAMPBK、コイル素子LP,LM、複数の単位容量ユニットCIU等を備え、各CIUは、容量素子CIp,CImと、当該CIp,CImを発振周波数の設定パラメータとして寄与させるか否かを選択するスイッチSWIを備える。ここで、SWIは、デコーダ回路DECからのオン・オフ制御線BIT_CIによって駆動され、当該BIT_CIは、シールド部GSによってOscP,OscMとの間でシールドされる。

(もっと読む)

PLL回路

【課題】PLL回路において、VCOのゲインが低くても、VCOを構成するトランジスタの動作速度に関係なく、ターゲット周波数にロックさせることができ、かつ内蔵ループフィルタのMOS容量の電圧依存性に起因するジッタを抑制できるようにする。

【解決手段】PLL部のチャージポンプ20及びループフィルタ30をスリープ状態にし、校正部60のループフィルタ62の出力電圧V’inと校正用電源66の出力電圧Vdd/2とを電圧比較器63で比較する。比較結果を基に、V’in≒Vdd/2となるように、電流制御装置64によりデジタル制御電圧を生成し、デジタルアナログ変換器65によりアナログ制御電圧V+、V-に変換し、VCO40内の電圧電流変換回路41に供給する。

(もっと読む)

PLL回路およびそのキャリブレーション方法

【課題】1回のキャリブレーションによって電圧制御発振器のフリーラン発振周波数がPLLロックレンジ内に入るようにして、キャリブレーション時間の大幅な時間短縮が可能となり、低消費電流化に貢献できるようにする。

【解決手段】PLLループをオープンにし、電圧制御発振器1に制御電圧Vcとして基準電圧Vaを入力したとき、基準信号f3のパルスによって帰還信号f2のパルス幅をカウントし、得られたカウント値に基づき、電圧制御発振器1の発振周波数f1を調整するキャリブレーションを実行するキャリブレーション回路10を設ける。

(もっと読む)

位相ロック・ループにおけるVCOの動的バイアス印加

【課題】無線通信機器における局部発振器を提供する。

【解決手段】局部発振器が位相ロック・ループを含む。位相ロック・ループは電圧制御発振器23と新規のVCO制御回路27を含む。VCO制御回路はプログラム可能で設定可能であることが出来る。1つの例では、前記VCOの電力状態を変更するために、命令が前記VCO制御回路に受信される。命令は、セルラー電話における無線チャネル状態の検出された変化(例えば、信号対雑音判定の変化)に応答して、他の回路によって発せられる。応答して、VCO制御回路は、PLLのループ帯域幅を徐々に拡大し、次に該VCOバイアス電流を徐々に変更して該VCO電力状態を変更し、そして次にPLLのループ帯域幅を縮小して元の帯域幅に戻す、制御信号を出力する。PLL帯域幅を拡大すること、VCO電力状態を変更すること、及びPLL帯域幅を縮小すること、の全過程はPLLがロックされたままで行われる。

(もっと読む)

信号生成装置及び信号生成方法

【課題】任意のジッタが付加された良好な信号波形を有する信号を容易に生成することができる信号生成装置を提供する。

【解決手段】基準クロックを基に制御データに応じた周波数の出力クロックを生成し出力するダイレクトデジタルシンセサイザ(DDS)と、ジッタ設定に応じてDDSの出力周波数を制御するための一連の設定データが格納されたジッタ制御テーブルを有し、基準クロックに同期させてDDSに制御データを供給する制御部とを備え、基準クロックに同期したタイミングで制御データをジッタ制御テーブルに格納されている設定データで順次書き替えることで、短時間かつ一定の時間間隔で制御データの切り替えを行い、周期的に周波数が変化する、すなわちジッタが付加された出力クロックをDDSにより生成できるようにする。

(もっと読む)

PLL回路及びその制御方法

【課題】回路規模の増大を抑制しつつ、VCOの発振周波数を広い範囲で変化させることができるPLL回路及びその制御方法を提供すること。

【解決手段】本発明にかかるPLL回路1は、VCO11と、制御ロジック14と、位相比較器13と、を備える。VCO11は、両端の電位差に応じて容量値が変化する可変容量素子を有し、電位差に応じた発振周波数の出力信号を出力する。制御ロジック14は、可変容量素子の一端に所定の電圧を印加した状態で、基準信号と出力信号との周波数差に基づいて、当該可変容量素子の他端に印加する制御電圧Vtcを決定する。位相比較器13は、可変容量素子の他端の電圧を制御ロジック14により決定された制御電圧Vtcに固定した状態で、基準信号と出力信号との位相差に基づいて、可変容量素子の一端に印加する制御電圧Vtaを決定する。

(もっと読む)

高周波発振源

【課題】位相雑音の劣化を抑制することができる高周波発振源を得ることを目的とする。

【解決手段】所定の周波数で発振する基準発振器1と、その基準発振器の出力波が注入されていない場合の発振周波数が、その基準発振器の出力波の周波数の整数倍に設定されている(または設定される)注入同期発振器とを備え、その基準発振器から注入同期発振器に注入される電力を、注入同期発振器の低離調周波数の位相雑音が基準発振器の位相雑音と(同じ周波数で比較した場合に)等しくなるように、かつ高離調周波数の位相雑音が注入電力がない時の注入同期発振器の位相雑音と(同じ周波数で比較した場合に)等しくなるように適切な注入電力とする電力調整手段を設ける。

(もっと読む)

1 - 10 / 282

[ Back to top ]