国際特許分類[H03M1/12]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 符号化,復号化または符号変換一般 (10,763) | アナログ/デジタル変換;デジタル/アナログ変換 (2,647) | アナログ/デジタル変換器 (1,364)

国際特許分類[H03M1/12]の下位に属する分類

各ステップが同じかまたは異なる変換手段を持ち,1ビットより多く出力するステップごとの変換 (169)

変換器が処理できる信号の範囲を修正するための自動制御,例.利得を変動するもの (82)

n+mビットを得るためにnビット方式を用いる分解能の増大,例.ディザリングによるもの (12)

パターン読出し形 (7)

アナログ値が基準値と比較されるもの (381)

追従比較形変換器 (7)

時間間隔への中間変換を行うもの (240)

パルス周波数への中間変換を行うもの (12)

正弦波信号の位相への中間変換を行うもの (4)

国際特許分類[H03M1/12]に分類される特許

1 - 10 / 450

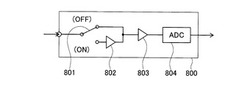

信号切替回路およびA/D変換装置

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

レベル調整装置、およびレベル調整のためのプログラム

【課題】ユーザに負担をかけることなく、容易にアナログ音響信号の音質劣化を抑制することが可能なレベル調整装置を提供すること。

【解決手段】入力ポートはアナログ入力ブロック800を有し、アナログ入力ブロック800は、迂回スイッチ801、固定ゲインにて信号レベルの減衰を行うパッド802、可変ゲインにて信号レベルを増幅又は減衰して調整するアンプ803を備える。迂回スイッチ801はパッド802とアンプ803により信号レベルが調整されるパッドオン状態とアンプ803のみで信号レベルが調整されるパッドオフ状態を切り替えられる。信号レベルの調整の後に、パッドオン状態で、かつパッドのオン・オフの何れの状態でもゲインの調整が可能な重複範囲ROVの範囲内である入力ポートを抽出し、該当する入力ポートのアナログ入力ブロック800に対して、パッドオフ状態への切り替え調整処理を行う。

(もっと読む)

広帯域AD変換装置

【課題】 高周波信号を帯域分割して複数のAD変換素子によって分担してカバーするダイレクトコンバージョン方式の方式の受信装置を実現する場合において、AD変換素子のナイキスト周波数の境界にかかわらず任意の周波数の帯域を観測帯域として選択でき、選択された1個の観測帯域を1個のAD変換素子でサンプリングできるような手段を提供する

【解決手段】 複数のAD変換素子によって帯域を分割してサンプリングする場合に生じるナイキスト周波数の境界を、別なサンプリング周波数で動作する補助的なAD変換素子を組み合わせて使用することによって回避し、1個の任意の観測帯域を1個のAD変換素子でサンプリングする。

(もっと読む)

タイムインタリーブ型サンプラのアレイを有する無線周波数(RF)サンプリング装置およびシナリオベースの動的資源割り当てのための方法

【課題】RFサンプリングシステムの動的資源割り当てのための方法および装置を提供すること。

【解決手段】

受信した無線周波数(RF)信号から、タイムインタリーブされた複数のサンプルを生成し、そのタイムインタリーブされた複数のサンプルを組み合わせて信号品質を生成することにより決定された信号品質測定値に基づいた、RFサンプリングシステムの動的資源割り当てのための方法および装置。

(もっと読む)

増幅回路およびA/D変換器

【課題】最小限の構成を用いて、演算増幅器の入出力端子間の寄生容量に起因する増幅回路の演算誤差を補償し、高精度の増幅率を得る。

【解決手段】増幅回路10は、一方の端子が演算増幅器A1の反転入力端子に、他方の端子が演算増幅器A1の反転出力端子に接続された容量CP5と、一方の端子が演算増幅器A1の非反転入力端子に、他方の端子が演算増幅器A1の非反転出力端子に接続された容量CN5とを備えている。

(もっと読む)

アナログ入力回路またはアナログ/ディジタル変換装置

【課題】制御電源のON、OFFの状態に関係なく、また外部に放電用機材が無くてもフィルタ回路、フライングキャパシタ回路内コンデンサの放電を短時間で可能にするためのアナログ入力回路またはアナログ/ディジタル変換装置を提供する。

【解決手段】縦列接続されたフィルタ回路とフライングキャパシタ回路を複数組備え、複数組のフライングキャパシタ回路の後段を増幅器の入力端子に共通に接続し、増幅器の後段にアナログ/ディジタル変換器を備えるとともに、外部制御電源に接続された基板上に構成されたアナログ/ディジタル変換装置において、フィルタ回路とフライングキャパシタ回路は、並列コンデンサとこれに並列に接続された抵抗と常閉接点の直列回路とを備えており、常閉接点は、制御電源の端子間に接続され、制御用接点を介して励磁される補助リレーにより駆動されているアナログ/ディジタル変換装置。

(もっと読む)

A/D変換器

【課題】 差動信号のA/D変換を行うA/D変換器においてチャージインジェクションやクロックフィードスルーに起因したA/D変換の誤差を少なくする。

【解決手段】 各A/D変換サイクルにおいて、正相アナログ入力部50Pおよび逆相アナログ入力部50Nは、正相アナログ入力信号INPおよび逆相アナログ入力信号INNをサンプリングし、正相アナログ入力信号INPを正相入力ノードC1PBまたは逆相入力ノードC1NBに、逆相アナログ入力信号INNを逆相入力ノードC1NBまたは正相入力ノードC1PBに供給する。制御部400は、このサンプリングした各信号の供給先をA/D変換サイクル単位で切り換える。A/D変換器では、正相入力ノードC1PBおよび逆相入力ノードC1NB間の電圧のA/D変換が行われる。平均化部502は、所定回数に亙るA/D変換結果が得られる毎に、A/D変換結果を平均化して出力する。

(もっと読む)

アナログデジタル変換装置及び信号処理システム

【課題】アナログデジタル変換装置のサイズを縮小し、且つ、インタリーブ間のミスマッチに起因する誤差の補正に必要な処理量を低減する。

【解決手段】本発明の実施形態のアナログデジタル変換装置は、アナログ入力信号をデジタル出力信号に変換する。アナログデジタル変換装置は、アナログデジタル変換ユニット12と、疑似エイリアス信号生成部114と、利得制御部116と、エイリアス信号補正部118と、を備える。アナログデジタル変換ユニット12は、アナログ入力信号を、複数のデジタル信号に変換する。疑似エイリアス信号生成部114は、複数のデジタル信号を合成した合成信号に含まれるエイリアス信号成分を模擬する疑似エイリアス信号を生成する。利得制御部116は、疑似エイリアス信号を用いて、デジタル出力信号の利得を制御する利得制御信号を生成する。エイリアス信号補正部118は、利得制御信号を用いて、エイリアス信号成分を補正する。

(もっと読む)

アナログデジタル変換装置及びアナログデジタル変換方法

【課題】変換対象であるアナログ信号の信号特性に応じた分解能でデジタル信号に変換でき、かつ、その際の消費電力が削減できるようにする。

【解決手段】入力信号G1の所定の特性を検出する信号特性検出部6と、信号特性検出部により検出された信号特性に基づき分解能を設定し、該分解能のアナログデジタル変換に必要な動作のみを指示する制御信号G10を生成し、出力する制御信号生成部7と、複数のレジスタ値が格納されて、レジスタ値に対応したレジスタ信号を出力する逐次比較レジスタと、レジスタ信号をアナログ信号に変換して、基準電圧信号として出力するデジタルアナログ変換器と、入力信号と基準電圧信号とを比較して比較結果信号を出力するコンパレータと、を備える。

(もっと読む)

コンパレータシステム、アナログデジタルコンバータおよびコンパレータの閾値補正方法。

【課題】 閾値のずれを補正できるコンパレータシステムを提供する

【解決手段】 コンパレータは、一対のキャパシタを介して入力端子から入力信号を受ける一対の入力ノードと、入力信号の電圧差を示す出力信号を出力する出力ノードとを有する。第1制御回路は、コンパレータの閾値を補正する補正期間に、所定量の負荷が出力ノードに接続された状態で、出力信号の論理が反転するまで一対の入力ノードに設定するコモン電圧を変更し、出力信号の論理が反転するときのコモン電圧の値を求め、求めたコモン電圧を補正期間後の通常動作期間に使用する。第2制御回路は、出力ノードに接続される負荷の量を設定する。第3制御回路は、補正期間に、所定量の負荷が出力ノードに接続されているときのコンパレータの標準の閾値の変動量に対応する電圧差を有する第1電圧および第2電圧を入力端子にそれぞれ供給する。

(もっと読む)

1 - 10 / 450

[ Back to top ]