国際特許分類[H05K1/16]の内容

電気 (1,674,590) | 他に分類されない電気技術 (122,472) | 印刷回路;電気装置の箱体または構造的細部,電気部品の組立体の製造 (64,965) | 印刷回路 (15,851) | 印刷電気部品,例.印刷抵抗器,印刷コンデンサまたは印刷インダクタンス,を備えるもの (587)

国際特許分類[H05K1/16]に分類される特許

181 - 190 / 587

多層配線板内蔵用キャパシタ形成材、多層配線板内蔵用キャパシタの製造方法、およびキャパシタ内蔵多層配線板

【課題】大きな静電容量を有し、かつ長期信頼性の高い多層配線板内蔵用キャパシタを歩留まり良く、効率的に提供することが可能な多層配線板内蔵用キャパシタ形成材、当該キャパシタ形成材を用いてなる高信頼性かつ小型の多層配線板内蔵用キャパシタの製造方法、および当該キャパシタを備えるキャパシタ内蔵多層配線板を提供すること。

【解決手段】第1の導電層108と、第2の導電層109と、前記第1の導電層108および前記第2の導電層109の間に形成された金属酸化物層105と、を備え、前記第1の導電層108および前記第2の導電層109の双方またはいずれか一方の導電層が銅以外の金属層103および該金属層103上に形成された銅パターン102からなり、隣接する前記銅パターン102およびこれら銅パターン間下部に位置する前記金属層103により過電流遮断素子を構成していることを特徴とする、多層配線板内蔵用キャパシタ形成材。

(もっと読む)

部品内蔵実装基板

【課題】高速・高密度電子機器で特に信号品質の確保が必要なCPU−メモリ間のアドレス線において、小型化と高周波特性確保の両立が実現できる部品内蔵実装基板を提供する。

【解決手段】絶縁基板100の表面上に、CPU101と、チップ部品としての並列終端抵抗105と、メモリ102とが搭載されている。絶縁基板100の内部には、CPU101の直下に第1のデカップリングキャパシタ106aが内蔵され、メモリ102の直下に第2のデカップリングキャパシタ106bが内蔵されている。並列終端抵抗105の直下には、膜部品としての直列終端抵抗103b及び信号品質補償用キャパシタ104bがその面を絶縁基板100の表面に平行にして内蔵されており、両者間に第3のデカップリングキャパシタ106cが内蔵されている。

(もっと読む)

セラミック基板の製造方法、セラミック基板、および電子装置

【課題】抵抗を覆うオーバーコートガラスのめっき耐性の高いセラミック基板を確実に製造することが可能なセラミック基板の製造方法、および信頼性の高いセラミック基板、および該セラミック基板を用いた電子装置を提供する。

【解決手段】一方主面1aに抵抗15となる抵抗膜115が形成され、抵抗膜を覆うように、収縮開始温度が、抵抗膜のそれより高い第1のガラス膜111を形成し、形成された第1のガラス膜111を覆うように、第1のガラス膜を構成するガラス材料よりめっき耐性が大きいガラス材料を含む第2のガラス膜112を形成し、かつ、少なくとも一方主面1aに、焼成工程で焼結しないセラミック材料からなる収縮抑制用グリーンシート102が配置された積層体を形成し、この積層体を、セラミックグリーンシートが焼結し、収縮抑制用グリーンシートが実質的に焼結しない温度で焼成する。

(もっと読む)

インダクタ内蔵基板及びその製造方法

【課題】容易に厚膜化できて抵抗の低いインダクタが内蔵されたインダクタ内蔵基板を提供する。

【解決手段】基板30と、基板30の上に接着されたインダクタ12と、インダクタ12の一端側の第1接続部Aと他端側の第2接続部Bとにそれぞれ電気的に接続された配線層40〜44とを含み、インダクタ12の厚みは配線層40〜44の厚みより厚く設定されている。インダクタ12は、金属板10がプレス加工されて得られるインダクタ部材12aが基板30に接着層14によって接着されて形成される。

(もっと読む)

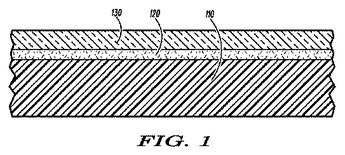

印刷電子素子及び当該素子の電気的特性値を導出する方法

印刷電子素子、及び当該素子の電気的特性値を導出する方法では、誘電体材料130を基板110にプリセット力を使用してコンタクト印刷する。基板110は、コンタクト印刷によって加わる力の大きさに直接比例して光応答する圧力検出材料120を有する。コンタクト印刷の力によって、圧力検出材料は、力の大きさを定量化することができるパターンを形成するようになる。次に、当該パターンを光学的に検査し、そして複数セットの標準と比較して、印刷に使用された力の大きさを定量化する。次に、印刷誘電体材料の厚さが、定量化された力に基づいて、当該力を別のセットの標準と比較することにより計算される。  (もっと読む)

(もっと読む)

共用型基板とそれを用いる半導体装置

【課題】基板配線の再設計と製作とに要る時間を大幅に縮短可能な共用型基板を提供する。

【解決手段】複数の内接パッド311、312、313と複数の外接パッド321、322、323とを有する。全ての内接パッド311、312、313を外接パッド321、322、323群に電気接続し、且つ随意にヒューズを焼切るため、基板の一表面には複数の分岐配線330とそれらの分岐配線330に直列連結される複数のヒューズF1、F2、F3、F4、F5、F6、F7、F8、F9、F10、F11、F12を形成している。

(もっと読む)

低温焼成セラミック回路基板及びその製造方法

【課題】拘束焼成法で低温焼成セラミック回路基板を製造する場合に、ワイヤボンディング性等の電気的特性を損なわずに、生産性を向上させる。

【解決手段】最外層に導体ペーストで印刷されたワイヤボンディングパッド用の導体15、16を有する焼成前の低温焼成セラミック基板11を、導体15、16と同時焼成し、焼成後、拘束焼成用グリーンシート18の残存物を取り除くことによって荒れたワイヤボンディングパッド用の導体15、16の表面にめっき被膜20、21を形成してワイヤボンディングパッド24,25を形成する。

(もっと読む)

電解コンデンサシート及び配線基板、並びに、それらの製造方法

【課題】基板を厚くすることなく、且つ小さな占有面積でより大きな容量が得られる電解コンデンサシートを提供する。

【解決手段】電解コンデンサシートは、側面を除き表面が粗化された弁金属シート体11と、弁金属シート体11の表面に形成された金属酸化膜12と、弁金属シート体11の上面側に形成された金属酸化膜12の開口内で、弁金属シート体11の表面に導通する陽極引き出し電極15と、弁金属シート体11の上面側の金属酸化膜12の表面に形成された固体電解質層13と、固体電解質層13の表面に形成された陰極引き出し電極16とを有する。

(もっと読む)

キャパシタ内蔵型印刷回路基板

【課題】低いインダクタンスと高いキャパシタンスを有するキャパシタ内蔵印刷回路基板。

【解決手段】積層ポリマーキャパシタ層21と、複数のポリマーシートのうち少なくとも一つのシートにより分離され、相互交代に配置されてペアを成す少なくとも一つの第1内部電極24及び第2内部電極27と、それらに連結される複数個の第1引出電極25a及び第2引出電極28aと、積層ポリマーキャパシタ層の一面または両面に積層され、層間回路を構成する複数の導電パターン及び導電性ビアが形成された少なくとも一つの絶縁層と、第1引出電極に連結されるよう積層ポリマーキャパシタ層を貫通して形成された複数の第1キャパシタ用ビア26と、第2引出電極に連結されるよう積層ポリマーキャパシタ層を貫通して形成された複数の第2キャパシタ用ビア29とを含み、複数個の第1及び第2引出電極は相互交代に配置され相互向い合うよう配置。

(もっと読む)

キャパシタ内蔵多層プリント配線板用誘電体材料,キャパシタ部材とキャパシタ内蔵多層プリント配線板およびキャパシタ内蔵多層プリント配線板の製造方法

【課題】基板内に1桁以上の容量密度に違いのある基板内蔵キャパシタを効率的に作製するキャパシタ内蔵多層プリント配線板用誘電体材料,キャパシタ部材とキャパシタ内蔵多層プリント配線板およびキャパシタ内蔵多層プリント配線板の製造方法を提供する。

【解決手段】厚さ5〜15μmの第1の金属層と、厚さ0.1〜1μmの第1の絶縁層と、厚さ10〜35μmの第2の金属層と、厚さ5〜50μmの第2の絶縁層からなるキャパシタ内蔵多層プリント配線板用誘電体材料であって、第1の絶縁層の比誘電率が10〜2000であり、第2の絶縁層が半硬化の樹脂材料でその硬化後の比誘電率が20〜100である、キャパシタ内蔵多層プリント配線板用誘電体材料。

(もっと読む)

181 - 190 / 587

[ Back to top ]