半導体装置

【課題】バンプを有する半導体装置において、半導体素子の電源供給系の電気抵抗に起因する電圧降下を低く抑える。

【解決手段】本発明の半導体装置は、複数の電極パッドを有する配線基板2とその上にバンプ形成面を下向きにして搭載された半導体チップ3とを備えている。半導体チップ3の表面の周辺部には、円形状の複数の信号バンプ4が配設され、中央部にはいずれも長尺形状を有する複数の電源バンプ5とグランドバンプ6が配設されている。配線基板2の半導体チップ搭載面には、周辺部に信号バンプ接続用の円形状の電極パッド7が形成され、中央部にはいずれも長尺形状を有する電源バンプ接続用の電極パッド8およびグランドバンプ接続用の電極パッド9が形成されている。そして、半導体チップ3の各バンプが配線基板2の対応する電極パッドに接合されている。

【解決手段】本発明の半導体装置は、複数の電極パッドを有する配線基板2とその上にバンプ形成面を下向きにして搭載された半導体チップ3とを備えている。半導体チップ3の表面の周辺部には、円形状の複数の信号バンプ4が配設され、中央部にはいずれも長尺形状を有する複数の電源バンプ5とグランドバンプ6が配設されている。配線基板2の半導体チップ搭載面には、周辺部に信号バンプ接続用の円形状の電極パッド7が形成され、中央部にはいずれも長尺形状を有する電源バンプ接続用の電極パッド8およびグランドバンプ接続用の電極パッド9が形成されている。そして、半導体チップ3の各バンプが配線基板2の対応する電極パッドに接合されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置に係り、特に、消費電力が高い高性能デバイスに対して有用な突起状電極を有する半導体装置に関する。

【背景技術】

【0002】

従来から、半導体チップを配線基板に搭載し接続する実装技術の一つとして、フリップチップ接続がある。フリップチップ接続は、半導体チップの主面に多数の電極をマトリックス状に配置し、この電極を介して外部との信号の送受信や電源の供給を行う接続技術であり、マイクロプロセッサ等の高性能デバイスや、多くの信号ピンを必要とするシステムLSIに用いられている。

【0003】

フリップチップ接続により実装される半導体チップの主面(表面)の主面には、バンプと呼ばれる突起状電極が多数配置されている。通常、主面の周辺部には、信号用のバンプ(信号バンプ)が狭い間隔(ピッチ)pで配設されており、中央部には、電源供給用の電源バンプと接地用のグランドバンプが、それぞれ信号バンプの配設ピッチpよりも広いピッチで配設されている。

【0004】

従来から、マイクロプロセッサ等の高性能デバイスにおいては、半導体チップ内の電源供給系の電気抵抗に起因する電圧降下(=抵抗×電流)が問題になっている。そして、半導体チップの機能素子Aと電源バンプおよびグランドバンプとの距離を短縮し、前記した電気抵抗に起因する電圧降下をさらに小さくすることが求められている。

【0005】

このような要求に合わせて、半導体チップ主面の電源供給領域および/または接地領域でも、信号バンプと同じ狭い配設ピッチpで電源バンプおよびグランドバンプを配置することが考えられている。

【0006】

しかしながら、このようなバンプ配置を有する半導体チップを搭載した半導体装置においては、以下に示す問題があった。すなわち、電源供給領域および/または接地領域においてバンプ間の間隔が狭くなるため、電源バンプ等の間の短絡が生じやすくなり、それに起因する不良が増大するおそれがあった。また、これらのバンプの狭ピッチ化に対応し、配線基板側の電極パッドおよび配線の設計が複雑化するため、製造歩留りの低下が生じやすかった。さらに、配線基板と半導体チップとの間に絶縁性樹脂の封止層を形成する工程で、絶縁性樹脂の注入および充填作業が難しくなるため、充填不良が発生しやすいか、あるいはスループットが低下するという問題があった。

【0007】

なお、この種の関連技術として、半導体装置の一例が開示されている(例えば、特許文献1参照。)。

【特許文献1】特開2001−284402号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

本発明はこれらの問題を解決するためになされたもので、突起状電極(バンプ)を有する半導体装置において、半導体素子の電源供給系の電気抵抗に起因する電圧降下を低く抑えることを目的としている。

【課題を解決するための手段】

【0009】

本発明の一態様に係る半導体装置は、一方の主面に複数の電極パッドを有する配線基板と、一方の主面に複数の突起状電極を有し、この突起状電極形成面を下向きにして前記配線基板の前記電極パッド形成面上に搭載された半導体素子を備え、前記半導体素子の前記突起状電極と前記配線基板の対応する電極パッドとを接合して成る半導体装置であり、前記半導体素子の電源供給領域および/または接地領域に形成された前記突起状電極は長尺形状を有し、かつこれら長尺形状の突起状電極はそれぞれの長辺方向を平行に揃えて配列されていることを特徴とする。

【発明の効果】

【0010】

本発明の一態様に係る半導体装置によれば、電源供給系の電気抵抗に起因する電圧降下を低く抑えることができる。

【発明を実施するための最良の形態】

【0011】

以下、本発明を実施するための形態について説明する。なお、以下の記載では実施形態を図面に基づいて説明するが、それらの図面は図解のために提供されるものであり、本発明はそれらの図面に限定されるものではない。

【0012】

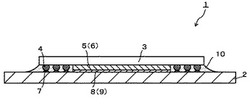

図1は、本発明の第1の実施形態に係る半導体装置の構成を示す断面図であり、図2は、第1の実施形態における半導体チップのバンプ(突起状電極)の配置を示す平面図である。また、図3は、図2の破線で囲まれた部分を拡大して示す図である。

【0013】

図1に示す第1の実施形態の半導体装置1は、一方の主面に複数の電極パッドを有するパッケージ用の配線基板2と、半導体チップ3を備えている。半導体チップ3は一方の主面である表面(素子形成面)に複数のバンプ(突起状電極)を有し、このバンプ形成面を下向きにして(フェースダウンで)配線基板2の電極パッド形成面上に搭載されている。

【0014】

図2に示すように、半導体チップ3の表面の周辺部には、円形状の複数の信号バンプ4が、所定の間隔(配設ピッチp)で配設されている。そして、このような信号バンプ4に取り囲まれた半導体チップ4の中央部には、複数の電源バンプ5とそれと同数のグランドバンプ6が、交互に並べて配設されている。電源バンプ5とグランドバンプ6は、いずれも長尺形状を有し、それぞれの長辺が半導体チップ3の少なくとも一辺に平行になるように配列されている。長尺形状の電源バンプ5とグランドバンプ6の配置間隔(配設ピッチ)は、信号バンプ4の配設ピッチpと等しくすることが好ましい。また、電源バンプ5とグランドバンプ6、および信号バンプ4の構成材料としては、スズ(Sn)をベースにした半田材料(Sn−Pb合金、Sn−Ag合金、Sn−Cu合金等)や、金(Au)、銅(Cu)等の単体金属を用いることができる。

【0015】

電源バンプ5およびグランドバンプ6の平面形状は、辺あるいは径がそれに直交する方向の辺あるいは径に比べて長尺に構成された形状(長尺形状)であればよい。長方形、平行四辺形、長楕円形等とすることができる。

【0016】

長尺形状の電源バンプ5およびグランドバンプ6の長辺あるいは長径の長さは、半導体チップ3の電源供給領域および/または接地領域の対応する長さ全体の1/3以上であれば、電源供給系の電気抵抗に起因する電圧降下抑制の効果を上げることができる。形成の容易さ等の点からは、電源供給領域および/または接地領域の長さと等しくすることが好ましい。

【0017】

配線基板2の半導体チップ搭載面においては、周辺部に信号バンプ接続用の円形状の電極パッド7が形成されている。また、中央部には、いずれも長尺形状を有する電源バンプ接続用の電極パッド8およびグランドバンプ接続用の電極パッド9が、交互に並べて配置されている。電源バンプ接続用の電極パッド8およびグランドバンプ接続用の電極パッド9の平面形状は、長尺形状であれば特に限定されず、長方形、平行四辺形、長楕円形などとすることができる。これらの電極パッド8,9は、対応する電源バンプ5およびグランドバンプ6と同一の形状および長さとし、かつこれらのバンプに対応する位置に配置することが好ましい。

【0018】

そして、半導体チップ3の各バンプが配線基板2の対応する電極パッドに接合されている。すなわち、半導体チップ3の円形状の信号バンプ4が配線基板2の信号バンプ接続用の電極パッド7に接合されており、半導体チップ3のいずれも長尺形状の電源バンプ5とグランドバンプ6が、配線基板2のいずれも長尺形状の電源バンプ接続用電極パッド8とグランドバンプ接続用電極パッド9にそれぞれ接合されている。

【0019】

また、配線基板2と半導体チップ3との間には、絶縁性樹脂が注入・充填され、絶縁性樹脂から成る封止層10が形成されている。さらに、配線基板2の半導体チップ搭載面と反対側の下面には、はんだボールのような外部接続用の電極(図示を省略する。)が配設されている。

【0020】

このように構成される第1の実施形態の半導体装置においては、図3に拡大して示すように、半導体チップ3の機能素子Aと長尺形状の電源バンプ5およびグランドバンプ6との距離の最大値がp/2となり、従来のバンプ配置に比べて大幅に短縮することができる。また、狭ピッチのバンプ配置に比べても、機能素子Aと電源供給用のバンプとの距離を短縮することができる。

【0021】

ここで、従来の半導体装置におけるバンプ配置を図4に示し、狭ピッチのバンプ配置を図5および図6に示す。図4に示すバンプ配置においては、電源バンプ52およびグランドバンプ53の配設ピッチは信号バンプ54の配設ピッチpの2倍になっており、半導体チップ51内の機能素子Aと電源バンプ52およびグランドバンプ53との距離の最大値はpとなっている。また、図5および図6に示す狭ピッチのバンプ配置では、半導体チップ51内の機能素子Aと電源バンプ52およびグランドバンプ53との距離の最大値は、√2p/2(<p)となる。

【0022】

第1の実施形態の半導体装置においては、このような従来のバンプ配置に比べて、機能素子Aと電源供給用のバンプとの距離を短縮することができるので、電源系の電圧降下を低減し、電気的特性に優れた半導体装置を得ることができる。

【0023】

また、第1の実施形態の半導体装置においては、電源バンプ5およびグランドバンプ6間の短絡が発生しにくく、製造歩留りが向上する。さらに、半導体チップ3の電源バンプ5とグランドバンプ6がそれぞれ長尺形状を有しており、これらのバンプと半導体基板2側の電極パッド8,9との接合面積が従来に比べて増大しているため、半導体チップ3から発生する熱を、これらの長尺形状のバンプ(電源バンプ5とグランドバンプ6)および半導体基板2側の長尺形状の電極パッド8,9を介して効率的に放散させることができる。こうして、熱膨張により発生する熱応力を効果的に分散することができるので、温度サイクルに対する寿命も向上する。またさらに、絶縁性樹脂の注入および充填作業が容易であり、充填不良が発生しにくいという利点がある。

【0024】

次に、本発明の別の実施形態について説明する。図7は、本発明の第2の実施形態に係る半導体装置の構成を示す断面図である。

【0025】

第2の実施形態において、半導体チップ3の素子形成面には、円形状の複数の信号バンプ4と、いずれも長尺形状の複数の電源バンプ5およびグランドバンプ6が、それぞれ第1の実施形態と同様に配設されている。

【0026】

配線基板2の半導体チップ搭載面において、周辺部には信号バンプ接続用の円形状の複数の電極パッド7が形成されている。また中央部にも、円形状の複数の電源バンプ接続用の電極パッド8とグランドバンプ接続用の電極パッド9がそれぞれ形成されている。これら電源バンプ接続用の電極パッド8およびグランドバンプ接続用の電極パッド9は、それぞれが列をなすように形成され、かつ電源バンプ接続用電極パッド8の列とグランドバンプ接続用電極パッド9の列が、半導体チップ3側の長尺形状の電源バンプ5およびグランドバンプ6に対応するように交互に配列されている。

【0027】

そして、半導体チップ3の円形状の信号バンプ4が、配線基板2の信号バンプ接続用の円形状の電極パッド7に接合されている。また、半導体チップ3の長尺形状の電源バンプ5が、配線基板2の対応する位置に形成された電源バンプ接続用の電極パッド8の列に接合され、半導体チップ3の長尺形状のグランドバンプ6が、配線基板2の対応する位置に形成されたグランドバンプ接続用の電極パッド9の列に接合されている。

【0028】

また、配線基板2と半導体チップ3との間には、絶縁性樹脂から成る封止層10が形成されている。さらに、配線基板2の半導体チップ搭載面と反対側の下面には、はんだボールのような外部接続用の電極(図示を省略する。)が配設されている。

【0029】

このように構成される第2の実施形態の半導体装置においては、第1の実施形態の半導体装置と同様に、半導体チップ3の機能素子Aと長尺形状の電源バンプ5およびグランドバンプ6との距離の最大値がp/2となり、従来からのバンプ配置に比べて、機能素子Aと電源供給用のバンプとの距離を短縮することができる。したがって、高性能デバイスにおける電源系の電圧降下を低減し、電気的特性に優れた半導体装置を得ることができる。

【0030】

また、配線基板2側の電源バンプ接続用の電極パッド8およびグランドバンプ接続用の電極パッド9の一部が欠損したとしても、同じ列に属する他の電極パッド8,9がそれを補って接続点となるため、半導体チップ3のバンプとの間に十分な電気接続が得られる。さらに、第1の実施形態に比べて、配線基板2の電極パッド8,9間の配線形成が可能であり、配線の自由度が大きいという利点がある。

【0031】

以上の実施形態で説明された構成、形状、大きさおよび配置関係については、概略的に示したものにすぎず、また各構成の組成(材質)等については例示にすぎない。したがって、本発明は以上の実施形態に限定されるものではなく、特許請求の範囲に示される技術的思想の範囲を逸脱しない限り、さまざまな形態に変更することができる。

【図面の簡単な説明】

【0032】

【図1】本発明の第1の実施形態に係る半導体装置の構成を示す断面図である。

【図2】第1の実施形態における半導体チップのバンプの配置を示す平面図である。

【図3】図2の破線で囲まれた部分を拡大して示す図である。

【図4】従来からの半導体装置における半導体チップのバンプ配置の一例を示す平面図である。

【図5】狭ピッチのバンプ配置を示す平面図である。

【図6】図5の破線で囲まれた部分を拡大して示す図である。

【図7】本発明の第2の実施形態に係る半導体装置の構成を示す断面図である。

【符号の説明】

【0033】

1…半導体装置、2…配線基板、3…半導体チップ、4…信号バンプ、5…電源バンプ、6…グランドバンプ、7…信号バンプ接続用の電極パッド、8…電源バンプ接続用の電極パッド、9…グランドバンプ接続用の電極パッド、10…絶縁性樹脂から成る封止層。

【技術分野】

【0001】

本発明は、半導体装置に係り、特に、消費電力が高い高性能デバイスに対して有用な突起状電極を有する半導体装置に関する。

【背景技術】

【0002】

従来から、半導体チップを配線基板に搭載し接続する実装技術の一つとして、フリップチップ接続がある。フリップチップ接続は、半導体チップの主面に多数の電極をマトリックス状に配置し、この電極を介して外部との信号の送受信や電源の供給を行う接続技術であり、マイクロプロセッサ等の高性能デバイスや、多くの信号ピンを必要とするシステムLSIに用いられている。

【0003】

フリップチップ接続により実装される半導体チップの主面(表面)の主面には、バンプと呼ばれる突起状電極が多数配置されている。通常、主面の周辺部には、信号用のバンプ(信号バンプ)が狭い間隔(ピッチ)pで配設されており、中央部には、電源供給用の電源バンプと接地用のグランドバンプが、それぞれ信号バンプの配設ピッチpよりも広いピッチで配設されている。

【0004】

従来から、マイクロプロセッサ等の高性能デバイスにおいては、半導体チップ内の電源供給系の電気抵抗に起因する電圧降下(=抵抗×電流)が問題になっている。そして、半導体チップの機能素子Aと電源バンプおよびグランドバンプとの距離を短縮し、前記した電気抵抗に起因する電圧降下をさらに小さくすることが求められている。

【0005】

このような要求に合わせて、半導体チップ主面の電源供給領域および/または接地領域でも、信号バンプと同じ狭い配設ピッチpで電源バンプおよびグランドバンプを配置することが考えられている。

【0006】

しかしながら、このようなバンプ配置を有する半導体チップを搭載した半導体装置においては、以下に示す問題があった。すなわち、電源供給領域および/または接地領域においてバンプ間の間隔が狭くなるため、電源バンプ等の間の短絡が生じやすくなり、それに起因する不良が増大するおそれがあった。また、これらのバンプの狭ピッチ化に対応し、配線基板側の電極パッドおよび配線の設計が複雑化するため、製造歩留りの低下が生じやすかった。さらに、配線基板と半導体チップとの間に絶縁性樹脂の封止層を形成する工程で、絶縁性樹脂の注入および充填作業が難しくなるため、充填不良が発生しやすいか、あるいはスループットが低下するという問題があった。

【0007】

なお、この種の関連技術として、半導体装置の一例が開示されている(例えば、特許文献1参照。)。

【特許文献1】特開2001−284402号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

本発明はこれらの問題を解決するためになされたもので、突起状電極(バンプ)を有する半導体装置において、半導体素子の電源供給系の電気抵抗に起因する電圧降下を低く抑えることを目的としている。

【課題を解決するための手段】

【0009】

本発明の一態様に係る半導体装置は、一方の主面に複数の電極パッドを有する配線基板と、一方の主面に複数の突起状電極を有し、この突起状電極形成面を下向きにして前記配線基板の前記電極パッド形成面上に搭載された半導体素子を備え、前記半導体素子の前記突起状電極と前記配線基板の対応する電極パッドとを接合して成る半導体装置であり、前記半導体素子の電源供給領域および/または接地領域に形成された前記突起状電極は長尺形状を有し、かつこれら長尺形状の突起状電極はそれぞれの長辺方向を平行に揃えて配列されていることを特徴とする。

【発明の効果】

【0010】

本発明の一態様に係る半導体装置によれば、電源供給系の電気抵抗に起因する電圧降下を低く抑えることができる。

【発明を実施するための最良の形態】

【0011】

以下、本発明を実施するための形態について説明する。なお、以下の記載では実施形態を図面に基づいて説明するが、それらの図面は図解のために提供されるものであり、本発明はそれらの図面に限定されるものではない。

【0012】

図1は、本発明の第1の実施形態に係る半導体装置の構成を示す断面図であり、図2は、第1の実施形態における半導体チップのバンプ(突起状電極)の配置を示す平面図である。また、図3は、図2の破線で囲まれた部分を拡大して示す図である。

【0013】

図1に示す第1の実施形態の半導体装置1は、一方の主面に複数の電極パッドを有するパッケージ用の配線基板2と、半導体チップ3を備えている。半導体チップ3は一方の主面である表面(素子形成面)に複数のバンプ(突起状電極)を有し、このバンプ形成面を下向きにして(フェースダウンで)配線基板2の電極パッド形成面上に搭載されている。

【0014】

図2に示すように、半導体チップ3の表面の周辺部には、円形状の複数の信号バンプ4が、所定の間隔(配設ピッチp)で配設されている。そして、このような信号バンプ4に取り囲まれた半導体チップ4の中央部には、複数の電源バンプ5とそれと同数のグランドバンプ6が、交互に並べて配設されている。電源バンプ5とグランドバンプ6は、いずれも長尺形状を有し、それぞれの長辺が半導体チップ3の少なくとも一辺に平行になるように配列されている。長尺形状の電源バンプ5とグランドバンプ6の配置間隔(配設ピッチ)は、信号バンプ4の配設ピッチpと等しくすることが好ましい。また、電源バンプ5とグランドバンプ6、および信号バンプ4の構成材料としては、スズ(Sn)をベースにした半田材料(Sn−Pb合金、Sn−Ag合金、Sn−Cu合金等)や、金(Au)、銅(Cu)等の単体金属を用いることができる。

【0015】

電源バンプ5およびグランドバンプ6の平面形状は、辺あるいは径がそれに直交する方向の辺あるいは径に比べて長尺に構成された形状(長尺形状)であればよい。長方形、平行四辺形、長楕円形等とすることができる。

【0016】

長尺形状の電源バンプ5およびグランドバンプ6の長辺あるいは長径の長さは、半導体チップ3の電源供給領域および/または接地領域の対応する長さ全体の1/3以上であれば、電源供給系の電気抵抗に起因する電圧降下抑制の効果を上げることができる。形成の容易さ等の点からは、電源供給領域および/または接地領域の長さと等しくすることが好ましい。

【0017】

配線基板2の半導体チップ搭載面においては、周辺部に信号バンプ接続用の円形状の電極パッド7が形成されている。また、中央部には、いずれも長尺形状を有する電源バンプ接続用の電極パッド8およびグランドバンプ接続用の電極パッド9が、交互に並べて配置されている。電源バンプ接続用の電極パッド8およびグランドバンプ接続用の電極パッド9の平面形状は、長尺形状であれば特に限定されず、長方形、平行四辺形、長楕円形などとすることができる。これらの電極パッド8,9は、対応する電源バンプ5およびグランドバンプ6と同一の形状および長さとし、かつこれらのバンプに対応する位置に配置することが好ましい。

【0018】

そして、半導体チップ3の各バンプが配線基板2の対応する電極パッドに接合されている。すなわち、半導体チップ3の円形状の信号バンプ4が配線基板2の信号バンプ接続用の電極パッド7に接合されており、半導体チップ3のいずれも長尺形状の電源バンプ5とグランドバンプ6が、配線基板2のいずれも長尺形状の電源バンプ接続用電極パッド8とグランドバンプ接続用電極パッド9にそれぞれ接合されている。

【0019】

また、配線基板2と半導体チップ3との間には、絶縁性樹脂が注入・充填され、絶縁性樹脂から成る封止層10が形成されている。さらに、配線基板2の半導体チップ搭載面と反対側の下面には、はんだボールのような外部接続用の電極(図示を省略する。)が配設されている。

【0020】

このように構成される第1の実施形態の半導体装置においては、図3に拡大して示すように、半導体チップ3の機能素子Aと長尺形状の電源バンプ5およびグランドバンプ6との距離の最大値がp/2となり、従来のバンプ配置に比べて大幅に短縮することができる。また、狭ピッチのバンプ配置に比べても、機能素子Aと電源供給用のバンプとの距離を短縮することができる。

【0021】

ここで、従来の半導体装置におけるバンプ配置を図4に示し、狭ピッチのバンプ配置を図5および図6に示す。図4に示すバンプ配置においては、電源バンプ52およびグランドバンプ53の配設ピッチは信号バンプ54の配設ピッチpの2倍になっており、半導体チップ51内の機能素子Aと電源バンプ52およびグランドバンプ53との距離の最大値はpとなっている。また、図5および図6に示す狭ピッチのバンプ配置では、半導体チップ51内の機能素子Aと電源バンプ52およびグランドバンプ53との距離の最大値は、√2p/2(<p)となる。

【0022】

第1の実施形態の半導体装置においては、このような従来のバンプ配置に比べて、機能素子Aと電源供給用のバンプとの距離を短縮することができるので、電源系の電圧降下を低減し、電気的特性に優れた半導体装置を得ることができる。

【0023】

また、第1の実施形態の半導体装置においては、電源バンプ5およびグランドバンプ6間の短絡が発生しにくく、製造歩留りが向上する。さらに、半導体チップ3の電源バンプ5とグランドバンプ6がそれぞれ長尺形状を有しており、これらのバンプと半導体基板2側の電極パッド8,9との接合面積が従来に比べて増大しているため、半導体チップ3から発生する熱を、これらの長尺形状のバンプ(電源バンプ5とグランドバンプ6)および半導体基板2側の長尺形状の電極パッド8,9を介して効率的に放散させることができる。こうして、熱膨張により発生する熱応力を効果的に分散することができるので、温度サイクルに対する寿命も向上する。またさらに、絶縁性樹脂の注入および充填作業が容易であり、充填不良が発生しにくいという利点がある。

【0024】

次に、本発明の別の実施形態について説明する。図7は、本発明の第2の実施形態に係る半導体装置の構成を示す断面図である。

【0025】

第2の実施形態において、半導体チップ3の素子形成面には、円形状の複数の信号バンプ4と、いずれも長尺形状の複数の電源バンプ5およびグランドバンプ6が、それぞれ第1の実施形態と同様に配設されている。

【0026】

配線基板2の半導体チップ搭載面において、周辺部には信号バンプ接続用の円形状の複数の電極パッド7が形成されている。また中央部にも、円形状の複数の電源バンプ接続用の電極パッド8とグランドバンプ接続用の電極パッド9がそれぞれ形成されている。これら電源バンプ接続用の電極パッド8およびグランドバンプ接続用の電極パッド9は、それぞれが列をなすように形成され、かつ電源バンプ接続用電極パッド8の列とグランドバンプ接続用電極パッド9の列が、半導体チップ3側の長尺形状の電源バンプ5およびグランドバンプ6に対応するように交互に配列されている。

【0027】

そして、半導体チップ3の円形状の信号バンプ4が、配線基板2の信号バンプ接続用の円形状の電極パッド7に接合されている。また、半導体チップ3の長尺形状の電源バンプ5が、配線基板2の対応する位置に形成された電源バンプ接続用の電極パッド8の列に接合され、半導体チップ3の長尺形状のグランドバンプ6が、配線基板2の対応する位置に形成されたグランドバンプ接続用の電極パッド9の列に接合されている。

【0028】

また、配線基板2と半導体チップ3との間には、絶縁性樹脂から成る封止層10が形成されている。さらに、配線基板2の半導体チップ搭載面と反対側の下面には、はんだボールのような外部接続用の電極(図示を省略する。)が配設されている。

【0029】

このように構成される第2の実施形態の半導体装置においては、第1の実施形態の半導体装置と同様に、半導体チップ3の機能素子Aと長尺形状の電源バンプ5およびグランドバンプ6との距離の最大値がp/2となり、従来からのバンプ配置に比べて、機能素子Aと電源供給用のバンプとの距離を短縮することができる。したがって、高性能デバイスにおける電源系の電圧降下を低減し、電気的特性に優れた半導体装置を得ることができる。

【0030】

また、配線基板2側の電源バンプ接続用の電極パッド8およびグランドバンプ接続用の電極パッド9の一部が欠損したとしても、同じ列に属する他の電極パッド8,9がそれを補って接続点となるため、半導体チップ3のバンプとの間に十分な電気接続が得られる。さらに、第1の実施形態に比べて、配線基板2の電極パッド8,9間の配線形成が可能であり、配線の自由度が大きいという利点がある。

【0031】

以上の実施形態で説明された構成、形状、大きさおよび配置関係については、概略的に示したものにすぎず、また各構成の組成(材質)等については例示にすぎない。したがって、本発明は以上の実施形態に限定されるものではなく、特許請求の範囲に示される技術的思想の範囲を逸脱しない限り、さまざまな形態に変更することができる。

【図面の簡単な説明】

【0032】

【図1】本発明の第1の実施形態に係る半導体装置の構成を示す断面図である。

【図2】第1の実施形態における半導体チップのバンプの配置を示す平面図である。

【図3】図2の破線で囲まれた部分を拡大して示す図である。

【図4】従来からの半導体装置における半導体チップのバンプ配置の一例を示す平面図である。

【図5】狭ピッチのバンプ配置を示す平面図である。

【図6】図5の破線で囲まれた部分を拡大して示す図である。

【図7】本発明の第2の実施形態に係る半導体装置の構成を示す断面図である。

【符号の説明】

【0033】

1…半導体装置、2…配線基板、3…半導体チップ、4…信号バンプ、5…電源バンプ、6…グランドバンプ、7…信号バンプ接続用の電極パッド、8…電源バンプ接続用の電極パッド、9…グランドバンプ接続用の電極パッド、10…絶縁性樹脂から成る封止層。

【特許請求の範囲】

【請求項1】

一方の主面に複数の電極パッドを有する配線基板と、一方の主面に複数の突起状電極を有し、この突起状電極形成面を下向きにして前記配線基板の前記電極パッド形成面上に搭載された半導体素子を備え、前記半導体素子の前記突起状電極と前記配線基板の対応する電極パッドとを接合して成る半導体装置であり、

前記半導体素子の電源供給領域および/または接地領域に形成された前記突起状電極は長尺形状を有し、かつこれら長尺形状の突起状電極はそれぞれの長辺方向を平行に揃えて配列されていることを特徴とする半導体装置。

【請求項2】

前記長尺形状の突起状電極の長辺の長さは、前記電源供給領域および/または接地領域の長さの1/3以上であることを特徴とする請求項1記載の半導体装置。

【請求項3】

前記半導体素子の長尺形状の突起状電極に対応する前記配線基板の電極パッドは、長尺形状を有しており、これらの長尺形状の電極パッドが、それぞれの長辺方向を平行に揃えかつ前記半導体素子の長尺形状の突起状電極と同じ向きに配列されていることを特徴とする請求項1または2記載の半導体装置。

【請求項4】

前記半導体素子の長尺形状の突起状電極に対応する前記配線基板の電極パッドは、円形を有しており、これらの円形の電極パッドの複数個が対応する前記長尺形状の突起状電極と接合されていることを特徴とする請求項1または2記載の半導体装置。

【請求項5】

前記半導体素子と前記配線基板との間に絶縁性樹脂の封止層を有することを特徴とする請求項1乃至4のいずれか1項記載の半導体装置。

【請求項1】

一方の主面に複数の電極パッドを有する配線基板と、一方の主面に複数の突起状電極を有し、この突起状電極形成面を下向きにして前記配線基板の前記電極パッド形成面上に搭載された半導体素子を備え、前記半導体素子の前記突起状電極と前記配線基板の対応する電極パッドとを接合して成る半導体装置であり、

前記半導体素子の電源供給領域および/または接地領域に形成された前記突起状電極は長尺形状を有し、かつこれら長尺形状の突起状電極はそれぞれの長辺方向を平行に揃えて配列されていることを特徴とする半導体装置。

【請求項2】

前記長尺形状の突起状電極の長辺の長さは、前記電源供給領域および/または接地領域の長さの1/3以上であることを特徴とする請求項1記載の半導体装置。

【請求項3】

前記半導体素子の長尺形状の突起状電極に対応する前記配線基板の電極パッドは、長尺形状を有しており、これらの長尺形状の電極パッドが、それぞれの長辺方向を平行に揃えかつ前記半導体素子の長尺形状の突起状電極と同じ向きに配列されていることを特徴とする請求項1または2記載の半導体装置。

【請求項4】

前記半導体素子の長尺形状の突起状電極に対応する前記配線基板の電極パッドは、円形を有しており、これらの円形の電極パッドの複数個が対応する前記長尺形状の突起状電極と接合されていることを特徴とする請求項1または2記載の半導体装置。

【請求項5】

前記半導体素子と前記配線基板との間に絶縁性樹脂の封止層を有することを特徴とする請求項1乃至4のいずれか1項記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2009−130074(P2009−130074A)

【公開日】平成21年6月11日(2009.6.11)

【国際特許分類】

【出願番号】特願2007−302498(P2007−302498)

【出願日】平成19年11月22日(2007.11.22)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成21年6月11日(2009.6.11)

【国際特許分類】

【出願日】平成19年11月22日(2007.11.22)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]