Fターム[5F044KK11]の内容

ボンディング (23,044) | フェイスダウンボンディング用配線基板 (5,003) | 電極部 (1,724)

Fターム[5F044KK11]の下位に属するFターム

Fターム[5F044KK11]に分類される特許

1 - 20 / 300

半導体デバイスおよびその製造方法

銅を含む電極連結構造体

配線基板及びその製造方法、半導体パッケージ

電子デバイス、及び電子機器

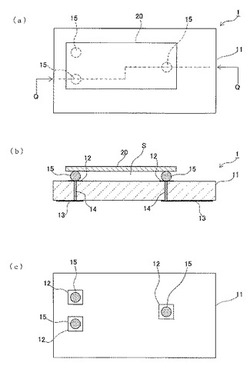

【課題】電子デバイスを小型化、低背化し、且つコストを低減する手段を得る。

【解決手段】電子デバイスは、第1の電子素子20と、第1の電子素子20を搭載する絶縁基板11と、を備えた電子デバイスであって、絶縁基板11は一方の主面に第1の電子素子20を搭載する電極パッド12を有すると共に、他方の主面に実装端子13を備え、第1の電子素子20に設けた端子と電極パッド12とは、接続用導電部材15を介して導通接続されている。

(もっと読む)

ウエハの接合方法及び接合部の構造

【課題】ウエハの接合部どうしをAuSn共晶接合する工程において、AuSnによる密着層の劣化を防ぐこと。

【解決手段】ウエハ1の表面に密着層4を形成し、密着層4の上方にAuSnとの濡れ性の悪い材料からなる拡散防止層7を積層する。さらに、拡散防止層7の縁よりも引っ込めて拡散防止層7の表面に接着層8を形成し、ウエハ1の表面に接合部3を形成する。一方、ウエハ11の下面に接合部13を設け、接合部13の下にAuSnハンダ層19を設ける。ウエハ1とウエハ11とを向かい合わせ、AuSnハンダ層19を溶融させて接合部3と接合部13をAuSnハンダ22によってAuSn共晶接合させる。

(もっと読む)

半導体装置

【課題】半導体パッケージを実装基板から取り外すリペアが容易であって、半導体パッケージと実装基板との接続部の耐衝撃性を向上させることができる半導体装置を提供する。

【解決手段】半導体装置100は、半導体素子4が接続された半導体パッケージ1と、実装基板2とがはんだバンプ3を介して電気的及び機械的に接続されてなり、半導体パッケージ1は、半導体素子4が接続されるとともに実装基板2と接続される半導体パッケージ用配線板5を有し、半導体パッケージ用配線板5に形成された電極パッド22のコア層11側には第1応力緩和層21が配置されており、実装基板2に形成された電極パッド33の層間絶縁層31側には第2応力緩和層34が配置されており、第1応力緩和層21の25℃の弾性率が2.5GPa以下であり、第2応力緩和層34の25℃の弾性率が3GPa以下かつ第2応力緩和層34の平面方向の25℃の熱膨張係数が8×10-6/℃以下である。

(もっと読む)

回路基板、半導体パワーモジュール、製造方法

【課題】半導体素子から多層基板への熱拡散性能の向上、および、多層基板と半導体素子との接合強度の向上。

【解決手段】半導体パワーモジュール10は、セラミックス多層基板100と、接合層110と、拡散層120と、半導体素子130を備える。接合層110は、セラミックス多層基板100の第1の面105上に配置され、半導体素子130とセラミックス多層基板100とを電気的に接続する導電接合部111と、半導体素子130とセラミックス多層基板100とを絶縁する絶縁接合部112とを備える平面状の薄膜層である。こうすれば、半導体素子130とセラミックス多層基板100との間における空隙の発生を抑制しつつ接合することができ、半導体素子130からセラミックス多層基板100への熱拡散性能、および、セラミックス多層基板100と半導体素子130との接合強度を向上できる。

(もっと読む)

半導体装置

【課題】本発明の目的は、半導体素子、及び半導体素子と多孔質状金属層との接合面等における、クラックや剥がれを抑制可能な半導体装置、及びその製造方法を提供する。

【解決手段】基板(K)またはリードフレーム(L)に設けられたパッド部(P)上に多孔質状金属層(C)を介して半導体素子(S)の金属層が接合されている半導体装置であって、前記多孔質状金属層(C)の外周側部位の金属密度がその内側に位置する中心側と比較して低いことを特徴とする半導体装置。

(もっと読む)

はんだ実装基板及びその製造方法、並びに半導体装置

【課題】 低コストで製造でき且つ実装信頼性に優れたはんだ実装基板及びその製造方法、並びに半導体装置を提供する。

【解決手段】 はんだ実装基板100は、銅を含む銅系金属層20を備える配線22及びはんだ実装部21を少なくとも一方面に複数備え、配線22及びはんだ実装部21の銅系金属層20が露出した領域に、銅と反応する官能基を少なくとも一つを有する有機化合物を反応させることにより、有機化合物からなる有機皮膜30を形成する工程と、有機皮膜30が形成されたはんだ実装部21の該有機皮膜30の一部を除去して開口31を設けて、銅系金属層20の一部を露出させる工程と、を具備する。

(もっと読む)

回路基板、半導体パワーモジュール、製造方法

【課題】半導体素子から多層基板への熱拡散性能の向上、および、多層基板と半導体素子との接合強度の向上。

【解決手段】半導体パワーモジュール30は、セラミックス多層基板300と、接合層310と、半導体素子330を備える。接合層310は、セラミックス多層基板100側が平面状に形成されている薄膜層である。接合層310の絶縁接合部312は、半導体素子330側の端部からセラミックス多層基板300側の端部に向けて先細な形状に形成されている。半導体素子130の実装時、半導体素子330の突状部335は窪み部316内に収められ、接合層310の導電接合部311と導通する。こうすれば、半導体素子330と接合層との接合面積を広く接合でき、多層基板と半導体素子との接合強度、絶縁性能を確保しつつ、半導体素子から多層基板への熱拡散性能を向上できる。

(もっと読む)

半導体装置

【課題】50ミクロンピッチ以下の微細ピッチ電極を有する半導体素子を基板上のパッドもしくは配線を接続する構造において、接続時の加熱または荷重負荷時に発生するバンプ間ショートや、高歪みによる接続部破断を防止しあるいは接触抵抗を低減し、高信頼性で高速伝送に対応可能な半導体装置を提供する。

【解決手段】基板20と半導体素子1は縦弾性係数(ヤング率)が65GPa以上600GPa以下のバンプ11と、錫、アルミニウム、インジウム、あるいは鉛のいづれかを主成分とする緩衝層12を介して接続されており、バンプ11と基板20上のパッドもしくは配線21の対向した面の少なくとも一方に突起が形成され、超音波により接続することにより低温接続が可能な半導体装置。

(もっと読む)

プリント配線板及びその製造方法

【課題】ソルダーレジスト層に良好な半田バンプの形成が可能な開口形状を備えるプリント配線板及びその製造方法を提供すること。

【解決手段】層間絶縁層と、上記層間絶縁層上に形成された導体パターンと、上記層間絶縁層上及び上記導体パターン上に設けられ、上記導体パターン上の少なくとも一部を露出する開口部を有するソルダーレジスト層と、上記開口部の内部に形成された半田バンプとを有するプリント配線板であって、上記開口部の形状は、平面視ティアドロップ形状又は平面視n角形状(n≧3)であることを特徴とするプリント配線板。

(もっと読む)

電子部品の実装構造体

【課題】接続部に不具合の生じにくい構造を備えた電子部品の実装構造体を提供する。

【解決手段】電子部品4の実装構造体10は、コアとなる樹脂の表面の長手方向に沿う複数箇所が金属からなる導電膜で覆われた構造を有するバンプ電極23を備えた電子部品4と、金属端子12を備えた基板11とを電気的に接続することで構成されており、バンプ電極23の金属端子12と接続される位置に、金属端子12との接触領域を少なくとも二分割する溝部が形成されている。

(もっと読む)

半導体デバイスウエーハの接合方法

【課題】異方性導電材料を用いた半導体デバイスウエーハ同士の接合方法を提供する。

【解決手段】複数の突起電極17を有する半導体デバイスが複数形成された第1半導体デバイスウエーハ11の該突起電極側を絶縁体10で被覆する絶縁体被覆ステップと、該絶縁体10が被覆された第1半導体デバイスウエーハ11の該突起電極側を平坦化するとともに該突起電極17の端面を露出させる突起電極端面露出ステップと、該突起電極17に対応した電極を有する第2半導体デバイスウエーハ24の該電極と第1半導体デバイスウエーハ11の該突起電極17とを異方性導電体28で接合し、該電極と該突起電極17とを接続する接合ステップと、を具備する。

(もっと読む)

半導体装置の製造方法

【課題】コストの上昇を抑えながら高い信頼性の接合を実現することができる半導体装置の製造方法を提供する。

【解決手段】半導体素子に設けられた第1の電極の表面の機械加工を行って、当該機械加工前よりも粒径が小さい微結晶の第1の層を設け、前記半導体素子が搭載される搭載部材に設けられた第2の電極の表面の機械加工を行って、当該機械加工前よりも粒径が小さい微結晶の第2の層を設ける(ステップS1)。前記第1の電極を構成する金属が固相拡散する温度未満、かつ前記第2の電極を構成する金属が固相拡散する温度未満の温度で、前記第1の層の表面に存在する酸化膜及び前記第2の層の表面に存在する酸化膜を還元する(ステップS2)。前記第1の層及び前記第2の層を互いに固相拡散接合する(ステップS4)。

(もっと読む)

異方性導電材料及び接続構造体

【課題】電極間の接続に用いた場合に、電極間の接続が容易であり、導通信頼性を高めることができる異方性導電材料、並びに該異方性導電材料を用いた接続構造体を提供する。

【解決手段】本発明に係る異方性導電材料は、導電性粒子1と、バインダー樹脂とを含む。導電性粒子1は、樹脂粒子2と、該樹脂粒子2の表面2aを被覆している導電層3とを有する。導電層3の少なくとも外側の表面層が、はんだ層5である。本発明に係る接続構造体は、第1の接続対象部材と、第2の接続対象部材と、該第1,第2の接続対象部材を接続している接続部とを備える。上記接続部が、上記異方性導電材料により形成されている。

(もっと読む)

電子部品およびモジュール

【課題】狭ピッチに形成されたバンプや柱状電極であっても、接合面積を増加させ、バンプと素子との接合部破断を防止できる電子部品およびモジュールを提供する。

【解決手段】素子11のパッド12上に形成されるバンプ15を、パッド12の長さ方向にパッド12よりはみ出して形成する。これによりバンプの接合面積を大きくすることができ、実装時に熱応力によるバンプ破断を抑制できる。また、バンプ同士が隣接する横方向にはみ出さないので、実装時に熱応力によるバンプ破断を抑制でき、隣接するバンプ間の距離を確保できるため、バンプ同士による短絡を防止することができる。

(もっと読む)

半導体チップ及び半導体装置

【課題】フリップチップ接続時における腹打ち現象を防止し、プローブテスト時のダメージに対する耐性を低下させることなく、配線のレイアウトの自由度を向上させる。

【解決手段】半導体チップは、外部素子と接続するパッド部15,25が形成されると共に、電源/GND配線16として利用されるパッドメタル層12と、パッドメタル層12と回路領域とを接続する複数の配線層13と、フリップチップ接続面5の周辺部に設けられプローブテストに利用される周辺パッド部15を含み、パッドメタル層12と少なくとも1つの配線層13とからなる積層構造を有する周辺パッド層18と、フリップチップ接続面5の周辺部より内側に設けられプローブテストに利用されない内部パッド部25を含み、パッドメタル層12のみからなる単層構造を有する内部パッド層28とを備える。

(もっと読む)

半導体装置

【課題】FC−BGAなどの半導体装置を適切に製造する技術を提供する。

【解決手段】チップ側電極(4)を有する半導体チップ(2)と、基板側電極(5)を有する基板(3)とを具備する半導体装置(1)を構成する。基板(3)は、基板側電極(5)が配置される基板側電極配置領域(8)と、チップ支持領域(9)とを備えている。その基板側電極配置領域(8)は、基板側電極(5)が配置される第1基板面(12)を有する。チップ支持領域(9)は、第1基板面(12)を含む面を基準面としたとき、基準面からの高さが第1高さ(h1)となる位置にチップ支持面を有する。そして、チップ支持面は、チップ面(11)の一部と向かい合う対向領域(21)を有する。

(もっと読む)

半導体装置

【課題】アンダーフィル樹脂の充填が困難な場合であっても、半導体装置の信頼性が低下することを防ぐ技術を提供する。

【解決手段】半導体チップ(2)と、基板(8)と、チップ面に形成されたチップ面絶縁層(7)と、基板面に形成された基板面絶縁層(10)と、フリップチップボンディングによってチップ側電極(4)と基板側電極(9)とを接続する接続部材(11)とを具備する半導体装置(1)を構成する。接続部材(11)は、チップ面絶縁層(7)を貫通するバンプ部分(12)と、基板面絶縁層(10)を貫通する低融点部分(13)と、バンプ部分(12)と低融点部分(13)とが接触している接触領域(16)とを備えることが好ましい。ここで、チップ面絶縁層(7)と基板面絶縁層(10)とは、空隙(14)を介して向かい合うように配置されている。そして、接触領域(16)は、空隙(14)によって露出される表面を有する。

(もっと読む)

1 - 20 / 300

[ Back to top ]