Fターム[5F044RR16]の内容

ボンディング (23,044) | ワイヤレスボンディング関連事項 (2,154) | 容器・封止 (1,675)

Fターム[5F044RR16]の下位に属するFターム

Fターム[5F044RR16]に分類される特許

1 - 20 / 141

エレクトロニクスアセンブリを製造する方法

【課題】アンダーフィル又は接着剤によって隣接する回路素子を汚染することなく、隣接する回路素子を物理的にできる限り近づけて配置できるようにするエレクトロニクスアセンブリを製造するための方法を提供する。

【解決手段】基板12上に液体障壁30を形成することと、液体障壁の一方の側に第1の回路素子22を配置することと、液体障壁の反対側に第2の回路素子24を配置する。液体44が第1の回路素子に塗布される。第1の回路素子と第2の回路素子との間の間隔を最小にすることができるように、液体障壁を用いて、第1の回路素子に塗布された液体が第2の回路素子を汚染するのを防ぐ。

(もっと読む)

半導体チップ、半導体装置および半導体装置の製造方法

【課題】バンプ電極同士の横滑りを防止し、バンプ電極同士を接合する接合材料のはみ出しを抑制する。

【解決手段】

半導体チップ10は、基板17と、基板17の一方の面に設けられた第1のバンプ電極50と、基板17の他方の面に設けられた第2のバンプ電極60と、第1のバンプ電極50と第2のバンプ電極60のうちの少なくとも一方の頂面に形成された導電性の接合材料層61と、を有している。第1のバンプ電極50の頂面は凸面54であり、第2のバンプ電極60の頂面は凹面63である。

(もっと読む)

フリップチップ型半導体裏面用フィルム、及び、ダイシングテープ一体型半導体裏面用フィルム

【課題】半導体素子を保護することができ、且つ、半導体素子の貼り剥がしを容易とするフリップチップ型半導体裏面用フィルムを用いた半導体装置の製造方法を提供する。

【解決手段】 ダイシングテープとフリップチップ型半導体裏面用フィルムとを備えるダイシングテープ一体型半導体裏面用フィルムを用いた半導体装置の製造方法であって、フリップチップ型半導体裏面用フィルムは、半導体素子の裏面に形成する際に半導体素子の裏面に対向しない側の表面粗さ(Ra)が、硬化前において、50nm〜3μmの範囲内であり、ダイシングテープ一体型半導体裏面用フィルム上に半導体ウエハを貼着する工程と、半導体ウエハをダイシングする工程と、ダイシングにより得られた半導体素子をピックアップする工程と、半導体素子を被着体上にフリップチップ接続する工程とを具備する半導体装置の製造方法。

(もっと読む)

電子機器、及び電子部品のリワーク方法

【課題】半導体パッケージを母基板へリワークするときのリフローによる熱応力が母基板に直接加わらないような半導体パッケージのリワーク方法を提供する。

【解決手段】リワーク部品1と母基板2との間に、リワーク部品1の各ボール電極1aと対応する位置に孔4aを開けて導電剤3を充填した異方性導電材料からなる半硬化状態の樹脂平板4を介在させる。樹脂平板4は、熱硬化性を有していてリワーク時においてリワーク部品1と母基板2とに接着される。また、樹脂平板4の孔4aに充填された導電剤3がリワーク部品1のボール電極1aと母基板2のランド2aとを電気的に接続する。更に、取り外された半導体部品の切削後に塗布された半田ペースト5によりリワーク部品1のボール電極1aと母基板2のランド2aとが半田付けされ、かつ、アンダーフィル樹脂6が母基板2と樹脂平板4との隙間に充填される。

(もっと読む)

半導体装置

【課題】封止材の充填不良(ボイド)が抑制され、封止材の注入速度を速めることを可能な半導体装置を提供する。

【解決手段】半導体装置1は、半導体チップ10に形成された電極をなす複数の外部端子11と、パッケージ基材20に形成された複数の引出配線21とが接合され、複数の外部端子11及び複数の引出配線21が封止材により封止されたものである。半導体チップ10においては、複数の外部端子11からなる外部端子列12が、外部端子列12の延びる方向に対して交差する方向に複数配列しており、かつ、複数の外部端子列12において、複数の外部端子11のうち2以上がチップ辺10Eに対して交差する方向に同軸配列している。

(もっと読む)

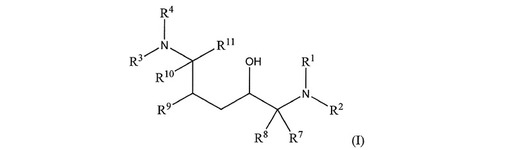

硬化性アミンフラックス組成物およびはんだ付け方法

【課題】電機部品における信頼性のあるはんだ付けされかつ封止された相互接続の製造を容易にする硬化性フラックス材料を提供する。

【解決手段】分子あたり少なくとも2つのオキシラン基を有する樹脂成分式Iのアミンフラックス剤、並びに、場合によっては硬化剤を当初成分として含む硬化性アミンフラックス組成物とする。

(式中、R1、R2、R3およびR4は独立して水素等、R7およびR8は独立してC1−20アルキル基等、R10およびR11は独立してC1−20アルキル基等、R9は水素等から選択される)

(もっと読む)

半導体装置の製造方法

【課題】半導体チップの組立工程におけるハンドリング性を向上し、しかも、半導体チップの損傷を回避する半導体装置の製造方法を提供すること。

【解決手段】ダイシングライン16によって区画された複数の半導体チップ4を含む半導体ウエハ2を準備する第1の工程と、半導体ウエハ2に支持板13を付着する第2の工程と、半導体ウエハ2および支持板13をダイシングライン16に沿って切断し、半導体チップ4および分割された支持板13からなる積層体3を形成する第3の工程と、積層体3を配線基板18に搭載し、積層体3の半導体チップ4および配線基板18を電気的に接続する第4の工程とを有する半導体装置1の製造方法。

(もっと読む)

実装装置および実装方法

【課題】 微細な半田バンプが形成されたチップであっても、基板に良好に熱圧着することができる実装装置および実装方法を提供すること。

【解決手段】 チップに設けられた半田バンプを、基板に設けられた電極に、押圧しながら加熱し熱圧着する実装装置および実装方法であって、チップを保持して基板に押圧する熱圧着ツールと、基板を保持する基板ステージと、熱圧着ツールを加熱する加熱手段と、熱圧着ツールの高さ位置の制御を行う制御部とを備え、制御部が、チップを保持した熱圧着ツールを下降し、チップの基板側に設けられている半田バンプが基板に設けられている電極に接触した後、所定量だけ熱圧着ツールを用いてチップを基板の電極に押し込み、半田バンプの温度が半田溶融温度に到達する前に、熱圧着ツールの高さ位置を熱圧着ツールの伸びに応じて上昇させる機能を有している実装装置および実装方法を提供する。

(もっと読む)

樹脂組成物、及び電子装置の製造方法

【課題】電極端子の接続信頼性が高い樹脂組成物、及びこの樹脂組成物を用いて製造する電子装置の製造方法を提供する。

【解決手段】第一基板110の半田バンプ111と第二基板120の半田バンプ121とを半田接合する際に、第一基板110の半田バンプ111と第二基板120の半田バンプ121との間に導入され、半田接合した後に熱硬化する樹脂組成物130であって、前記樹脂組成物は、熱硬化性樹脂を含み、180℃、及び250℃におけるゲルタイムが100秒以上である。

(もっと読む)

半導体装置の製造方法

【課題】半導体ウエハにBG工程を施すと、研削された半導体ウエハの面に破砕層が形成される。この破砕層は、半導体ウエハの内部への不純物の侵入を抑制する効果を有している。一方、半導体装置の薄型化に伴い、半導体ウエハの厚さを更に薄くしなければならない。そのため、半導体ウエハの抗折強度は従来に比べて低下してきており、薄くなった半導体ウエハに破砕層が形成されていると、半導体ウエハにクラックが発生する恐れがある。そこで、半導体ウエハの抗折強度を向上するために、BG工程の後に、ストレスリリーフを行うことが有効とされている。しかし、破砕層を除去してしまうと、ゲッタリング効果は低下してしまう。

【解決手段】本願発明は、半導体装置の製造方法において、そのデバイス面に集積回路が形成されたウエハの裏面に対して、バックグラインディング処理を実行した後、裏面の破砕層が残存するように、同裏面に保護膜を形成するものである。

(もっと読む)

半導体装置及びその製造方法

【課題】種類の異なる半導体チップの間で接合不良が発生することを防止した半導体装置及びその製造方法を提供する。

【解決手段】配線基板2の一面に実装されたチップ積層体3は、配線基板2の一面とは反対側から順に、一面側に第1のバンプ電極12と他面側に第2のバンプ電極13とを有する複数のメモリーチップ10a〜10dを、それぞれの一面と他面とを対向させながら、それぞれの間にある第1のバンプ電極12と第2のバンプ電極13とを接合して積層し、その上に、一面側に第3のバンプ電極15と他面側に第4のバンプ電極16とを有するロジックチップ11を、その一面と、その下にあるメモリーチップ10dの他面とを対向させながら、その間にある第2のバンプ電極13と第3のバンプ電極15とを接合部材18を介して接合して積層した構造を有する。

(もっと読む)

電子パッケージのはんだ接合用アンダーフィル材選択支援装置、電子パッケージのはんだ接合用アンダーフィル材選択支援プログラム、電子パッケージのはんだ接合用アンダーフィル材の最適物性値算出方法

【課題】実験等の手間を不要とし、効率よく、信頼性の高い電子パッケージを実現可能なはんだ接合用アンダーフィル材選択支援装置等を提供する。

【解決手段】 電子パッケージを構成するアンダーフィル材以外の各部材の寸法に基づいて、有限要素モデルを作成し、電子パッケージを構成する複数のはんだボールのうち、2以上のはんだボールを、最大変位又は最大応力又は最大歪みを有する注目はんだボールとして決定する。注目はんだボールの一部を節点とし、電子パッケージの温度環境情報と各部材の物性値に基づいて、節点の変位を算出し、アンダーフィル材の物性値を最適化の変数Xとして定義して、算出された2つの節点の変位の差(NDi(x,y,z)−NDj(x,y,z))に基づいて目標関数F(X)の値を算出し、目標関数F(X)の値が最小値に収束する変数Xをアンダーフィル材の最適物性値として提示する。

(もっと読む)

半導体装置の製造方法およびそれを用いてなる半導体装置、並びに電気、電子部品の製造方法およびそれを用いてなる電気、電子部品

【課題】 フラックス洗浄工程が不要で生産性に優れ、かつ半導体ウエハの裏面を研削した際の反りを低減することが可能な半導体装置の製造方法およびその製造方法で製造された半導体装置を提供すること。

【解決手段】 上記課題は、第1の接続電極が設けられた回路面を有する半導体ウエハの回路面にフラックス機能を有する樹脂組成物層およびバックグラインドテープをこの順に形成する第1の工程と、前記半導体ウエハの回路面とは反対側の面を研削する第2の工程と、前記半導体ウエハの回路面とは反対側の面にダイシングテープを積層する第3の工程と、前記バックグラインドテープを剥離する第4の工程と、前記フラックス機能を有する樹脂組成物層および半導体ウエハを個片化することにより前記フラックス機能を有する樹脂組成物層付き半導体チップを得る第5の工程と、さらに2つの工程を有する半導体装置の製造方法とすることにより解決することができる。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】配線とはんだバンプとの接合強度の低下を抑制し、かつ配線と半導体チップとの接合強度の低下を抑制する。

【解決手段】開口部80を有する配線基板100上に設けられた配線110と、配線110の一部であり、配線基板100上に位置するランド部112、及び配線基板100上から開口部80内に延伸するリード部114と、ランド部112に形成されるはんだバンプ50と、平面視で開口部80の内側に位置し、リード部114と接続する半導体チップ10と、を備え、配線110は、Cuを含む材料により構成され、ランド部112のうちはんだバンプ50が形成される面上には、Niめっき層が形成され、リード部114のうち半導体チップ10と接続する面上、及び側面上にはNiめっき層が形成されておらず、ランド部112のうちはんだバンプ50が形成される面上、及びリード部114には、Auめっき層が形成されている。

(もっと読む)

フリップチップ型半導体裏面用フィルム

【課題】被着体上にフリップチップ接続された半導体素子に反りが発生するのを抑制又は防止することが可能なフリップチップ型半導体裏面用フィルム、及びダイシングテープ一体型半導体裏面用フィルムを提供する。

【解決手段】本発明のフリップチップ型半導体裏面用フィルムは、被着体上にフリップチップ接続された半導体素子の裏面に形成するためのフリップチップ型半導体裏面用フィルムであって、熱硬化後の23℃における引張貯蔵弾性率が10GPa以上50GPa以下であることを特徴とする。

(もっと読む)

布製半導体素子のパッケージ及びその製造方法

【課題】着用した際の異物感を最小限に抑えると共に、生産性が向上した布製半導体素子のパッケージ、その布製半導体素子のパッケージの製造方法を提供する。

【解決手段】布製半導体素子のパッケージは、織布と、前記織布上に導電材をパターニングして形成された第1リード部と、を有する布製印刷回路基板と、前記布製印刷回路基板のリード部に接続された電極部を有する半導体素子と、前記布製印刷回路基板と、前記半導体素子とを密封する成形部(molding)と、を含む。前記第1リード部は、前記第1リード部の端部において別の布製半導体素子と電気的に接続された導電性繊維によって前記織布とともに縫合されることにより、あるいは、前記第1リード部は、前記第1リード部の端部において別の布製半導体素子と電気的に接続された布製印刷回路基板の第2リード部と前記織布と共に縫合されることにより、前記別の布製半導体素子と電気的に接続されている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】歩留まりを低下させることなく、複数の半導体装置を一括形成することが可能な方法を提供すること。

【解決手段】支持板19上に金属膜21を形成する工程と、この金属膜21上に、係合部を有する複数の接続プラグ18を形成する工程と、それぞれの接続プラグ18の係合部内に、複数の半導体チップ13にそれぞれ設けられた各突起電極17を挿入し、かつ接触させることにより固定するとともに、複数の半導体チップ13を絶縁樹脂15−1で覆う工程と、少なくとも突起電極17を接続プラグの係合部内に挿入、接触させた後に、絶縁樹脂15−1を硬化させる工程と、少なくとも金属膜21をエッチングすることにより、接続プラグ18に電気的に接続された配線パターン16を形成する工程と、配線パターン16の一部に電気的に接続されるとともに、配線パターン16の他の部分とはソルダーレジスト膜14により絶縁されるように半田ボール12を形成する工程と、それぞれの半導体チップ13の周囲およびその上方の絶縁樹脂15−1を切断する工程と、を具備する。

(もっと読む)

導電接続シートの製造方法、端子間の接続方法、接続端子の形成方法、半導体装置および電子機器

【課題】金属層に亀裂や皺が生じることなく、金属層と樹脂組成物層との間で優れた密着性が維持された導電接続シートを製造することができる導電接続シートの製造方法、かかる製造方法により製造された導電接続シートを用いた端子間の接続方法、接続端子の形成方法、信頼性の高い半導体装置、および、電子機器を提供すること。

【解決手段】本発明の導電接続シートの製造方法で製造される導電接続シート1は、樹脂組成物層11、13と、樹脂組成物層11、13同士の間でこれらに互いに接合する金属層12とを有するものであり、この導電接続シート1は、樹脂組成物層11と金属層12とを備えるシート51および樹脂組成物層13を備えるシート52をそれぞれ用意する工程と、金属層12の樹脂組成物層11と反対側の面と、樹脂組成物層13の一方の面とが対向するようにして、シート51とシート52とを圧着する工程とを経ることにより製造される。

(もっと読む)

テープキャリア、テープキャリア型半導体装置、およびテープキャリア型半導体装置の製造方法

【課題】スプロケットホールのピッチの整数倍でテープキャリアの搬送を行うことができ、かつ、材料コストを低減できる半導体装置用テープキャリアを実現することにある。

【解決手段】本発明に係るテープキャリア10は、複数の半導体素子11を搭載してなるテープキャリア型半導体装置1に用いられ、長尺の絶縁テープ12からなり、複数の半導体素子11に対応する複数の配線パターン13を備えるものであって、搬送のためのスプロケットホール16がテープキャリア10の長尺方向に並んで形成されており、複数の配線パターン13は、所定数の配線パターン13毎に配線パターンセットを形成し、テープキャリア10の長尺方向に並ぶ配線パターン10の配置ピッチは、スプロケットホール16のピッチの非整数倍であり、テープキャリア10の長尺方向に並ぶ配線パターンセットの配置ピッチは、スプロケットホール16のピッチの整数倍である。

(もっと読む)

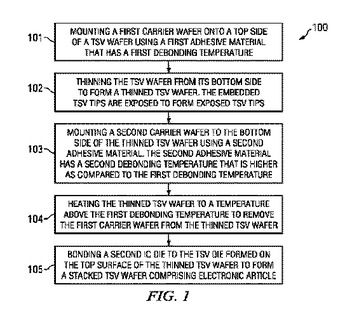

ICダイ又はウエハをTSVウエハに接合するためのデュアルキャリア

シリコン貫通ビア(TSV)ウエハを用いてスタックされた電子的部品を形成する方法が、第1ディボンデング温度を有する第1接着性材料(206)を用いてTSVウエハ(202)の上側に第1キャリアウエハ(205)を搭載することを含む。TSVウエハは、その下側から薄くされて薄くされたTSVウエハ(202’)を形成する。第1ディボンデング温度より高い第2ディボンデング温度を有する第2接着性材料(207)を用いて、TSVウエハ(202’)の下側に第2キャリアウエハ(215)が搭載される。薄くされたTSVウエハ(202’)はそれから第1キャリアウエハ(205)を取り除くため、前記第1ディボンデング温度を超える温度まで加熱される。スタックされた電子的部品を形成するため、少なくとも1つの個片化されたICダイが、薄くされたTSVウエハの上面上に形成されたTSVダイに結合される。

(もっと読む)

(もっと読む)

1 - 20 / 141

[ Back to top ]