株式会社東芝により出願された特許

54,421 - 54,430 / 54,554

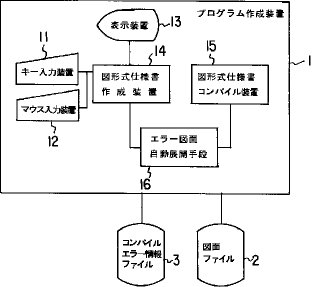

プログラム作成装置

【目的】 この発明は、エラー発生図面を自動展開し、エラー発生個所を明示することにより、エラー修正時の作業手順を簡素化し、エラーの修正漏れを防止し、プログラム開発効率を高めることにある。

【構成】 コントローラプログラムの動作を図形表現化した図面を作成し、この図面からオブジェクトプログラムを作成する装置において、この図面を格納する図面ファイル2と、エラー情報を格納するエラー情報ファイル3と、図面コンパイル時にエラーが発生したとき、図面ファイルの該当図面からエラー情報を読み出してエラー情報ファイルに格納する図形式仕様書コンパイル装置15と、エラーの発生時に起動し、図面ファイルからエラー発生図面を読み出して表示し、エラー情報ファイルからエラー情報を読み出してエラー発生個所を識別可能に表示する図形式仕様書作成装置14とを設けたプログラム作成装置である。

(もっと読む)

ATMセル化装置

【構成】 入力情報を蓄積しつつ、入力情報がATMセルのペイロード部に格納する格納予定情報量以上になると随時出力する蓄積手段と、この手段から格納予定情報が出力されたならば、格納予定情報からATMセルを生成して外部に出力し、ATMセルが生成されなければ、他のATMセルを外部に出力するATMセル化手段とで構成される。

【効果】 蓄積手段の蓄積情報量がATMセルのペイロードの格納予定情報量以上かどうかによって、有効セルかその他のセルをATMセルとして送出するので、ATMセル化装置の下流にATM側インターフェースとの速度を揃えるための速度整合用のバッファを用意する必要がない。

(もっと読む)

回転電機の検査装置

【目的】 測定者による測定値のバラツキをなくし、高精度で容易に能率良く測定すること。

【構成】 回転電機の整流子片3間の位置を検出すると共に、電機子巻線2に接続された2個の整流子片3間に電流を通電し、その間の電圧降下を検出する第1手段6,10,11と、整流子片間の位置を検出する度に前記電流と電圧降下を記録する第2手段7,8,12〜17を設けたもの。

(もっと読む)

発電電動機系統並入制御装置

【目的】 発電電動機を系統に並入する場合に、同期速度レベルに達するまでの起動時間を最短にするとともに、同期速度レベルに達した後の加速度一定制御においても、GD2 等による時間遅れを生じることがなく系統への並入に要する時間を最短にする。

【構成】 検出回転数25が同期処理検出値31よりも小さいか否かにより、変化率選択回路101は起動時であるか同期時であるかを判断し、起動時変化率32又は同期時変化率38を選択する。トルク/電流特性出力回路102は、選択された変化率と検出回転数25とを入力し、電流目標値35を出力する。電流調整回路103は、この目標値35と検出電流23との比較に基いて電流減信号又は電流増信号を出力し、電流調整制御を行う。

(もっと読む)

半導体ウエハ処理液

【目的】 パ―ティクルとともに金属不純物を半導体ウエハ表面から充分に除去することが可能な半導体ウエハ処理液を提供する。

【構成】 水性溶媒を主成分とし、前記水性溶媒中に下記一般式で示されるヒドラゾン誘導体及びその互変異性体の少なくとも1種を添加成分として含有する。

【化1】

(式中、R1 ,R2 はアシル基またはo位の少なくとも一方がヒドロキシ基、カルボニル基及びこれらの塩のいずれか1種で置換された芳香族炭化水素基もしくは芳香族複素環基、R3 は水素原子または置換されていてもよい芳香族炭化水素基、複素環基、脂肪族炭化水素基もしくは脂環式炭化水素基を表す。)

【効果】 半導体ウエハ表面を極めて清浄な状態にすることができる。

(もっと読む)

実装回路装置

【目的】 比較的簡略な構成を採りながら、TCPなど能動素子の動作に伴う発熱を効率よく放熱することが可能で、所要の高機能を呈する実装回路装置(モジュール)の提供を目的とする。

【構成】 プリント配線板4と、前記プリント配線板4の一主面に実装、配置された少なくとも1個のテープ・キャリア・パッケージ(TCP)5ないしベアーチップを含む複数の能動素子と、前記プリント配線板4の他主面側に離隔・配置されたヒートシンク6と、前記ヒートシンク6およびプリント配線板4間に配置され両者を離隔・保持して一体化するスペーサ7と、前記TCP5を含む各能動素子が実装・配置されたそれぞれの領域でプリント配線板4を遊嵌的に貫通し各別に能動素子5下面およびてヒートシンク6面を熱的に接続する伝熱体8とを具備して成ることを特徴とする。

(もっと読む)

窒化アルミニウム基板とその製造方法

【目的】 メタライズ層の形成にあたって、接合強度の低下や外観不良の発生等を再現性よく抑制することを可能にした窒化アルミニウム基板とその製造方法を提供する。

【構成】 窒化アルミニウムの結晶粒11a間に、主に焼結助剤成分からなる粒界相12を有する焼結体11からなる窒化アルミニウム基板であって、その表面には結晶粒11aの周辺部に、粒界相の脱落部に相当する凹部14が設けられている。このような窒化アルミニウム基板15は、窒化アルミニウム焼結体11に表面加工を施し、表面にしみ出した粒界相成分13を除去して後、超音波等を併用した、窒化アルミニウム自体には影響を及さないエッチング処理を施すことによって得られる。

(もっと読む)

トリミング回路

【目的】 トリミング箇所を増やしたり、トリミングステップを細かくしても、ピン数をほとんど増やすことなくチップ封止後のトリミングを可能にした。

【構成】 ツェナーザップダイオード11〜13を、スイッチング用トランジスタQ14〜Q16により選択的にザッピングする。スイッチングトランジスタQ14〜Q16は、デコーダ回路B11のデータに基づいてオンオフ状態を制御する。

(もっと読む)

無停電電源装置の制御方式

【目的】本発明は、電子計算機本体と無停電電源装置との間に相互に情報を送受するインターフェイスを備えて、電子計算機本体が無停電電源装置を監視できるようにしたことを特徴とする。

【構成】電子計算機本体1と無停電電源装置2との間を双方向のデータ転送ライン31によりインターフェイス接続し、電子計算機本体1には、上記データ転送ライン31を介して上記無停電電源装置2にコマンドを発送する手段と、上記無停電電源装置2より受けた電源状態情報の内容を解読し処理する手段とを有し、上記無停電電源装置2には、電源状態を監視し停電発生を検知する手段と、停電発生検知情報及び上記コマンドに従うレスポンスを上記データ転送ラインを介して上記電子計算機本体1に送付する手段とを有してなることを特徴とする。

(もっと読む)

絶縁ゲート型半導体装置

【目的】 IGBTの最大電流遮断能力は大きなままで、十分に低いオン抵抗を持つ絶縁ゲート型半導体装置を提供すること。

【構成】 p+ 型エミッタ層11,n- 型高抵抗ベース層12,p型ベース層13,n+ 型ソース層14,ゲート電極17及び主電極18,19等からなる縦型のIGBTのカソード側オンチャネル15とオンチャネル15′の間に、カソード電極18には接していないn+ 型エミッタ層22,このn+ 型エミッタ層22を覆うp型ベース21を有するサイリスタ構造を設けた絶縁ゲート型半導体装置において、このサイリスタ構造とIGBT部分の面積比を最適な範囲に設定するべく、各層の厚み方向と直交する横方向の単位セルサイズを120μm以下としたことを特徴とする。

(もっと読む)

54,421 - 54,430 / 54,554

[ Back to top ]