ローム株式会社により出願された特許

3,441 - 3,450 / 3,539

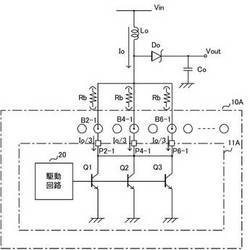

半導体装置及びそれを用いた電源回路装置

【課題】グリッドアレイ端子構造の半導体装置において、スイッチ回路がつながる端子の発熱を低減して溶解の危険性を少なくすること。

【解決手段】BGAなどのグリッドアレイ端子構造の半導体装置に内蔵されるスイッチ回路の出力端を、グリッドアレイ端子のうちの複数の端子に接続する。これにより、1つのアレイ端子に流れる電流を許容電流レベル内に低減し、また、ICソケットとの接触抵抗による発熱量を低減する。また、複数の端子の各端子間に1つ以上の他の端子が存在するように配置し、また、複数の端子の全てをグリッドアレイ端子のうちの最外周に配置する。

(もっと読む)

固体電解コンデンサにおけるプリント配線基板に対する実装構造及びネットワーク構造

【課題】 プリント配線基板5に、固体電解コンデンサを実装する場合に、スペースを縮小して、小型・軽量化を図る。

【解決手段】 弁作用金属粉末によるチップ体2及びこのチップ体の一端面から突出する陽極棒3並びに前記チップ体の表面に形成した陰極膜4にて構成されるコンデンサ素子1を、前記陽極棒の軸線と直角方向の厚さ寸法T0を前記プリント配線基板における板厚さTと略等しくするかこの板厚さ以下に薄くした扁平な形状にする一方、前記プリント配線基板5には、抜き孔10を、その表面における一対の配線パターン6,7の各々に電気的に導通するように設けたスルーホール8,9が当該抜き孔内に露出するように穿設し、この抜き孔内に、前記コンデンサ素子を、その陽極棒及び陰極膜が前記各スルーホールに電気的に接続するように装填する。

(もっと読む)

電源装置および電子機器

【課題】シリーズ型にチャージポンプ型昇圧回路を併用した電源装置において、過電流制限動作における垂下特性を緩やかにして、電流制限値を超えた負荷電流をも安定して供給可能にし、また電流制限時の発振状態を抑制すること。

【解決手段】調整電圧Vcpを出力するシリーズレギュレータ(12、30、21、22)と、この調整電圧Vcpを昇圧して出力電圧Voutを出力するチャージポンプ型昇圧回路20とを直列に接続し、出力電圧Voutを定電圧にするようにシリーズレギュレータを制御する。そして、電流検出回路40によりシリーズレギュレータの主回路電流I1を電流制限の対象とし、超過電流作成回路50は、電流検出値が電流制限基準値を超過した分に応じた超過信号を発生し、この超過信号に応じて電圧制御信号を低減する。

(もっと読む)

ALC付き増幅装置およびそれを用いた電子機器

【課題】携帯電話機等の音声の入出力機能を有するモバイル型電子機器に好適なALCを有する増幅装置において、アタック動作時とリカバリ動作時の両方で自然な聴感を得ることができるとともに、頻繁なアタック動作とリカバリ動作の繰り返しをさけること。

【解決手段】第1所定時間T1毎にアタックタイミングTaを出力するアタック用カウンタ50と、第2所定時間T2毎(T1<T2)にリカバリタイミングTrを出力するリカバリ用カウンタ70とをそれぞれ設ける。これにより、増幅利得を下げるアタック動作が、増幅利得を上げるリカバリ動作より速く行われるから、アタック動作時とリカバリ動作時の両方で自然な聴感を得る。

(もっと読む)

半導体装置

【課題】 処理速度を低下させることなく、共有されるメモリの使用効率の向上を実現する半導体装置を提供することを目的とする。

【解決手段】 複数のタスクを切換えて行う半導体装置10であって、行われるタスクに応じて夫々に所定の演算処理を行う複数のCPU1、2と、CPU1、2の間で共有される1つのメモリ空間を全体として有するメモリMEM1、2、3、4とを備えている。割当制御回路3は、タスク毎にCPU1、2が必要とするメモリサイズを記憶しており、行われるタスクに応じてセレクタSEL1、2、3、4及びマルチプレクサMUX1、2を制御することにより、CPU1、2の夫々に必要なメモリサイズ分のメモリを割り当てる。

(もっと読む)

マルチサンプリングレートΣΔDACシステム、及び音響機器

【課題】共通のΣΔDAC装置を用いて、異なるサンプリングレートでサンプリングされた複数のディジタル入力信号を変換する際のS/N比を向上する、マルチサンプリングレートΣΔDACシステムを提供すること。

【解決手段】可聴周波数領域のほぼ上限側周波数の2倍以下のサンプリング周波数でサンプリングされた第1ディジタル入力信号をサンプリングレート変換して第1アップディジタル入力信号を形成する。この第1アップディジタル入力信号と高サンプリング周波数の第2ディジタル入力信号とを選択して、ΣΔDAC装置に供給して、アナログ信号を出力する。

(もっと読む)

半導体装置の製造方法

【課題】 貫通電極を有した半導体装置の製造方法において、工程を簡略化して製造コストを極力低く抑えると共に、歩留まりの向上を図る。

【解決手段】 半導体基板10の表面に第1の絶縁膜11を形成し、その一部をエッチングして、半導体基板10の一部を露出する開口部11aを形成する。次に、開口部11a内から第1の絶縁膜11上に延びるパッド電極12を形成する。半導体基板10の裏面上には第2の絶縁膜15を形成する。次に、開口部11aよりも大きい開口径を有したビアホール16を形成する。そして、ビアホール16内から第2の絶縁膜15上に延びる第3の絶縁膜17を形成し、ビアホール16の底部の第3の絶縁膜17をエッチングしてパッド電極12を露出する。その後、ビアホール16内に貫通電極19及び配線層20を形成する。最後に、半導体基板10を複数の半導体チップ10Aに切断分離する。

(もっと読む)

半導体発光装置

【課題】 LEDチップから出射される光を効率よく正面側に反射させて明るい輝度を得ることができると共に、樹脂成形体からの出っ張りを無くして非常に小形化することができる、サイドビュー型の半導体発光装置を提供する。

【解決手段】 板状体から形成され、先端部に椀状の凹部1aが設けられる第1のリード1と、第2のリード2とが並設され、第1のリード1の先端部の一部が板状体の面と平行に変位して第1の実装面1bとされ、第2のリード2の先端部も板状体の面と平行に変位して第2の実装面2bとされている。凹部1a内には、LEDチップ3がマウントされ、その2つの電極は第1および第2のリード1、2と接続手段4により電気的に接続されている。そして、第1および第2の実装面1b、2b並びにリードの切断面を除いて全面が樹脂成形体5により被覆されている。

(もっと読む)

画像形成装置

【課題】 レンズを具備せずに適切に画像を形成することができる画像形成装置を提供する。

【解決手段】 本発明により提供される画像形成装置は、光透過性を有する基板31と複数の表示素子33とを有する有機ELパネル3を、感光性記録媒体22を露光するための手段として備える。基板31は、感光性記録媒体22に対向するための第1面31a、これとは反対の第2面31b、並びに当該第1面31aおよび第2面31bにより規定される厚さTを有している。複数の表示素子33は、相互に離隔して第2面31b上に設けられ、且つ、各々、感光性記録媒体22に向けて光を出射可能である。基板31の屈折率をnとし、複数の表示素子33において隣り合う表示素子33間の最小離隔距離をSとすると、基板31の厚さTは下記の式(1)を満たしている。

【数1】 (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 大電流を流す場合や長期間使用する場合の信頼性が高く、かつ、腐食に対する信頼性の高い配線を備えた半導体装置およびその製造方法を提供する。

【解決手段】 銅配線層30と、銅配線層30に比べ酸素による腐食の少ないアルミ配線層32を銅配線層30の上に形成した積層構造の配線層33を形成する。したがって、配線層33が銅配線層30を有するため、エレクトロマイグレーションによる断線が生じ難く、大電流を流す場合や長期間使用する場合の信頼性を向上させることができる。また、配線層33形成後に配線層33が露出した状態で酸素を含む雰囲気中における処理を行なう場合でも、配線層33が腐食されにくい。すなわち、大電流を流す場合や長期間使用する場合の信頼性が高く、かつ、腐食に対する信頼性の高い配線層33を得ることができる。

(もっと読む)

3,441 - 3,450 / 3,539

[ Back to top ]