富士通セミコンダクター株式会社により出願された特許

1,451 - 1,460 / 2,507

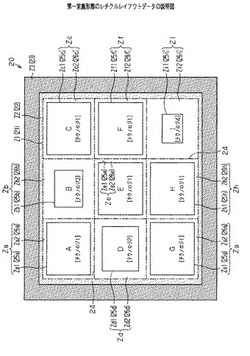

レチクルレイアウトデータ作成方法及びレチクルレイアウトデータ作成装置

【課題】半導体チップに応じて異なるスクライブ幅を備えるレチクルレイアウトデータを作成するレチクルレイアウトデータ作成方法及びレチクルレイアウトデータ作成装置を提供する。

【解決手段】複数種類の半導体チップのレチクルレイアウトデータに対して、実際にダイシングにて必要なスクライブ幅をそれぞれ設定する。設定した実際にダイシングにおいて必要なスクライブ幅の二分の一の幅で、前記複数種類の半導体チップのレチクルレイアウトデータに対して、その外周に配置されるチップスクライブ領域をそれぞれ作成する。

(もっと読む)

電子デバイスの製造方法及び設定装置

【課題】電子デバイスの更なる微細化及び高集積化が進んでも、リソグラフィー及びエッチングにより被加工対象の極めて高い寸法精度を達成し、信頼性の高い電子デバイスを実現する。

【解決手段】被加工対象上に形成されたレジスト膜を加工してレジストパターンを形成する工程と、レジストパターンをマスクとして、所定のエッチング条件で被加工対象をエッチングする工程とを実行する際に、形成されたレジストパターンの寸法及び形状(膜厚及びテーパ角度)を測定し、測定されたレジストパターンの寸法及び形状に基づいて前記エッチング条件を調整する。

(もっと読む)

絶縁ゲート型半導体装置及びその製造方法

【課題】 絶縁ゲート型半導体装置及びその製造方法に関し、炭化タンタル膜の仕事関数を適正に選択的に制御する。

【解決手段】 半導体基板上にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜上に炭化タンタル膜を成膜する工程と、前記炭化タンタル膜の一部を露出する開口を有するマスクパターンを形成したのち、水素プラズマ処理を行う工程とを設ける。

(もっと読む)

可変遅延回路

【課題】 本発明は、所定の遅延時間を設定可能な可変遅延回路を提供することを目的とする。

【解決手段】 可変遅延回路は、第1遅延回路6、第2遅延回路7、検出回路8、および選択回路9を備えている。第1遅延回路6は、複数の第1遅延段6aを縦続接続して構成されており、入力信号を初段で受けている。第2遅延回路7は、第1遅延段6aと同一の複数の第2遅延段7aを縦続接続して構成されており、第1タイミング信号を初段で受けている。検出回路8は、第2タイミング信号を受け、各第2遅延段7aから出力される遅延タイミング信号のうち、第2タイミング信号の遷移エッジに隣接する遷移エッジを有する遅延タイミング信号を求める。選択回路9は、検出回路8が求めた遅延タイミング信号を出力する第2遅延段に対応する第1遅延段から出力される遅延信号を選択する。

(もっと読む)

設計支援方法

【課題】半導体集積回路の集積度の向上を図ること。

【解決手段】設計支援装置800は、レイアウトデータに含まれる配線の中から、対象配線と隣接配線の組み合わせを配線検出部801により検出し、対象配線上の対象ビアと、隣接配線上の近傍ビアとの組み合わせをビア検出部802により検出する。つぎに、検出した対象ビアと近傍ビアとのビア間距離を算出部803により算出し、置換部804により対象ビアと近傍ビアの少なくともいずれか一方のビアの形状を、当該ビアの露光パターンの形状に置換する。そして、置換した近傍ビアの位置が算出したビア間距離となる位置を探索部805により探索し、変換部806により、探索した位置に近傍ビアの位置を変換し、レイアウトデータを保持するデータベースに保存する。そして、保存されたデータを出力部807により出力する。

(もっと読む)

モーションベクトルおよび画像の境界強度を取得する方法およびシステム

【課題】画像のモーションベクトル及び境界強度を取得する方法およびシステムの提供。

【解決手段】画像のモーションベクトルおよび境界強度を取得する方法であって、デコードするブロックおよびマクロブロック/副マクロブロックのタイプに従ってモーションベクトル予測方向情報およびモーションベクトル演算方法情報を決定しS202、モーションベクトル演算方法情報に従って、モーションベクトル予測方向情報を使用してブロックのモーションベクトルを演算するのに必要な関連情報を取得しS204、そして取得した関連情報を使用してブロックのモーションベクトルを演算し、そしてブロックおよび周囲ブロックのモーションベクトルを使用してブロックの境界強度を演算するS206。

(もっと読む)

制御回路

【課題】シンセサイザの起こり得る温度ドリフトを、連続運転間に補正する制御回路を提供する。

【解決手段】出力信号及び第1の参照信号の間の関係を示す第1の制御信号を生成し及び第1の制御信号に依存する出力信号を生成するために動作可能であり、且つ、第1の制御信号に応じて、出力信号及び第1の参照信号に間の第1の所望の関係を維持しやすいように構成される第1の制御手段と、第1の制御信号と第2の参照信号との間の第2の所望の関係を維持しやすいように、第2の制御信号を経て第1の制御信号に応じて、第1の制御手段の動作に影響を与えるように構成される第2の制御手段と、を有する制御回路。

(もっと読む)

半導体装置およびその製造方法

【課題】素子分離領域を挟んで隣接する素子領域間におけるリーク電流の発生を抑制する素子分離構造の提供。

【解決手段】半導体基板41上に形成され、シャロートレンチアイソレーション構造を有する素子分離領域41Iと、素子分離領域41Iを挟んで形成され、第1の導電型を有する第1および第2の不純物拡散領域41N1,41N2と、素子分離領域41Iの下に形成された、第2の導電型を有する第3の不純物拡散領域41PWと、素子分離領域41Iの下で、第3の不純物拡散領域41PWの深さよりもさらに深く形成され、前記第2の導電型の第3の不純物元素を含む第4の不純物拡散領域41DPWと、第1および第2の不純物拡散領域41N1,41N2中、第4の不純物拡散領域DPWの深さよりも浅く形成され、前記第1の不純物元素に加え前記第3の不純物元素を含む第1および第2の不純物拡散領域部分41n1,41n2とで構成する。

(もっと読む)

メモリアクセス制御回路及び画像処理装置

【課題】効率的なメモリアクセス動作を実現できるメモリアクセス制御回路を提供する。

【解決手段】メモリアクセス制御回路は、レジスタを第1の状態に設定して第1の一連のアドレスを送信し、レジスタを第2の状態に設定して第2の一連のアドレスを送信するアドレス送信部と、レジスタを第3の状態に設定して第1の一連のデータを受信して遅延させることなくデータ処理し、レジスタを第4の状態に設定して第2の一連のデータを受信して所定の遅延時間だけ遅延させてからデータ処理するデータ受信部と、アドレス送信部からの第1の一連のアドレスの送信終了に応答してレジスタの状態をバックアップ部に退避させるとともに第2の状態をレジスタに復帰させ、データ受信部による第1の一連のデータのデータ処理終了に応答して、前記所定の遅延時間を利用してレジスタの状態をバックアップ部に退避させるとともに第4の状態をレジスタに復帰させることを特徴とする。

(もっと読む)

レイアウト設計方法および半導体集積回路

【課題】パッド律則とコア律則を意識しないレイアウト設計を容易に実現し、半導体集積回路の面積の縮小化とコストの低減化を図ること。

【解決手段】レイアウト設計装置300は、設計対象回路の回路情報の入力を入力部301により受け付け、入力された回路情報に含まれているコアの領域が確保された設計対象回路のレイアウト情報を生成部302が生成する。生成されたレイアウト情報上のコアの領域以外の領域に、回路情報に含まれているI/O回路をレイアウト部303により配置および配線する。回路情報に含まれているパッドの配置可能領域を決定部308により作成したレイアウト情報上に決定する。必要配置数分のパッドの総面積が配置可能領域の面積を超えない最大の大きさに、パッドの面積を最適化部309により最適化する。最適化されたパッドを配置部310により配置可能領域に配置する。

(もっと読む)

1,451 - 1,460 / 2,507

[ Back to top ]