富士通セミコンダクター株式会社により出願された特許

911 - 920 / 2,507

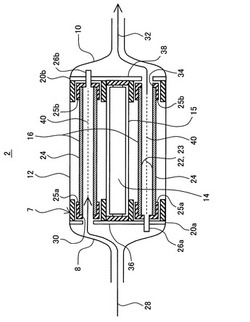

有機ガス処理装置

【課題】小型で且つ運転が容易な有機ガス処理装置を提供すること。

【解決手段】紫外線を発生し、前記紫外線により光触媒に有機ガスを分解させる紫外線光源と、内壁が前記光触媒の皮膜で覆われ且つ前記紫外線を透す筒状体であって、前記紫外線光源を囲うように前記紫外線光源の長手方向に沿って配置され、且つ前記長手方向に延在する軸を中心に自転する複数の有機ガス光分解部と、複数の前記有機ガス光分解部を直列に連結して、前記有機ガス光分解部の連結構造体を形成する複数の連結管と、前記連結構造体の一端に設けられ、前記有機ガスを含むガスが流入する第1の開口部と、前記連結構造体の他端に設けられ、前記ガスが流出する第2の開口部とを有すること。

(もっと読む)

半導体装置の製造方法

【課題】 バッチ式イオン注入処理において、イオンビームのビーム電流に周期変動が存在する場合にもドーズ量の均一性を向上させ、それを用いて製造される半導体装置の特性を均一化する。

【解決手段】 複数のウェーハを装填したウェーハディスクを回転させながら、該複数のウェーハにイオンビームを照射するイオン注入工程において、イオンビームのビーム電流が測定され、ビーム電流に周期変動が存在するかが判定される。周期変動が存在すると判定されたとき、ウェーハディスクの回転速度が、ビーム電流の周期変動と同期しない回転数に更新される。

(もっと読む)

設計方法

【課題】設計期間の短縮を図る。

【解決手段】設計装置11は、セルのレイアウト設計処理において、半導体装置のデザインに応じて、セルに含まれる端子に接続する信号配線を形成するための信号アクセストラック数を定量化した信号アクセス率を算出し、信号アクセス率に従って対応する端子のパターンを変更する。該信号アクセス率算出は、半導体装置の層数とロウ使用率に応じて設定された目標端子アクセス指数を記憶する記憶手段から、半導体装置に応じた目標端子アクセス指数を読み出し、前記セルの初期レイアウトデータを生成し、前記セルに含まれる端子を順次選択して着目端子とし、前記着目端子以外の端子のレイアウトをサイジングし、サイジングしたレイアウトの影響を受けない配線トラックを前記着目端子の信号アクセストラックとして抽出し、抽出した前記信号アクセストラックの数と前記目標端子アクセス指数とに基づいて、行う。

(もっと読む)

オン時間固定方式DC−DCコンバータ

【課題】スイッチング周波数のスペクトラム拡散を可能とするオン時間固定方式DC−DCコンバータを提供すること。

【解決手段】オン時間を、設定時間を平均値としてスイッチング周期に応じて可変に制御するオン時間計時回路を備えることで、オン時間の平均値を設定時間に維持しながら個々のスイッチング周期におけるオン時間を可変することにより、スイッチング周波数のスペクトラム拡散を可能とするオン時間固定方式DC−DCコンバータを提供することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】ソース・ドレイン領域の大きさの違いに起因する特性のばらつきを抑制できる半導体装置及びその製造方法を提供することを目的とする。

【解決手段】ソース・ドレイン領域が小さいトランジスタAのゲート電極29aの両側には例えば幅が38nmのサイドウォール32aを配置する。また、ソース・ドレイン領域が大きいトランジスタBのゲート電極29bの両側には、サイドウォール32aと同じ幅のサイドウォール32bに加えて、例えば幅が5nmのサイドウォール33bを配置する。これにより、熱処理する際にソース・ドレイン領域の大きさの違いによるゲート電極の下方への過剰な不純物の拡散が回避でき、所定の特性を得ることができる。

(もっと読む)

半導体装置

【課題】内部回路の再構成を行うためのヒューズ回路を有する半導体装置に関し、ヒューズ材の飛散よるヒューズ回路の誤動作を防止しうる半導体装置を提供する。

【解決手段】第1電源電圧線と第2電源電圧線との間に並列して接続され、ヒューズ10と、ヒューズ10の一方の端子に直列に接続され、ヒューズ10の導通状態に応じた電圧を出力するラッチ回路32とをそれぞれ有する複数のヒューズ回路を有し、複数のヒューズ回路は、ヒューズ10が千鳥状に配列されるように配置されており、隣り合うヒューズ10の第2電源電圧線側の端子と第1電源電圧線側の端子とが反対向きになるように配置されている。

(もっと読む)

研磨パッド、研磨装置及び研磨方法

【課題】 研磨を繰り返すと、研磨定盤と研磨パッドとの間に、気泡が発生し、研磨パッドが盛り上がる。

【解決手段】 研磨層の上面が研磨対象物に接触する。研磨層の背面に、軟質層が接着されている。軟質層の、研磨層に接着された上面とは反対側の背面が、自転する研磨定盤に接着される。軟質層は、研磨層よりも軟質で、連続気泡構造を有する。軟質層の背面に、研磨定盤の自転中心を中心とした円周上の複数の点の各々から、軟質層の外周に向かって、切り込みが形成されている。

(もっと読む)

半導体装置

【課題】 半導体装置に関し、ソース・ドレイン領域を実効的に埋込Si混晶層で構成する際の電気的特性を向上する

【解決手段】 一導電型シリコン基体と、一導電型シリコン基体上に設けたゲート絶縁膜と、ゲート絶縁膜の上に設けたゲート電極とゲート電極の両側の一導電型シリコン基体に設けた逆導電型エクステンション領域と、逆導電型エクステンション領域に接するとともに、一導電型シリコン基体に形成された凹部に埋め込まれた逆導電型Si混晶層とを備えた半導体装置であって、逆導電型Si混晶層が、第1不純物濃度Si混晶層/第2不純物濃度Si混晶層/第3不純物濃度Si混晶層を有し、第2不純物濃度を第1不純物濃度及び第3不純物濃度よりも高くする。

(もっと読む)

半導体装置の製造方法

【課題】ロジック回路とメモリ回路を混載した半導体装置において、ロジック回路部に形成されるレジストパターン形状の精度低下抑制に寄与する半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、ロジックトランジスタ、不揮発性メモリをそれぞれ形成する第1及び第2の活性領域を画定する素子分離絶縁膜を、STIで形成する工程と、第2の活性領域上方に、フローティングゲートとなる導電層を形成する工程と、導電層上及びその外側の領域を覆って、窒化シリコンを含む絶縁膜を形成する工程と、第1の活性領域の隣接部分の素子分離絶縁膜上の窒化シリコンを含む絶縁膜を覆い、第1の活性領域を露出するマスクを用いてエッチングする工程と、第1の活性領域の隣接部分の素子分離絶縁膜上の窒化シリコンを含む絶縁膜上に端部の配置されたフォトレジストパターンを形成する工程とを有する。

(もっと読む)

半導体試験回路、半導体試験用冶具、半導体試験装置及び半導体試験方法

【課題】多くのDUTを同時に試験可能な半導体試験回路を提供する。

【解決手段】信号処理部12が、テスタ20から信号線SLを介して入力された試験信号を複数のDUT30−1〜30−nに分配して供給するとともに、試験信号に基づいた複数のDUT30−1〜30−nからの応答信号を合成した試験結果を生成し、試験結果出力部13が、その試験結果を、入力された試験信号とは異なる電圧レベルにして、信号線SLを介してテスタ20に出力する。

(もっと読む)

911 - 920 / 2,507

[ Back to top ]