富士通セミコンダクター株式会社により出願された特許

931 - 940 / 2,507

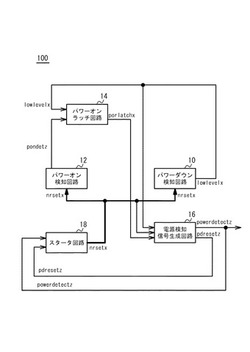

電源検出回路

【課題】 電源検出回路の誤動作を抑制すること

【解決手段】 パワーダウン検出回路10及びパワーオン検出回路12を初期化するための初期化信号nrsetxを生成するスタータ回路18において、パワーオンが検出されている第1期間に電源電圧を中間ノードへ供給する切替回路を有する。第1の期間において第1電源電圧から中間ノードへ電源電圧を供給することにより、スタータ回路の出力を安定させることができる。その結果、電源検出回路の誤動作を抑制することができる。

(もっと読む)

多層配線基板及びその製造方法

【課題】 機械的な切断時の樹脂の剥離や損傷を軽減もしくは回避することにより、信頼性が高く、かつ電気的特性に優れた多層配線基板の構造及びその製造方法を提供する。

【解決手段】 複数の樹脂層と複数の配線層が積層形成され、コア基板を有しない配線基板を複数個配設した多層配線基板であって、多層配線基板を切断して各配線基板に個片化するために、各配線基板が単一の樹脂層により連続して配設される。

(もっと読む)

半導体装置の設計方法及び半導体装置の製造方法

【課題】溝内に配線を埋め込む際に層間絶縁膜の表面に深い凹部が生じるのを防止し得る半導体装置の設計方法等を提供する。

【解決手段】単位面積当たりの配線パターンの周囲長の総和を各々の単位領域毎に算出するステップS6と、単位領域内における配線パターンの周囲長の総和が第1の値以上である第1の領域と第2の値以下である第2の領域とを抽出するステップS7,S8と、第1の領域に隣接する第3の領域内に単位面積当たりの周囲長の総和が第3の値である第1のダミーパターンを配置し、第2の領域に隣接する第4の領域内に単位面積当たりの周囲長の総和が第4の値である第2のダミーパターンを配置するステップS9,S10と、第3の領域と第4の領域との間の第5の領域内に単位面積当たりの周囲長の総和が第3の値より小さく、第4の値より大きい第5の値である第3のダミーパターンを配置するステップS11とを有している。

(もっと読む)

半導体装置の製造方法

【課題】チップの搭載を短時間で確実に実施できるようにする。

【解決手段】基板10上にBステージ化したフィルム接着剤21を設け、フィルム接着剤21を介してチップ1を基板10に仮固定する。さらに、チップ1上に封止フィルム41を供給してから、プレスヘッド43で押圧する。プレスヘッド43の温度を調整して、最初に封止フィルム41のみを軟化させてチップ1間の空間40に封止フィルム41の材料を充填させる。次に、プレスヘッド43の温度を上昇させ、フィルム接着剤21を軟化させてバンプ2と電極パッド13Aを接続させる。この後、プレスヘッド43の温度をさらに上昇させてフィルム接着剤21及び封止フィルム41をCステージ化する。

(もっと読む)

送信回路

【課題】

直交変調回路のキャリアリークを抑制する。

【解決手段】

送信回路は,第1のベースバンド信号と発振信号とのいずれか一方を選択する第1のスイッチと,第2のベースバンド信号と発振信号とのいずれか一方を選択する第2のスイッチと,第1のスイッチが選択した信号と発振信号に基づく第1のローカル周波数信号とを乗算する第1の乗算器と,第2のスイッチが選択した信号と発振信号に基づく第2のローカル周波数信号とを乗算する第2の乗算器と,第1,第2の乗算器の出力を加算する加算器と,第1,第2のスイッチが発振信号を選択した場合に,加算器の出力のレベルに応じて第1,第2のベースバンド信号をそれぞれ補正する補正部とを有する。

(もっと読む)

半導体装置

【課題】 入出力部の電源配線の近傍にバイパスコンデンサを配置する場合、LSIの端子数が多くなると、バイパスコンデンサを配置するための領域を確保することが困難になる。

【解決手段】 半導体基板の表面に、電子回路素子が形成されている電子回路領域が画定される。半導体基板の上に、一方に基準電位が印加され、他方に電源電圧が印加される第1及び第2の配線が配置される。シールリングが、電子回路領域を取り囲むように、半導体基板の上に配置される。シールリングは、第1の配線に電気的に接続される。第1の不純物拡散領域が、シールリングよりも内側において、半導体基板の表層部に形成される。第1の不純物拡散領域の上に誘電体膜が配置される。誘電体膜の上に、シールリングに電気的に接続され、導電材料で形成されたキャパシタ導電膜が配置される。

(もっと読む)

半導体装置及びその製造方法

【課題】 半田ボール等の外部接続端子の位置精度を高めるとともに、外部接続端子と電極パッドとの間の接続信頼性を高める。

【解決手段】 半導体装置100は、基板111と、基板111上に形成された電極パッド113及び絶縁層115と、電極パッド113に電気的に接続された半田ボール141とを含む。絶縁層115は、電極パッド113上に開口部115aを有する。半導体装置100は更に、絶縁層115の開口部115a内で電極パッド113に接合され、半田ボール141を受ける金属膜161を含む。金属膜161は、電極パッド113に接する底部161aと、当該金属膜の外周部が底部161aの縁部から突出した突出部161bとからなるカップ形状を有する。

(もっと読む)

半導体メモリおよび半導体メモリの冗長方法

【課題】 チップサイズを増やすことなく、欠陥箇所の試験および欠陥箇所を置き換える場所の試験を行う。

【解決手段】 半導体メモリは、第1データ変換部、バッファメモリ、メインメモリおよび第2データ変換部を有している。第1データ変換部は、第1データを第2データに変換するための第1テーブルを含む。バッファメモリは、第2データを一時的に格納する。メインメモリは、バッファメモリに格納された第2データを格納する。第2データ変換部は、メインメモリから読み出される第2データを第1データに変換するための第2テーブルを含む。さらに、バッファメモリは、メインメモリの欠陥アドレスを格納し、第1データ変換部は、欠陥アドレスに対応する第1テーブルのアドレスに欠陥情報を格納する。

(もっと読む)

プローバー装置及び検査方法

【課題】半導体回路に影響を与えることなく確実に電極パッドとの電気的接続を得ることのできるプローバー装置を得る。

【解決手段】1又は複数のプローブ針を有するプローブカードと、前記プローブ針を振動させるための振動子と、を有し、前記プローブ針は屈曲部を有しており、前記プローブ針には、前記屈曲部から前記先端までの先端部を振動させる固有振動数が与えられるものであることを特徴とするプローバー装置により上記課題を解決する。

(もっと読む)

直交変復調回路

【課題】

移相器が生成するローカル周波数信号に位相ずれが生じても復調信号や変調信号に位相誤差が生じない直交変復調回路を提供する。

【解決手段】

直交復調回路は,変調信号が入力される第1〜第4の乗算器と,第1,第3の乗算器に第1のローカル周波数信号を供給し,第1のローカル周波数信号に対して所定の位相差を有する第2のローカル周波数信号を第2の乗算器に,それと逆相の第3のローカル周波数信号を第4の乗算器に供給する移相器と,第1,第2の乗算器の出力信号を加算して第1の復調信号を出力する第1の加算器と,第3,第4の乗算器の出力信号を加算して第2の復調信号を出力する第2の加算器とを有する。

(もっと読む)

931 - 940 / 2,507

[ Back to top ]