エルピーダメモリ株式会社により出願された特許

91 - 100 / 2,599

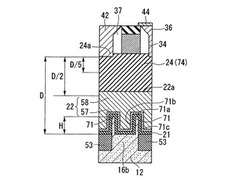

半導体装置およびその製造方法

【課題】電流―電圧特性の向上およびオン電流を増大することが可能で、高速動作に優れた半導体装置及びその製造方法を提供する。

【解決手段】半導体基板12の主面に形成され、第1の方向に延在する複数の活性領域と、活性領域を区画する素子分離領域と、半導体基板12の主面に形成されたものであって、平面視して複数の活性領域に交差する方向に延在する複数のゲート溝と、ゲート溝のそれぞれに埋め込まれた複数のゲート電極22と、を備えた半導体装置であって、ゲート溝のそれぞれの底面には、第1の方向に延在すると共に、上面71aが半導体基板12の主面よりも低い位置に配置する一対の突起部71が形成されており、ゲート電極22は、ゲート絶縁膜21を介して突起部71の上面71aと内側面71bと外側面71cとを覆ってなる、ことを特徴とする。

(もっと読む)

半導体装置

【課題】相補の信号によりプルアップバッファ回路とプルダウンバッファ回路を制御し、レベルシフタ関連回路をコンパクトに構成する。

【解決手段】半導体装置10は、プルアップバッファ回路100とプルダウンバッファ回路200を排他的にオン・オフ制御することによりデータ端子DQからデータを出力する。シリアライザ300は、相補な内部データ信号DT1/DC1を出力する。レベルシフタ370は、内部データ信号DT1/DC1の電圧レベルを変換し、相補な内部データ信号DT2/DC2を同時生成する。プルアップバッファ回路100とプルダウンバッファ回路200は、この変換後の内部データ信号DT2/DC2により制御される。

(もっと読む)

半導体装置

【課題】1つのコントローラに共通接続された複数の半導体装置のモードレジスタに個々の設定値を書き込む。

【解決手段】例えば、モードレジスタ設定信号MRS1を活性化させるコマンドデコーダ82と、モードレジスタ設定信号MRS1を遅延させることによってモードレジスタ設定信号MRS2を生成するレイテンシシフタ83と、データ信号D0がローレベルである場合にはモードレジスタ設定信号MRS2に基づいてモードレジスタ設定信号MRS3を活性化させ、データ信号D0がハイレベルである場合にはモードレジスタ設定信号MRS3を非活性状態に保持する論理ゲート回路G2,G3と、モードレジスタ設定信号MRS3の活性化に応答してモード信号が設定されるモードレジスタ84を備える。これにより、1つのコントローラに共通接続された複数の半導体装置のモードレジスタに個々の設定値を書き込める。

(もっと読む)

半導体装置

【課題】CRC機能を有し、ライト動作とリード動作を高速に行うことができる半導体装置を提供する。

【解決手段】メモリセルアレイ(メモリセルアレイ11)と、巡回冗長論理符号を生成する誤り検出符号生成回路(誤り検出符号生成回路20)と、メモリセルアレイから読み出されたデータに巡回冗長論理符号を付加してデータ入出力端子を介して半導体装置の外部へリードデータとして出力し、或いは半導体装置の外部からライトデータが入力されて、前記メモリセルアレイへ書き込むデータを誤り検出符号生成回路に出力するデータ入出力部(データ入出力部19)と、メモリセルアレイとデータ入出力部との間に配置されるバス配線(リードライトバス)と、誤り検出符号生成回路とデータ入出力部との間に配置される巡回冗長論理符号配線(CRC信号線)と、を備える。

(もっと読む)

半導体装置

【課題】調整コードの変化に伴うジッタの発生が低減されたDLL回路を提供する。

【解決手段】内部クロック信号ECLKを受けるインバータ回路210〜217と、内部クロック信号OCLKを受けるインバータ回路220〜227とを有し、調整コードC0〜C7を受けて選択されたインバータ回路の出力を合成することによって、内部クロック信号LCLKの位相を16段階に調整する。インバータ回路210,220は内部クロック信号LCLKの位相を1段階変化させる能力を有し、インバータ回路211〜217,221〜227は内部クロック信号LCLKの位相を2段階変化させる能力を有する。このように、内部クロック信号LCLKの位相を調整するインバータ回路の最大能力が抑制されていることから、調整コードの変化に伴うジッタの発生が低減される。

(もっと読む)

半導体装置

【課題】直前の書き込みデータと同じ書き込みデータを連続して書き込む場合であれば、入出力線対のイコライズは不要である。そのため、直前の書き込みデータと同じ書き込みデータを連続して書き込む場合に、入出力線のイコライズを実施せず、データ書き込み時の消費電力を削減する半導体装置が、望まれる。

【解決手段】半導体装置は、第1の信号入出力線をイコライズする第1のイコライズ回路と、データのライト動作が連続する場合には、連続するライト動作間、第1のイコライズ回路を非活性とし、リード動作が連続する場合又はライト動作の後にリード動作を行う場合には、連続するライト動作間又はライト動作の後のリード動作間時に、第1のイコライズ回路を活性とする制御回路と、を備えている。

(もっと読む)

半導体装置

【課題】貫通電極を有する半導体チップを積層して貫通電極同士を相互に接続する際、貫通電極の接続端子となるバンプ表面の金属接合層のうち、加熱により流動する層、例えば半田層が押しつぶされて薄膜化すると接合強度が低下する場合がある。

【解決手段】半導体基板の両主面に通常のバンプ構造(第1及び第2主バンプ51,69)と共に第1及び第2副バンプ50,68を設け、第1及び第2副バンプの少なくとも一方を第1及び第2主バンプよりも高くして、半導体チップの接合時に副バンプ同士が主バンプ同士より先に接触させることで、主バンプ同士の接合マージンを確保して、半田層49などの加熱により流動する層の主バンプでの薄膜化を抑制する。

(もっと読む)

半導体装置

【課題】パリティエラーが発生した場合に適切な処理を実行する。

【解決手段】例えば、アドレス信号ADD及びコマンド信号CMDに基づいてメモリセルアレイ11を活性化させるアクティブ制御回路230と、外部から供給される検証信号PRTYに基づいてアドレス信号ADD及びコマンド信号CMDを検証することによりパリティエラー信号PERRを生成する検証回路90と、パリティエラー信号PERRがフェイルを示した場合、活性化されているメモリセルアレイ11を所定時間経過後に非活性化させるエラー処理回路120を備える。これにより、パリティエラーが発生した場合であっても、既に発行されたコマンドを正しく実行した後にメモリセルアレイを非活性化させることができる。

(もっと読む)

半導体装置及びその制御方法

【課題】出力バッファ回路のインピーダンスを切り替えるためのタイミングマージンを拡大する。

【解決手段】制御期間T1においてはプルアップバッファ回路100をオン、プルダウンバッファ回路200をオフとし、制御期間T2においてはリードデータDQに基づいてプルアップバッファ回路100及びプルダウンバッファ回路200の一方をオン、他方をオフとする。制御期間T1においてはプルアップバッファ回路100のインピーダンスをインピーダンスコードODTCに基づいて設定し、制御期間T2においてはプルアップバッファ回路100及びプルダウンバッファ回路200の前記一方のインピーダンスをインピーダンスコードRONCに基づいて設定する。制御期間T3中にプルアップバッファ回路100のインピーダンスをコードODTCに基づく値からコードRONCに基づく値に変化させる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板に形成されたプレーナ型トランジスタと3次元トランジスタを含む半導体装置の形成プロセスを簡略化できるようにする。

【解決手段】半導体基板に形成されたプレーナ型トランジスタと3次元トランジスタを含む半導体装置であり、前記プレーナ型トランジスタ、前記3次元トランジスタはともに高誘電率材料によるゲート絶縁膜を有し、前記プレーナ型トランジスタは、前記ゲート絶縁膜上に、下側が第1のメタル材料(A)、上側が第2のメタル材料(B)からなるゲート電極を有し、前記3次元トランジスタは埋め込みゲート電極を有し、該埋め込みゲート電極の下側のほうに前記第1のメタル材料(A)と同一の材料が、該埋め込みゲート電極の上側のほうに前記第2のメタル材料(B)と同一の材料がそれぞれ使用されている。

(もっと読む)

91 - 100 / 2,599

[ Back to top ]