エルピーダメモリ株式会社により出願された特許

131 - 140 / 2,599

半導体装置及びその製造方法

【課題】通電領域表面の周辺の強電界の影響がナノワイヤに及び難くして、ホットキャリアの生成やオフリーク電流を低減する。半導体装置を高性能化する。

【解決手段】基板の表面よりも深い位置に配置され互いに対向する2つの側壁を有する導電膜と、導電膜の2つの側壁の側方に形成され互いに同じ導電型の半導体領域である第1及び第2の通電領域と、導電膜を貫通して2つの半導体領域どうしを接続し第1及び第2の通電領域の導電型とは逆導電型の半導体領域であるナノワイヤと、導電膜と前記ナノワイヤとの境界部に形成された絶縁膜と、を有することを特徴とする半導体装置。

(もっと読む)

半導体装置及びその配線部品

【課題】半導体装置において、実装密度向上とノイズ低減とを両立することができる技術を提供する。

【解決手段】プリント配線基板101上に実装されたLSI102は、プリント配線基板101から電源供給を受けるためのグランド用BGAボール105bと電源用BGAボール105aとを有し、グランド用BGAボール105bと電源用BGAボール105aは隣接している。プリント配線基板101にはデカップリングコンデンサ103が実装され、デカップリングコンデンサ103は端子113と端子114とを有している。グランド用BGAボール105bと端子113が金属電極平板110で接続され、電源用BGAボール105aと端子114が金属電極平板111で接続され、金属電極平板110と金属電極平板111の間には、厚さ1μm以下の誘電体膜112が挟み込まれている。

(もっと読む)

半導体装置及びその製造方法

【課題】多結晶シリコン膜との接触に起因するショットキー抵抗を低減する。

【解決手段】半導体装置は、トランジスタを備える。トランジスタは、第1の活性領域の表面の一部を覆い二酸化シリコンよりも高い誘電率を有する第1の絶縁材料からなる第1のゲート絶縁膜と、第1のゲート絶縁膜上に形成された第1の金属材料からなる第1の金属ゲート電極と、第1の金属ゲート電極上に形成されたp型導電型の第1の多結晶シリコン膜を有する。

(もっと読む)

半導体装置及びそのテスト方法

【課題】ディスターブ試験時のノイズを低減しサイクル高速化を実現する技術を提供する。

【解決手段】本発明による半導体装置は、ワード線及びビット線に接続された複数のメモリセルを含み、複数のバンクに分割されたメモリセルアレイと、テスト動作時に、テスト回路用アドレス信号とディスターブ試験用テスト信号を用いて、バンク毎にワード線を内部アドレス信号に応じて別々のタイミングで選択するロウ周辺回路とを備える。

(もっと読む)

半導体装置

【課題】適宜繰り返し行われるキャリブレーションに要する時間を短縮する。

【解決手段】半導体装置は、入力コマンドに応じ、出力ドライバーのインピーダンスを調整するキャリブレーションを、設定値を用いて行うキャリブレーション回路と、温度センサーと、前記出力ドライバーの温度特性情報を記憶する記憶回路と、前記温度センサーからの検出信号と前記記憶回路から読み出した前記温度特性情報とに基づいて前記設定値を変更する設定信号を生成し、前記キャリブレーション回路へ出力する設定回路と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】TSV構造を採用し複数のチップをスタックした半導体装置を、改良された入出力形式で提供できるようにする。

【解決手段】複数のチップをスタックしてなり、隣り合うチップ間の接続を、貫通電極を介して行なうTSV構造を持つ半導体装置に適用される。各チップは複数のチャンネルに対応した複数のTSVアレイ部を備え、該複数のTSVアレイ部は、スタックするチップの数に応じて入出力に寄与するTSVアレイ部と入出力回路に接続されないパススルーのTSVアレイ部とに分けられている。スタックするチップの数に応じて2段目以降のチップを面方向に回転させてスタックし、前記パススルーのTSVアレイ部を経由してデータの入出力を行なう構成とすることにより、前記データの入出力に寄与するTSVアレイ部にのみ共有の入出力回路を備える構成とし、入出力回路の数を低減させた。

(もっと読む)

結晶性化合物及びこれを用いた可変抵抗素子並びに電子デバイス

【課題】磁気抵抗効果の大きい新たな可変抵抗素子を提供する。

【解決手段】本発明による可変抵抗素子は、次の3つの特徴を備えた結晶性化合物を含む。第1の特徴は、トポロジカル誘電体特性を示すことにより、伝導帯と価電子帯がディラックコーンを形成する点である。第2の特徴は、ディラックコーンを構成する伝導帯の谷と価電子帯の山との間に、バンドギャップが形成される点である。第3の特徴は、異なるスピンが入る二つのバンドがΓポイントを中心に時間反転対称を持つことである。これら3つの特徴を全て備えることにより、著しい磁気抵抗効果が発現する。

(もっと読む)

半導体装置

【課題】トリミング時間の短縮とヒューズ素子による占有面積の縮小を達成しつつ、高速アクセスを実現する。

【解決手段】不良ワード線のアドレスを記憶するロウヒューズ回路21と、不良ビット線のアドレスを記憶するカラムヒューズ回路22と、ロウアドレスXADD又はロウヒューズ回路21から読み出されたアドレスRXADDに基づいてワード線WL又は冗長ワード線RWLを選択するロウデコーダ11と、カラムアドレスYADD又はカラムヒューズ回路22から読み出されたアドレスRXADDに基づいてビット線BL又は冗長ビット線RBLを選択するカラムデコーダ12とを備える。ロウデコーダ11、ロウヒューズ回路21及びカラムヒューズ回路22はメモリセルアレイ10の長辺10aに沿って配置され、カラムデコーダ12はメモリセルアレイ10の短辺10bに沿って配置される。

(もっと読む)

半導体装置の製造方法

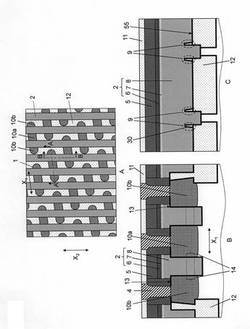

【課題】キャパシタ上の絶縁膜とキャパシタの形成されていない領域上の絶縁膜と平坦化する際に、キャパシタ上の絶縁膜を一部エッチング除去した後平坦化すると、両者の境界部に残る絶縁膜隆起部が剥がれてくぼみ等の欠陥が発生する。

【解決手段】境界部に残す絶縁膜の隆起部立ち上がり点から水平方向の距離をLr、エッチング量をHdとしたとき、アスペクト比Hd/Lrを0.6以下、好ましくは0.25以下とする。通常、Hdはキャパシタの形成されていない領域上の絶縁膜表面高さまでとし、Lrはキャパシタ高さの少なくとも4倍とする。

(もっと読む)

半導体装置の製造方法

【課題】キャパシタ上の絶縁膜とキャパシタの形成されていない領域上の絶縁膜と平坦化する際に、キャパシタ上の絶縁膜を一部エッチング除去した後平坦化すると、両者の境界部に残る絶縁膜隆起部が剥がれてくぼみ等の欠陥が発生するのを抑制する。

【解決手段】境界部に残す絶縁膜の隆起部立ち上がり点から水平方向の最短距離をLr、エッチング量をHdとしたとき、アスペクト比Hd/Lrを0.6以下、好ましくは0.25以下する。キャパシタ上のエッチング開口端形状として鋸刃型などの形状、開口端側面を傾斜形状とする、又はスリットを形成する。

(もっと読む)

131 - 140 / 2,599

[ Back to top ]