エルピーダメモリ株式会社により出願された特許

141 - 150 / 2,599

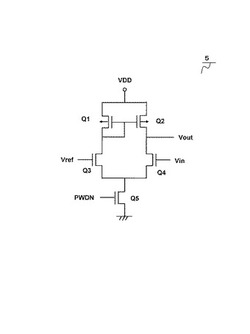

半導体装置

【課題】信号伝送のより高速化を図る。

【解決手段】入力信号Vinと基準信号Vrefとを入力する第1の差動対(Q3、Q4が相当)と、第1の差動対のそれぞれ負荷となる第1及び第2のトランジスタQ2、Q1と、を含む第1の入力回路を備え、第1の入力回路の出力側となる第1のトランジスタQ2は、第2のトランジスタQ1に比べてゲート幅を長くする。

(もっと読む)

半導体ウェハ及びその製造方法

【課題】スクライブ線領域におけるダミーパターンが影響して配線形成の際に露光時のアライメント波形検出精度を低下させるおそれがあった。

【解決手段】複数の素子形成領域と、素子形成領域を相互に区画するスクライブ線領域と、素子形成領域において半導体基板上に配置された複数のパターンと、スクライブ線領域において半導体基板上に配置されるとともに、パターンと同様な構成の複数のダミーパターンと、パターン及びダミーパターンを含む半導体基板上に形成されるとともに、上面が平坦化された層間絶縁膜と、スクライブ線領域における層間絶縁膜に形成されるとともに、ダミーパターンと重ならない領域にて半導体基板に通じないように形成された穴状のアクセサリパターンと、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】ねじれや歪の発生を抑制し、マザーボードへの実装が阻害されることがない半導体装置を提供する。

【解決手段】単一の配線基板10と、配線基板10上に搭載された第1の半導体チップ211と、配線基板10上に第1の半導体チップ211に並列して搭載された第2の半導体チップ220と、第1の半導体チップ211および第2の半導体チップ220を覆う封止体60とを有している。第2の半導体チップ220は、複数の半導体チップ片221、222が高さ方向に積層されて成るチップ積層体である。第1の半導体チップ211の上面と、第2の半導体チップ220の上面とは、配線基板10の表面からの高さが互いに等しい。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、小型化を図ることが可能になると共に、絶縁リングで囲まれた貫通電極を狭ピッチで配置することの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】回路素子層5が形成される表面1a、及び裏面1bを有する半導体基板1と、半導体基板1を貫通し、かつ半導体基板1の表面1a側から半導体基板1の裏面1b側に向かうにつれて幅が広くなる貫通電極7と、貫通電極7を囲むように半導体基板を貫通し、かつ半導体基板1の表面1a側から半導体基板1の裏面1b側に向かうにつれて幅が狭くなる第1の絶縁リング3と、を有し、半導体基板1の厚さ方向Aにおいて、第1の絶縁リング3の少なくとも一部と対向するように貫通電極7を配置する。

(もっと読む)

半導体装置の製造方法

【課題】装置の大型化や材料コストの増加を招くことなく下層チップに接続されるボンディングワイヤと上層チップとの接触を抑制した半導体装置の製造方法を提供する。

【解決手段】第1の半導体チップ13の一方の面にボンディングワイヤ16−2を接続し、第2の半導体チップ15の一方の面に接着部材14を設け、コレットを用いて第2の半導体チップの他方の面を保持し、第2の半導体チップを保持した状態でコレットを冷却し、コレットを冷却した後に、コレットを移動させて、接着部材14を第1の半導体チップ13の一面に密着させ、第1の半導体チップ13と第2の半導体チップ15とを接着部材14を介して接着する。

(もっと読む)

半導体装置とその制御方法

【課題】テスト時に、読み出しビット線に接続するYスイッチと共通のローカル入出力線に接続される被救済ビット線に接続するYスイッチに接続するYS制御信号のオープン不良を検出可能とする半導体装置の提供。

【解決手段】テストモード時に、選択されたYS制御信号(YS8)の非活性からメインアンプを活性化させる制御信号(MAE)の活性化までの時間(t4)を調整し、通常動作時よりも長くすることで、被救済ビット線に接続するYスイッチに接続するYS制御信号(YS0)のオープン不良を検出する。

(もっと読む)

半導体装置およびその製造方法

【課題】同一平面上に形成された2つの配線が互いにショートするのを回避すること。

【解決手段】第1の方向(X)に複数本並べて配置された活性領域(50)の各々は、第1の方向(X)と直交する第2の方向(Y)に離間して配置された2つの縦型トランジスタ(51)と、この2つの縦型トランジスタ(51)の間に位置する縦型のゲート電極用ダミーピラー(1a)と、から成る。半導体装置(100)は、複数本の活性領域(50)の中央に位置するゲート電極用ダミーピラー(1a)へ給電するために第1の方向(X)へ延在して配置されたゲート給電配線(23)と、2つの縦型トランジスタ(51)間を接続するために、第2の方向(Y)に延在し、かつゲート給電配線(23)を迂回するように構成されたトランジスタ間接続配線(21、10A、16)と、を備える。

(もっと読む)

半導体装置

【課題】消費電力の低減と干渉の抑制を実現できる半導体装置を提供する。

【解決手段】半導体装置は、直列に多段接続された第1及び第2のチップと制御チップとを備える。第1及び第2のチップのそれぞれの転送制御部は、識別信号が制御チップから供給されると当該識別信号後段のチップへ伝送し、制御チップが供給するクロック信号のn番目のパルスに基づいて、識別信号が表す識別情報を第2の記憶領域に書き込み、書き込みが終了するまでクロック信号の後段のチップへの伝送を阻止する。制御チップは、コマンドによって第1及び第2のチップを排他的にアクセスし、第1及び第2のチップのスイッチ制御回路は、コマンド及び識別情報に応じてそれぞれ対応する第1のスイッチ回路を互いに排他的に制御する。

(もっと読む)

半導体装置

【課題】アナログ電圧を使用することなく、クロック信号を高精度且つ広範囲に遅延させる。

【解決手段】入力ノード110aと出力ノード110bとの間に直列接続された複数のワンショットパルス生成回路201〜20nを備える。ワンショットパルス生成回路201〜20nのそれぞれは、入力されたクロック信号の一方のエッジに応答して、ワンショットパルスを生成する。ワンショットパルスのパルス幅は、カウント値RCNTに基づいて可変である。これにより、カウント値RCNTを変化させることによって、ディレイライン110の遅延量を広範囲且つ高精度に変化させることが可能となる。しかも、アナログ電圧を使用しないことから、アナログ電圧の生成回路やその安定化回路などを設ける必要もなくなり、回路設計が容易となる。

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタ間接続配線が吊りワード線と短絡してしまうのを回避すること。

【解決手段】第1の方向(X)に複数本並べて配置された活性領域(50)の各々は、第1の方向(X)と直交する第2の方向(Y)に離間して配置された2つの縦型トランジスタ(51)と、この2つの縦型トランジスタ(51)の間に位置するピラー(1a)と、から成る。半導体装置(100)は、複数本の活性領域(50)の中央の位置で、第1の方向(X)へ延在して配置された吊りワード線(23)と、2つの縦型トランジスタ(51)間を接続するために、第2の方向(Y)に延在し、かつ吊りワード線(23)を迂回するように構成されたトランジスタ間接続配線(21、10A、16)と、を備える。

(もっと読む)

141 - 150 / 2,599

[ Back to top ]