エルピーダメモリ株式会社により出願された特許

181 - 190 / 2,599

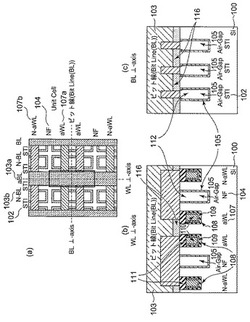

半導体装置及びその製造方法

【課題】 対象セルのワード線に隣接するワード線の電位の影響に伴う対象セルのビット線への電界を緩和する。

【解決手段】 半導体基板100に形成され、半導体素子101を形成するための活性領域と、半導体基板100内に形成され、活性領域を分離するための素子分離領域(STI102、NF104)と、素子分離領域(STI102、NF104)内に設けられた空洞部105を有する半導体装置。

(もっと読む)

電子顕微鏡システム及びその制御方法

【課題】試料の鮮明な画像を撮影することができる電子顕微鏡システム及びその制御方法を提供すること。

【解決手段】電子顕微鏡システムは、電子線を発生させる電子銃と、電子線を試料に照射するための光学系と、当該試料をセットするステージと、当該試料を観察するために、当該試料への電子線の照射を基に試料を撮影する撮影機構と、撮影機構が撮影した当該試料の画像を解析する解析機構と、当該試料と撮影機構との相対的位置を調節する位置調節機構と、を備える。位置調節機構は、解析機構の解析結果を基に、ステージ又は撮影機構の視野のうちの少なくとも一方を移動させる。

(もっと読む)

半導体装置

【課題】消費電流を削減する。

【解決手段】第1及び第2の入力端子に現れる電位差を第1及び第2の電源に基づいて増幅する差動アンプ(図2のMN1、MN2が相当)と、差動アンプを動作させるバイアス電流を制御するバイアストランジスタ(図2のMN3が相当)と、差動アンプの負荷となるカレントミラー回路(図2のMP1、MP2が相当)と、カレントミラー回路のダイオード接続側と其々の制御端が接続されると共に第1及び第2の電源間に直列に接続される、バイアストランジスタと逆導電型の第1及び第2のトランジスタ(図2のMP4、MP6が相当)を有し、第1及び第2のトランジスタの間の接続ノードをバイアストランジスタの制御端に接続するバイアス制御回路と、を備える。

(もっと読む)

ヒューズ回路及びトリミング良否判定方法

【課題】ヒューズ開口部の端部に必ず切断すべきヒューズを配設することにより、レーザー照射後のその切断/未切断をもって、端部のポリイミド膜の膜厚の良否を容易に判定する。

【解決手段】ヒューズ回路は、ヒューズ開口部FAの、ポリイミド膜の厚さが不本意に厚く残りやすい端部に配設された2つの切断確認用ヒューズ1a,1bと、ポリイミド膜の厚さ変動が端部に比べ少ない領域RAに配設された複数の実使用ヒューズ7a〜7dと、2つの切断確認用ヒューズ1a,1bからの信号を入力して当該ヒューズ1a,1bが確実に切断されているかを判定するヒューズ未切断判定回路2と、を備えている。なお、ヒューズ未切断判定回路2は、更にテストモード信号を入力すると共に、出力回路(例えばDQ回路)に判定結果を出力している。

(もっと読む)

半導体装置

【課題】出力回路のインピーダンス調整の精度を向上する半導体装置を提供する。

【解決手段】各々が調整可能なインピーダンスを備える複数の単位バッファを含む出力回路(出力バッファ101)と、複数の単位バッファ回路のうちの1または複数個の単位バッファ回路を選択的に活性化する制御回路(出力制御回路150)と、複数の単位バッファのそれぞれのインピーダンスを調整するインピーダンス調整部であって、当該インピーダンス調整部は、制御回路によって選択的に活性化された1又は複数個の単位バッファ回路の個数が変化することに応じて複数の単位バッファのそれぞれのインピーダンスを調整する、インピーダンス調整部(インピーダンス調整部30)と、を備える。

(もっと読む)

半導体装置及びその制御方法

【課題】クロック信号にジッタ成分が重畳している場合であってもDLL回路を正しくロックさせる。

【解決手段】カウンタ部102のカウント値に応じてクロック信号LCLKを生成するディレイライン101と、クロック信号LCLKを反転させるか否かを制御する反転制御部103とを備える。カウンタ部102のカウント値を第1の初期値にリセットした後、反転制御部103はクロック信号LCLKを反転させ又は反転させることなく出力する。次に、カウンタ部102のカウント値を第2の初期値にリセットする。本発明によれば、ジッタなどの影響によってクロック信号LCLKを誤って反転させ、或いは誤って反転させなかった場合であっても、ダウンカウント(またはアップカウント)が多数回連続することがなくなる。これにより、第1及び第2の初期値としてオフセットした値を用いることが可能となる。

(もっと読む)

半導体装置の製造方法

【課題】チップ積層体の外部接続用電極として機能する第1のバンプ電極間がショートしないように、第1のバンプ電極に精度よくはんだを形成可能な半導体装置の製造方法を提供する。

【解決手段】ボンディングツール34によりはんだ搭載用基板50の他面を保持すると共に、第2のバンプ電極55に形成されたはんだ57を加熱により溶融させ、はんだ搭載用基板の第2のバンプ電極をチップ積層体40の第1のバンプ電極17と対向配置させる工程と、第2のバンプ電極に形成され、かつ溶融したはんだを、チップ積層体の第1のバンプ電極に接触させた後、チップ積層体からはんだ搭載用基板を離間させることで、第1のバンプ電極にはんだを転写させる工程と、を含む。

(もっと読む)

半導体記憶装置

【課題】メモリセルアレイと入出力バッファ間の遅延の最大値を抑制し高速に入出力動作が行える半導体記憶装置を提供する。

【解決手段】複数のメモリセルアレイが配置されたメモリセルアレイ部と、外部入出力回路が配置された周辺回路部と、複数のメモリセルアレイと周辺回路部とを接続する内部バス4と、を備え、周辺回路部は、複数の外部入出力バッファ23と、メモリセルアレイとの間で内部バスを並列に入出力するデータと複数の外部入出力バッファを直列に入出力するデータとを相互に変換する複数のバスインターフェース回路24と、を備え、複数のバスインターフェース回路間の距離d1が、複数の外部入出力バッファ間の距離d2及び内部バスの配線幅の最大値d3より狭くなるように、複数のバスインターフェース回路24は、内部バス4と複数の外部入出力バッファとの間にまとめて配置されている。

(もっと読む)

半導体装置、及び出力バッファのインピーダンスを調整する方法

【課題】出力バッファのインピーダンスを制御する複数の制御ビットを転送するデータバスの配線面積を削減できる半導体装置、及び出力バッファのインピーダンスを調整する方法を提供する。

【解決手段】インピーダンス制御情報を生成するZQ回路(ZQ回路40)と、前記インピーダンス制御情報を受けて自身のインピーダンスが制御される出力バッファ(出力回路80)と、を備え、前記インピーダンス制御情報を構成する複数の制御ビット情報は前記ZQ回路からシリアルに転送される。

(もっと読む)

半導体装置

【課題】出力クロック信号を生成して出力するまでに要する時間を短縮させる。

【解決手段】半導体装置は、第1のクロック信号のライズエッジ及び第2のクロック信号のライズエッジを合成して第1及び第2のクロック信号のライズエッジの間にライズエッジを有する第3のクロック信号を生成する第1の位相合成回路と、第1のクロック信号のフォールエッジ及び第2のクロック信号のフォールエッジを合成して第1及び第2のクロック信号のフォールエッジの間にフォールエッジを有する第4のクロック信号を生成する第2の位相合成回路と、第3のクロック信号のライズエッジを受けてライズ/フォールエッジの内の一方の位相を、第4のクロック信号のフォールエッジを受けてライズ/フォールエッジの内の他方の位相を其々調整した出力クロック信号を出力する第3の位相合成回路と、を備える。

(もっと読む)

181 - 190 / 2,599

[ Back to top ]