Fターム[2F063AA41]の内容

電気磁気的手段を用いた長さ、角度等の測定 (19,512) | 測定内容 (2,719) | 形状、輪郭 (169)

Fターム[2F063AA41]の下位に属するFターム

曲り、曲率、たわみ、そり (23)

表面の粗さ、不規則性 (74)

Fターム[2F063AA41]に分類される特許

61 - 72 / 72

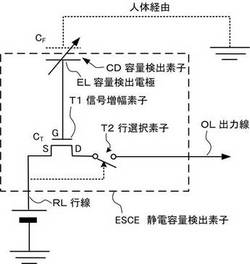

静電容量検出装置

【課題】 列毎に出力線を備える場合でも高い検出精度で静電容量検出が行える静電容量検出装置を提供する。

【解決手段】 行列状に配置された静電容量検出素子、各行に配置された静電容量検出素子を選択するための行線RL、各列に配置された静電容量検出素子からの信号を出力するための出力線OLを備える。各静電容量検出素子には、行線RLからの信号に基づいて当該静電容量検出素子の信号の出力線OLへの出力を制御する行選択素子T2を備えている。行線RLからの選択信号に基づいて選択状態とされた静電容量検出素子からの信号が当該静電容量検出素子に配置されている出力線OLに出力されるように構成されている。

(もっと読む)

寿命判定装置、その方法、及び電子機器

【課題】 静電容量検出装置の寿命を前もって正確に判定することが可能な寿命判定装置を提供する。

【解決手段】 複数の静電容量検出素子(31)を備えた静電容量検出装置(1)、静電容量検出装置(1)からの出力を記録する記録部(2)、及び当該静電容量検出装置(1)の出力の経時変化に基づいて当該静電容量検出装置(1)の寿命を判定する判定部(3)を備え、判定部は出力の移動平均等により寿命が近づいていることを判定する。

(もっと読む)

静電容量検出装置及びスマートカード

【課題】 薄膜半導体装置を用いて優良に動作する静電容量検出装置等を提供する。

【解決手段】 信号増幅素子T2を構成する信号増幅用薄膜半導体装置と行選択素子T4を構成する行選択用薄膜半導体装置と列選択素子T3を構成する列選択用薄膜半導体装置とを出力線Oと電源線Pの間に直列に接続する。この場合、信号増幅用薄膜半導体装置と行選択用薄膜半導体装置と列選択用薄膜半導体装置の抵抗値を適切に定めなければ検出感度が低下してしまうため、行選択用薄膜半導体装置のオン抵抗Rsrと列選択用薄膜半導体装置のオン抵抗Rscが信号増幅用薄膜半導体装置のオン抵抗Rsaよりも小さくなるように設定する。

(もっと読む)

ICカード

【課題】 ICカードのセキュリティを向上させる。

【解決手段】 生体情報を取得する生体認証部10と、上記生体認証部10からの上記生体情報と予め記憶した生体情報とを照合し、合致した場合にアプリケーションに対して有効状態とし、合致しなかった場合にアプリケーションに対して無効状態とする処理部とを備え、上記処理部は、所定のサンプリング間隔で上記生体認証部10から上記生体情報を取得し、その都度上記生体認証部10から上記生体情報と予め記憶した上記生体情報とを照合する。

(もっと読む)

静電容量検出装置及びスマートカード

【課題】 高精度に静電容量を検出できる静電容量検出装置を提供する。

【解決手段】 本発明の静電容量検出装置10は、容量値一定の基準コンデンサCRと、対象物表面HBとの間に静電容量CFを形成するセンサ電極SEと、基準コンデンサCRと静電容量CFとの容量比で定まるゲート電位に基づいてドレイン電流を変調する信号増幅素子Tr1と、信号増幅素子Tr1のゲート電位を接地電位にリセットするリセット素子Tr2を備える。対象物表面形状を読み取る際に、非選択列に属する信号増幅素子Tr1のゲート電位を接地電位にリセットすることで、高精度な検出精度を確保する。

(もっと読む)

静電容量検出装置

【課題】 静電破壊に耐性の高い静電容量検出装置を実現する。

【解決手段】

対象物の表面形状を読み取る静電容量検出装置において、M行N列に配置された静電容量検出素子(1)、当該静電容量検出素子(1)の各々に電源を供給する電源線を備えている。当該静電容量検出素子(1)は、当該静電容量に応じた電荷を蓄積する信号検出素子(4)、当該信号検出素子(4)が蓄積した電荷に対応した信号を増幅する信号増幅素子(T1)を含んでいる。当該信号検出素子(T1)は、容量検出電極(41)と、当該容量検出電極(41)の当該対象物が接触する側に設けられる容量検出誘電体膜(42)とを含んでいる。特に、容量検出誘電体膜(42)は、絶縁膜(160)と半導体膜(162)とを備えている。

(もっと読む)

情報記録媒体

【課題】 傷や汚れによる認識精度の低下、認識対象となる導電体の表面形状の認識精度のバラツキが少なく、セキュリティ上も安全な認証システムに用いることのできる情報記録媒体を提供する。

【解決手段】 認証システムに用いられる情報記録媒体1であって、薄板状の基材部2と、この基材部2の表面の少なくとも一部に形成された導電層4と、この導電層4の上に形成された誘電体層5とを有し、導電層4と誘電体層5によって読み取り情報の保持部3が形成され、この保持部3は、導電体の表面形状に対応した静電潜像を保持可能とされている。

(もっと読む)

導電体の表面形状認識装置及び導電体の表面形状認識方法

【課題】 認識精度の低下、バラツキが小さく、またユーザーが使用に際して不快感を覚えることを防止し、更に装置本体外では認識対象の表面形状を他人から見られることのない、導電体の表面形状認識装置及び導電体の表面形状認識方法を提供する。

【解決手段】 媒体10を表面形状認識装置1の内部で搬送させる搬送手段21、媒体10を帯電させる帯電手段6、導電体の表面形状に対応する読み取り情報として保持された静電潜像を現像してトナー像を形成するトナー像形成手段7と、トナー像の形状情報を作成する情報作成手段8と、この形状情報を出力する出力手段とを有する。

(もっと読む)

残留面状態検出

【課題】指紋を検出するセンサーにおいて、センサーに一度指紋を押し当て、その後にセンサーから完全に指が離れてから、押し当てられた時の指紋パターンを押し当てたセンサー表面から検出することを特徴とした指紋パターン検出方法。

【解決手段】図4は指を離した指紋センサーに40の(−)に帯電した粒子を近づけている図である。プラスとマイナスの電荷間にクーロン力が作用し、(−)帯電粒子は(+)帯電された表面に吸い付く。粒子40は例えばコピー機などのトナー、アルミ粉末などが使用できる。帯電させることが出来る粉であれば何でもよい。

そして、吸い付かない余分な粒子を取り除く。次にこの指紋センサー表面を指紋センサーの真上からCCD等の撮像素子を使用して撮影し、その画像をメモリーに取り込むことによって指紋パターンを検出することが出来る。

センサー表面の色と粒子40の色は同色以外にした方が画像にした時に指紋パターンがはっきりとして見やすい。

(もっと読む)

静電容量検出装置

【課題】 優良な静電容量検出装置を実現する。

【解決手段】 M行N列の行列状に配置されたM本の行線とN本の列線、及び此等交点に設けられた静電容量検出素子とを具備し、静電容量検出素子は信号検出素子と信号増幅素子とリセット素子とを含み、信号検出素子は容量検出電極と容量検出誘電体膜とを含み、信号増幅素子はソース電極とドレイン電極とゲート電極とを有する信号増幅用薄膜半導体装置から成り、リセット素子はソース電極とドレイン電極とゲート電極とを有するリセット用薄膜半導体装置から成り、信号増幅素子のゲート電極と容量検出電極とリセット素子のドレイン電極とが接続されて居る。

(もっと読む)

指紋認識装置

【課題】指紋センサに指の腹が接触し、さらに接地電極に指が確実に接触するようにして、常に理想的な状態で高精度の指紋認識を可能とすること。

【解決手段】指紋を検出する指紋センサ10と、指紋検出時に対向電極となる指を接地電位とするための接地電極3と、前記指紋センサ10と前記接地電極3が取り付けられる絶縁性の基板1とを備え、指紋の検出を行うとき、前記基板1を指紋を検出する指と他の指とで挟む構造とする。

(もっと読む)

物体の形状を決定する方法及びそのような方法のためのシステム

処理手段(12)及び静電感知装置(20)を使用するシステムが記載されている。該システムは、所定形状の物体(42,70)及び感知された静電的測定値(40)に対する静電的計算(44,46)の反復(56)から未知の物体の形状が計算されるような方法を実行する。上記所定の物体形状(70)は未知の物体形状(72)に向かって該物体形状が決定される(60,74)まで当該方法の各反復において変形される。該形状の変形は、上記所定形状に供給された電荷分布に依存するような静電電位の零等高線を計算することに基づくものである。  (もっと読む)

(もっと読む)

61 - 72 / 72

[ Back to top ]