Fターム[2G132AA03]の内容

Fターム[2G132AA03]に分類される特許

101 - 120 / 151

レジスタファイル及びその記憶素子

スキャン制御回路は、スキャン接続構成回路及びメモリアレイの最終レジスタから先頭レジスタの順番に第1シフトクロックを入力させることにより、まずメモリアレイの最終レジスタの各第1素子からスキャン接続構成回路の各第2記憶素子にデータを並列的にコピーし、スキャン接続構成回路の最下位ビットの第2記憶素子からシフトデータをシフトレジスタ出力端子外部出力させる。次にメモリアレイの上位側のレジスタの各第1記憶素子から下位側のレジスタの各第1記憶素子に順次データを並列的にコピーする。そして先頭レジスタについては、その最上位ビットを除く各第1記憶素子にスキャン接続構成回路の最上位ビットを除く各第2記憶素子のデータを並列的にコピーし、最後に先頭レジスタの最上位ビットの第1記憶素子に第2シフトクロックを入力させることによりシフトレジスタ入力端子に外部から入力しているシフトデータをコピーさせる。この処理をスキャン開始時にメモリアレイに保持されていたデータがシフトレジスタ出力端子から外部に出力し終わるまで繰り返す。  (もっと読む)

(もっと読む)

フラッシュメモリ混載マイコン及びその検査方法

【課題】製造工程全体の工程数を減少して生産時間を短縮することができるフラッシュメモリ混載マイコン及びその検査方法を提供する。

【解決手段】フラッシュメモリ部のゲートストレステストモードをマイコンのバーインテストモード時に同時活性するために、バーイン工程時に同時にフラッシュメモリ部のゲートストレス印加を行なった後に、バーイン後の閾値選別Tp13を含む動作速度テストを行なうことにより、ゲートストレス印加をマイコンのバーイン工程時に同時実施することを可能とし、独立したゲートストレス印加工程を省略する。

(もっと読む)

半導体集積回路

【課題】 複数のCPUを内蔵する半導体集積回路をテストする際に、半導体集積回路の内部において複数のCPUの演算結果を期待値と比較判定することにより、テスト時間を短縮する。

【解決手段】 この半導体集積回路は、同一のテストパターンに基づいて演算を行うことにより、それぞれの演算結果を出力値パターンとして出力する複数のCPU20と、同一の期待値パターンをパラレルに入力し、複数のCPUからそれぞれ出力される出力値パターンを期待値パターンと比較することにより、複数のCPUについての複数の比較結果をそれぞれ出力する複数組の比較器41〜44と、複数組の比較器からそれぞれ出力される複数の比較結果に基づいて、複数のCPUの内の少なくとも1つから出力される出力値パターンと期待値パターンとが一致しない場合に不一致を示す情報を出力する不一致検出回路50とを具備する。

(もっと読む)

半導体集積回路及びそのバーインテスト方法

【課題】

効率のよいバーインテストを実施可能なフラッシュEEPROMを内蔵する半導体集積回路、及び、そのバーインテスト方法の提供。

【解決手段】

モード選択部40からの制御信号C2のレベルを変えることによって、機能部10の動作モードを通常モードから、テスト用の命令コードを格納したROM30からデータを読み出すテストモードに切り替える。そして、テストモード下で、前記第1の制御信号C1のレベルを変えることによって、第1の選択回路12の出力先及びプログラムカウンタ11の動作を切り替え、フラッシュEEPROM20を活性化する第1のバーインモードと機能部10を活性化する第2のバーインモードとを交互に実行する。

(もっと読む)

集積回路

【課題】集積回路の故障箇所における故障前後の特性データなどを記憶し、故障箇所の特定および軌跡が可能な集積回路を提供する。

【解決手段】集積回路100に不揮発性メモリ部110を備え、前記集積回路100の機能ブロック120の電流値の特性データ、または集積回路100の温度変化を示す電流値データ、または機能ブロック120内の振幅値の特性データ、または機能ブロック120内の回路動作を制御するデータなどを、それらが変化する毎に、前記不揮発性メモリ部110に書き換え可能にする。

(もっと読む)

静電気サージ反射装置、電子機器の評価装置、及び被評価装置の評価方法

【課題】 被評価装置に対しては、所定の放電電圧に設定された静電気サージを減衰させ

ることなく印加させることができる一方、被評価装置を評価するための評価装置に対して

は、静電気サージから確実に保護することができる静電気サージ反射装置を提供すること

。

【解決手段】 ECU30(被評価装置)と、ECU30を評価するための計測装置1と

を接続するラインに介装される静電気サージ反射装置20であって、一端側がECU30

側のラインに接続され、他端側が計測装置1側のラインに接続されるチョークコイル25

を含んで構成されている。

(もっと読む)

マルチコア集積回路における同時コア試験

集積回路に含まれる複数のコアを同時に試験する方法およびシステムの各種実施形態が開示されている。一実施形態では、集積回路は2つ以上のロジックコアを含んでもよい。ICはさらに、コアに接続された構造スキャン試験ハードウェアを含んでもよい。この構造スキャン試験ハードウェアは、スキャン試験ベクトルデータをロジックコアの各々に関連づけられたスキャンレジスタに入力し、ICに含まれるロジックコア上でスキャン試験を同時に実行し、複数のコアに対するスキャン試験結果を自動試験装置(ATE)に同時に出力することができる。一実施形態において、複数のコアに対する試験結果のそれぞれの要素は、各ストローブウィンドウの間において、ATEへの入力チャンネル上に各コアからの試験結果データの一つの要素が単一の出力線上において存在するように、インターリーブされる。  (もっと読む)

(もっと読む)

半導体集積回路

【課題】 動作プログラムの命令コードをRAM1320に配置し、CPU1310はRAM1310から命令コードを読み出しても、ROM1320が読み出し動作をした状態で、所定の動作の動作時電源電流テストを実施出来る半導体集積回路を提供することを目的とする。

【解決手段】 テストモード信号をイネーブルにし、RAM1330の命令コード読出し動作と同時に、ROM1320も読み出し動作状態にするROM制御部1340を備えることで、ROM1320の読出し動作をした状態で、所定の動作の動作時電源電流テストを行うことが可能となる。

(もっと読む)

非接触式プリント基板検査システム

【課題】 検査治具やフィクスチャーへのケーブル接続が不要で、更にはパッチプログラムの移植も容易に行うことができる、非接触式プリント基板検査システムを得る。

【解決手段】 CPUを搭載したプリント基板に、通信用外部端子を設けたRFIDタグを実装し、CPUの通信ポートにRFIDタグの通信インターフェース回路の信号線を接続する。また、CPUのプログラムメモリに検査実行プログラム及びパッチ移植プログラムを内蔵し、組立・検査ラインに設置されたリーダー/ライターとRFIDタグ間で無線通信を行い、プリント基板単体時においては検査プログラムの受信及び不揮発性メモリへの書込みと、筐体へのプリント基板組込み時においては検査コマンドの受信及び当該検査コマンドに対応した検査プログラムの実行と、パッチ移植コマンドの受信時においてパッチプログラムの移植を実行する機能を持たせる。

(もっと読む)

ディジタル電子パッケージにおけるはんだ接合不良の検出方法および回路

【課題】 ディジタル電子パッケージの通常動作の間にはんだ接合ネットワークの完全性を評価する方法および回路を提供する。

【解決手段】 内部で接続されている入力/出力バッファ(146a/b、148a/b)を有するFPGA(120)またはマイクロコントローラのような、ディジタル電子パッケージのはんだ接合完全性を評価する際、1つ以上のはんだ接合ネットワーク(153a)を通じて時間可変電圧を印加して、電荷蓄積素子(156)を充電する。各ネットワークは、パッケージ内にあるダイ(138)上にあるI/Oバッファ(146a)と、はんだ接合接続部(124)とを含む。通例、1つ以上のこのような接続部が、パッケージの内側、そしてパッケージと基板との間にある。素子を充電する際の時定数は、はんだ接合ネットワークの抵抗に比例するので、電荷蓄積素子間で測定した電圧は、はんだ接合ネットワークの完全性の指標となる。

(もっと読む)

DLL回路を内蔵する集積回路装置及びその試験方法

【課題】 DLL回路を内蔵する集積回路装置の内部動作に起因するDLL回路の特性をチェックできる試験方法及びかかる試験ができる集積回路装置を提供する。

【解決手段】 集積回路装置10は,基準クロックDQSから所定の位相遅れたサンプリングクロックCLK90,CLK270を生成するDLL回路,基準クロックDQSに同期して入力されるデータを取り込む入力回路S/P,外部メモリ20へのアクセス制御を行い当該データに対して所定の処理を行う複数の機能ブロックからなる機能マクロ30を有する。試験方法は,試験装置から外部メモリへの読み出し動作を行う一部の機能ブロックだけを動作させる試験プログラムをダウンロードする工程,試験プログラムによりこの機能ブロックを動作させる工程,この機能ブロックの動作により生成されるデータを期待値データと比較する工程,及び生成データが期待値データと異なるとき不良と判定する工程を有する。

(もっと読む)

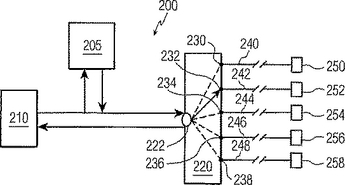

テスト信号の自動検出及び経路指定

回路テストアプローチは、テスト信号を自動的に検出し、複数のテスト回路経路(240、242、244)に沿って経路指定する設定可能なスイッチ制御を有する。本発明の実施例によれば、マイクロコントローラ(205)は、テスト信号(即ち、デジタル及び/又はJTAGのテスト信号)を自動的に検出する割り込みルーチンを用いて入力ノードを監視するようにプログラムされる。テスト信号を検出すると、マイクロコントローラは、テスト回路経路の一つに沿ってテストデータを経路指定するように制御可能スイッチ(220)を制御する。このアプローチと共に、テスト信号を経路指定する手動の切り替えは、必要とされず、切り替えのための回路経路へのアクセスが困難又は不可能である用途において有用であると考えられる。  (もっと読む)

(もっと読む)

論理検証装置

【課題】入力データの生成と出力データの照合を、端末装置に代えて、再構成可能素子内で実施する機構を付加することにより、端末装置と再構成可能素子との間のデータ転送回数の増加を抑制し、再構成可能素子のピン数の増加を抑制し、高効率なプロパティ利用検証を高速に実施することを可能にする論理検証技術を提供する。

【解決手段】検証対象論理回路105は、CPU107と、テストプログラム及び結果値が格納される内部メモリ108とを備え、検証対象論理回路105が実装される再構成可能素子103は、前記テストプログラム実行中の各サイクルにおいて、各プロパティが満たされているか否かを照合した照合結果が格納されるシャドウメモリ114を備え、CPU107が、内部メモリ108に格納された値を読み出す命令を使用して、シャドウメモリ114に格納された前記照合結果を読み出す構成とする。

(もっと読む)

マイクロコンピュータ

【課題】 メモリデバイスのアドレスデコーダを対象とする静止状態電源電流測定に要する時間を短縮することができるマイクロコンピュータを提供する。

【解決手段】 マイコンに搭載される4つのROM3A〜3Dを選択するためのアドレスデコーダ11は、IDDQテスト信号が与えられると、測定用のテストパターンとして与えられるアドレスがLSB側の16ビットに亘り連続する領域については、その領域に対応するROM3A〜3Dを同時に選択するようにデコード信号を出力する。

(もっと読む)

機能検査方法

【課題】 検査のための余計なメモリを持つことなく、組込み電子機器の機能検査が確実にできるようにする。

【解決手段】 外部ホスト端末30から供給された検査プログラム及び/又はデータを、JTAG準拠のポート及びバウンダリスキャンセルを搭載する機器ホストCPU21のバウンダリスキャンセルにセットし、機能検査が行われる第1の機能ブロック24及び/又は第2の機能ブロック25に送信、実行し、出力値を計測手段に送信、測定する。

(もっと読む)

半導体装置とそのテスト装置及びテスト方法。

【課題】

マイコン等の入出力端子を多数有する半導体装置の出荷検査を行う際には、多くの時間と高価な設備が必要であった。

【解決手段】

本発明の半導体装置は、半導体装置の入出力端子に接続されるバッファ回路と、前記バッファ回路の入出力状態を切り替えるバッファモード切り替え信号を出力するテスト制御回路と、前記テスト制御回路に接続されるテスト端子とを備え、テストモード時に、前記テスト端子に入力されるテスト信号に基づいて隣接端子間ショート検出テストを行うためのショート検出信号を生成し、前記ショート検出信号を前記バッファ回路に送信する前記テスト制御回路とを有している。これにより、半導体装置は内部にテスト用の内部ROM及びその命令コードを必要としない。つまり、半導体装置の設計の簡素化とテスト時間の短縮及び簡素化が可能である。

(もっと読む)

半導体装置およびその検査方法

【課題】 品質の向上を実現可能な半導体装置およびその検査方法を提供する。

【解決手段】 ある検査工程において、被測定デバイス40のスタンバイ電流値をIC検査装置41で測定し、その測定したスタンバイ電流値を被測定デバイス40が備えた不揮発性メモリ12に書き込んでおき、その後の別の検査工程において、被測定デバイス40のスタンバイ電流値を例えば別のIC検査装置41で測定した際に、その測定データと前記不揮発性メモリ12に書き込んでおいたデータを読み出すことで得た測定データとを相対的に比較することで、複数の検査工程にまたがるスタンバイ電流値の変化を検証することが可能となる。

(もっと読む)

自動的に生成されたテストプログラムのための採点機構

【課題】本発明は、テストコードの実行がシミュレートされている間に選択された機能状態の適用範囲で作られる評価をするテストプログラムの生成の自動化を提供する。

を提供する。

【解決手段】データ処理装置のためのテストプログラムは、テストプログラムを形成している集団におけるプログラム命令の順序付けられたリストからなる例の変更について、遺伝子アルゴリズムを使用して生産される。集団は、特定の例が集団の中又は外へ交換されるべきであるか否かについてなされる決定がされているとき、集団全体がデータ処理装置において所定の機能ポイントの刺激に対して採点されることによる測定を使用して評価される。

(もっと読む)

プロセッサ、そのエラー解析方法及びプログラム

【課題】チップマルチプロセッサのバウンダリスキャンを拡張したエラー情報収集をチップシングルプロセッサとのピン互換を損なうことなく実現する。

【解決手段】LSIチップ10上に形成されたCPUコア14−1、14−2に内蔵された複数のエラー保持用ラッチを一本のエラー収集用スキャンチェーン48に接続構成し、エラー収集用スキャンチェーン48の中をCPUコア14−1、14−2に対応したCPUラッチ群56−1、56−2に分け、テスト動作時に2つのCPUコアの内の縮退したCPUコアに対応したエラー保持用ラッチ群のラッチ内容をマスクさせるマスク回路58−1、58−2を設け、エラー発生時にエラー収集用スキャンチェーン48をスキャンアウトしてエラー情報を収集する

(もっと読む)

デバッグ用レジスタおよびデータ転送方法

【課題】 少ないクロック数でデバッグメモリ空間の連続するアドレスのデータを転送することができるデバッグ用レジスタ、およびデータ転送方法を提供する。

【解決手段】 アドレスレジスタおよびPrAccレジスタからのデータのシフトアウトとデータレジスタおよびPrAccレジスタへのデータのシフトインを同時に実行し、シフトアウトされたアドレスレジスタの値が予想した値であったときは、シフトインされたデータのデータレジスタへの書き込みおよびPrAccレジスタへの書き込みを実行する命令を用い、シフトインするデータとして、次にアクセスが予想されるアドレスから取得したデータと、デバッグが継続して実行されるようプロセッサアクセスのペンディングを制御するPrAccデータを順次入力することにより、デバッグメモリ空間の連続するアドレスから順次データを取得して前記データレジスタに順次書き込む。

(もっと読む)

101 - 120 / 151

[ Back to top ]