Fターム[2G132AA03]の内容

Fターム[2G132AA03]に分類される特許

61 - 80 / 151

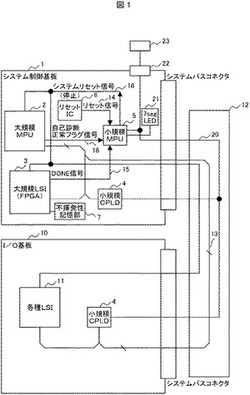

小規模MPU搭載の大規模MPUシステム

【課題】大規模MPU・大規模LSIを使用することで、絶対最大定格値の低下・静電耐圧の減少など故障発生要因の閾値低下により高信頼化が計れなかった。

また、電源投入時に各I/O基板を含めたシステムの異常を監視、異常情報を不揮発性記憶部に格納しても、大規模MPUの基本モニタが動作しない場合、自己診断情報を確認することができずに、原因解明の早期絞込みが困難であるという問題があった。

【解決手段】電源投入時に大規模MPUによる自己診断を行ない、システムに異常があれば立上げを停止する機能を有する小型で最小限の機能を持った故障率の低い小規模MPUを実装し、信頼性の高いシステムの構築を可能とする。また、各I/O基板に実装した書込み可能な不揮発性記憶部に自己診断時の診断情報および異常情報を格納することで、大規模MPUが異常で基本モニタが動作しない場合にも、早期原因の解明を可能とする。

(もっと読む)

半導体集積回路

【課題】内部のテスト回路にテスト用の信号を入力するための端子を、より柔軟に設定することができる半導体集積回路を提供する。

【解決手段】マイコン1の複数の入力端子3に対応して出力選択回路4,5とデータラッチ6,7とを配置し、テスト端子設定回路9が、データラッチ6,7に対してラッチ信号,並びにリセット信号を出力することで、出力選択回路4,5は、設定に応じて入力端子3に与えられる信号をテスト回路8側にも出力させる。そして、テスト回路8は、入力端子3より出力選択回路4,5を経由して与えられるテストデータに基づいて主回路部2の機能をテストする。

(もっと読む)

半導体集積回路

【課題】RTレベルから最終的なASICまでの各抽象度の設計段階で、検証対象回路の内部の動作をチェックできる半導体集積回路を提供する。

【解決手段】入力信号INに従って予め定められた論理処理を行って出力信号OUTを出力するステートマシン11と組み合わせ回路12を有するシステムLSI10に、信号線13の状態の異常を検出するための機能検証回路20を設ける。機能検証回路20は、ハードウエアに変換可能なハードウエア記述言語で記述され、かつ論理回路として合成されたもので、内部の信号線13の状態の履歴を保持する状態履歴保持部21と、状態履歴保持部21に保持された状態履歴に基づいて信号線13に出力されるべき信号を生成する遷移チェック信号生成部22と、遷移チェック信号生成部22で生成された信号と信号線13に出力された信号を比較する比較部23と、比較結果を出力する出力部24を備える。

(もっと読む)

ECU機能検査装置

【課題】従来のECU機能検査装置では、準備しておくセンサの数が多くなり検査装置の規模が肥大化したり、車種毎での段取り換えに手間を要したりするなどして、ECU機能の検査を、量産工程にて行うことが困難となる恐れがあった。

【解決手段】ECU30に対して検査用信号を出力し、該信号を受信したECU30からの応答出力を検査するECU機能検査装置1であって、ECU機能検査装置1は検査用信号の出力およびECU30からの応答出力の検査を行う検査処理装置10と、検査処理装置10とECU30との間の通信を行う通信ボード20とを備えており、通信ボード20は、1本の通信線で電源供給と電流通信とを行うことを可能とする複数の通信IC240を搭載しており、各通信IC240のGND電極は、通信ボード20のGND配線に対して絶縁されており、該各通信IC240のGND電位が独立している。

(もっと読む)

半導体集積回路、マイクロコンピュータ、および、それらの動作モード切替え方法

【課題】従来の動作モードの設定においては、製品の出荷前と出荷後で動作モードの設定条件を変更することができなかった。

【解決手段】本発明の半導体集積回路は、書換え可能な不揮発性メモリと、動作モード設定信号が入力される動作モード設定端子と、動作モード設定信号に基づいてカウント動作を行う第1のカウンタと、を備え、不揮発性メモリは、第1のパルス数設定値を格納し、第1のカウンタのカウント値と第1のパルス数設定値が一致した場合に動作モードの切替えを実行することを特徴とする。

(もっと読む)

半導体装置

【課題】外部負荷容量に依存する外部アクセスにおいて、正確なAC測定を可能とする半導体装置を提供する。

【解決手段】メモリアクセスの制御を行う外部メモリ制御部2と、外部アクセス主信号と外部アクセス従信号の経路に対して外部負荷容量を接続・分離する外部負荷容量スイッチSw3,Sw4と、テストアクセス主信号とテストアクセス従信号の経路上にテスト容量を配置するテスト容量部C1,C2と、テスト容量部を外部アクセス主信号および外部アクセス従信号の経路に対して接続・分離するテスト容量スイッチSw1,Sw2と、外部負荷容量スイッチとテスト容量スイッチと外部メモリ制御部を制御するテストモード制御部1と、テストアクセス主信号に対するテストアクセス従信号の遅延時間を測定する遅延時間測定部3と、遅延時間とACスペック格納部4のACスペックを比較する比較部5とを備える。

(もっと読む)

半導体装置と半導体装置のテスト方法

【課題】マルチチップモジュールの性能を維持しつつ、信頼性の高い試験を可能にした半導体装置とテスト方法を提供する。

【解決手段】第1半導体チップと上記第2半導体チップとでマルチチップモジュールを構成する。第1半導体チップから第2半導体チップに対する動作指示の有効/無効を示す第1信号を外部端子に接続する。第2半導体チップの動作指示の有効/無効を受け取る第2信号を外部端子に接続する。第1半導体チップのリセット指示を行なう第3信号を外部端子に接続する。第1信号と第2信号マルチチップモジュール外に一旦引き出し、マルチチップモジュール外で結合変更可能なように構成し、第1、第2、第3信号の制御をマルチチップモジュール外部で行なうことで、試験対象とすべき半導体チップを単体の半導体チップを持つ半導体装置と等価にテスト可能にする。

(もっと読む)

システムLSI検証装置及びシステムLSI検証プログラム

【課題】システムLSIに含まれるプロセッサモジュールを検証する。

【解決手段】システムLSI検証装置10は、検証対象であるプロセッサモジュールの設計の記述データが記憶された回路記述記憶部15と、記述データと検証環境の仕様が記述された検証環境仕様ファイルに従って、検証用タスクファイルを生成して検証環境を生成する検証環境生成部17と、検証用タスクを起動するための環境コマンド関数を含むテストプログラムが記憶されたテストプログラム記憶部18と、テストプログラムに従って論理シミュレーションを実行する論理シミュレーション部19を備える。

(もっと読む)

半導体集積回路およびその診断方法

【課題】LSIへのアナログ入力部のA/D変換器の故障もしくは多入力マルチプレクサーの故障、応用システムのマザーボードの上での各種センサーの断線、電源ショート、グランドショート等の不具合を診断するに際して、診断回路のオーバーヘッドを削減すること。

【解決手段】半導体集積回路は、A/D変換器10bit A/D_Convと、2ビットの入力信号C、Bに応答して高レベル(H)、低レベル(L)、中間レベル(M)、高インピーダンス(Hi−Z)の4状態の出力信号Oを生成する診断信号生成回路BIDT Cirtとを含む。BIDT Cirtから生成されたH、L、Mの3状態の出力信号OをA/D変換器にてA/D変換を実行する。A/D変換されたディジタル出力信号から、A/D変換器の良・不良を自己診断する。また、マルチプレクサーMPXやセンサーの不具合も診断することができる。

(もっと読む)

メモリ要素の非接触プログラミング及び試験

本発明は、ワイヤレス近距離通信インタフェースを有する電子装置のメモリ要素の非接触プログラミングに対する方法を提供する。本方法は、ワイヤレス近距離通信インタフェースの存在を検出するための問合せを実行し、問合せに応答し、ワイヤレスインタフェースからのデータを受信し、データは電子装置のハードウェア構成を示し、ハードウェア構成に基づきメモリ要素をプログラミングするためのプログラミングデータを選択し、ワイヤレス近距離通信インタフェースにより受信されるべく選択されたプログラミングデータを送信するステップを有する。本方法は、さらに、問合せを検出し、問合せに応答し、ワイヤレスインタフェースを介してデータを送信し、データは電子装置のハードウェア構成を示し、ワイヤレス近距離通信インタフェースにおいてプログラミングデータを受信し、プログラミングデータに従いメモリ要素をプログラミングするステップを有する。本発明は、本発明の方法を実行するための装置も提供する。  (もっと読む)

(もっと読む)

フォールト・トレランス・コンピューティング・システムにおけるエラー・フィルタリング

電子回路におけるシングル・イベント故障を許容するためのシステムが開示される。このシステムは、メイン・プロセッサと、メイン・プロセッサに応答する故障検出プロセッサであって、ボータ(多数決)論理回路を備える故障検出プロセッサと、故障検出プロセッサに応答する3つ以上の論理デバイスであって、それらの各出力がボータ論理回路を通るものである3つ以上の論理デバイスと、プログラマブル・エラー・フィルタとを備える。ボータ論理回路の出力は、プログラマブル・エラー・フィルタに結合される。  (もっと読む)

(もっと読む)

半導体集積回路、及びBIST回路設計方法

【課題】面積オーバーヘッドを考慮しつつ、BISTのテスト速度を向上させることが可能な半導体集積回路を提供する。

【解決手段】 複数のメモリ回路とテストベクタを出力するBIST回路140とを備える半導体集積回路であって、BIST回路140からそれぞれのメモリ回路へテストベクタを供給する信号線路上に、BIST回路140から出力されるテストベクタを、共通のクロック信号に応じて隣接するマクロセルへ転送する1以上のレジスタ回路150を有することを特徴とする。

(もっと読む)

電子制御装置、及び、演算機能検査方法

【課題】通信負荷を軽減しつつより迅速に、CPUやマイクロプロセッサの演算機能を検査することが可能な電子制御装置、及び、演算機能検査方法を提供すること。

【解決手段】複数のCPUを備え、複数のCPUに含まれる一のCPUの演算機能を他のCPUとの協働により検査可能な電子制御装置1であって、演算機能の検査を受ける被検査CPUが、所定のプログラム12に基づき検査用の演算課題を作成すると共に作成した演算課題の解答を自己の演算機能により作成して、被検査CPUを監視する監視CPUに対して作成した演算課題及び解答に関する情報を送信し、監視CPUが、送信された演算課題及び解答に関する情報に基づいて、被検査CPUが有する演算機能が正常か否かを判定することを特徴とする。

(もっと読む)

試験アクセス・ポート・スイッチ

試験アクセス・ポート(TAP)スイッチは、電子システムと、電子システムに対する外部リソースとの間の集中型シリアル試験インタフェースを提供する。電子システムは、TAPスイッチと、複数の電子回路部品とを含んでいる。電子回路部品はそれぞれ、TAPスイッチに接続されたTAPを有している。1または複数の実施形態では、TAPスイッチは、例えば、命令に追加または事前追加されたコードのように、シリアル命令に含まれる選択コードに応答して、TAPのうちの選択された1つへクロック信号を提供するように構成された第1の回路を備える。このTAPスイッチは更に、TAPスイッチによって受け取られたシリアル命令を、選択されたTAPへ渡すように構成された命令レジスタ(IR)を備える第2の回路と、選択コードに応答して、選択されたTAPから受け取ったシリアル命令を、TAPスイッチの出力へと転送するように構成された第3の回路とを備える。  (もっと読む)

(もっと読む)

ディジタル処理装置の検査システム

【課題】ディジタル処理装置が通常モード時に何らかのトラブルで検査用データを受信しても、誤動作を確実に防止できること。

【解決手段】検査装置13は、検査治具14によって、ディジタル処理装置11の通常使用出力端子になるステータス信号出力端子と接続し、検査モード切換指令発生器13Aによってステータス信号出力端子をオン状態に強制する。マイクロコンピュータ11Bは、ステータス信号出力端子のオン状態の認識で機能検査を実行する。検査結果は、調歩同期式シリアルデータ通信で検査装置または上位制御装置12に伝送する。この伝送に、検査モードと通常モードでは異なる通信レートにすること、パリティ信号を、検査モードと通常モードの一方を奇数パリティとし、他方を偶数パリティとすることを含む。

(もっと読む)

半導体集積回路及び動作試験方法

【課題】動作保証温度が高く設定されている場合でも、動作試験を精度よく行う。

【解決手段】マイクロコンピュータ(1)は、半導体基板(2)と、入出力回路(4,4A〜E)と、複数の発熱回路(5A〜5D)と、発熱回路を制御する制御信号(S1)を入力するパッド(3A〜3C)と、温度センサ(7)と、温度センサによる検出信号(S3)を外部に出力するパッド(3D,3E)と、デコーダ(6)等とを備える。入出力回路は、半導体基板に所定間隔を隔てて配置されたパッドに接続されており、入出力バッファ等を備える。発熱回路は、入出力回路の近傍に配置されている。温度センサは、pn接合シリコンダイオードである。デコーダは、温度センサによる検出信号に基づいて、評価用治具に備えられた制御回路が生成した制御信号をデコードして、デコード結果に応じて動作させるべき発熱回路をブロック単位で選択する。

(もっと読む)

半導体集積回路

【課題】複数の順序回路として少なくともレベルセンス型順序回路を用いたシステムにおいて、動作周波数を高めると共に、信頼性を向上させる。

【解決手段】マイクロコンピュータ(1)は、クロック供給元とされるクロック発生回路(2)と、クロック信号CLKに同期動作する機能モジュールと、機能モジュールに含まれ、クロック供給先とされるレベルセンス型順序回路(12〜14)と、クロック信号をレベルセンス型順序回路に伝播するクロック供給系(11)等とを備える。クロック供給系は、クロック発生回路から出力されるクロック信号を複数の分岐を介して末端に伝播するクロック配線(20)を有する。クロック配線の途中には、少なくともパルス生成回路(26,28,29)が配置される。パルス生成回路は、レベルセンス型順序回路の入力動作期間の終点を規定するクロック信号の立ち下がりエッジの変化タイミングを可変とする。

(もっと読む)

回路装置、このような回路装置を有するデータ処理装置及びこのような回路装置へのアタックを識別する方法

回路装置(100、100′、100″)、特にアクティブシールドを改善するとともに、この回路装置(100、100′、100″)への少なくとも1つのアタックを識別する方法であって、テストデータを発生させ、標準的なデータの形態で、又はテストデータの形態で、又はその双方の形態でデータ信号を伝達するように設計されたデータライン(50)の少なくとも1つの群を介して前記テストデータを伝送し、伝送されたテストデータを受信し、受信したテストデータを予期するテストデータと比較し、受信したテストデータと予期するテストデータとの間のいかなる不一致をも確定又は決定し、前記回路装置(100、100′、100″)がアタックされたかどうかを検査、特に識別するのに必要とする電力を少なくするようにする方法を改善するために、発生された新たな又は最後のテストデータを伝送するのに、データライン(50)の群の一部分を選択することを提案する。  (もっと読む)

(もっと読む)

半導体集積回路装置の検査方法

【課題】 半導体集積回路装置の静的消費電流テストを、一枚のウェーハ上で、複数の半導体集積回路装置で同時に行っても、半導体集積回路装置個々の静的消費電流特性を、高い精度で測定できる半導体集積回路装置の検査方法を提供すること。

【解決手段】 互いに機能が異なっている複数の機能回路2〜5を、1つの半導体基板に混載した半導体集積回路装置の検査方法であって、機能回路2〜5相互間を、半導体基板内に設けた分離領域10によって互いに分離すると共に、分離領域10を半導体基板の側面に接触させ、少なくとも複数の機能回路2〜5に動作電圧を与えるために、複数の機能回路2〜5に少なくとも1つの高電位電源端子及び低電位電源端子とを具備し、複数の機能回路2〜5のうち少なくとも2つを同時に検査する。

(もっと読む)

テストパターン生成装置及びその方法

【課題】LSI機能をシミュレートさせるためのテストベンチが大規模複雑化し、これらをシミュレートするためのシミュレーション時間が増大する。

【解決手段】評価対象とするLSIチップ101を搭載する実機セットボード装置100でLSIチップ101を動作させ、そのLSI端子信号111〜116,124,125をプローブし、そのプローブ信号118〜123,127を任意のフォーマットのテストパターン170へ変換することで、簡便にかつ短時間でのテストパターン生成が可能となる。

(もっと読む)

61 - 80 / 151

[ Back to top ]