Fターム[2H092JA39]の内容

液晶−電極、アクティブマトリックス (131,435) | 能動素子 (19,865) | 三端子素子 (19,408) | 構造 (10,751) | ゲート電極 (2,011) | 厚さ (144)

Fターム[2H092JA39]に分類される特許

81 - 100 / 144

表示装置

【課題】極めて簡単な構成にも拘わらず、半導体層への光照射を低減し、オフ電流の発生の抑制を図った薄膜トランジスタを具備する表示装置の提供。

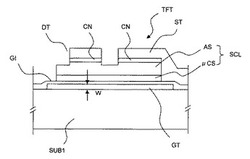

【解決手段】画像表示部が形成された基板に薄膜トランジスタが形成された表示装置であって、

前記薄膜トランジスタは、

ゲート電極と、

前記ゲート電極を被って形成されたゲート絶縁膜と、

前記ゲート絶縁膜上であって前記ゲート電極に重畳して形成される半導体層と、

前記半導体層上に形成され互いに対向して配置された一対の電極と、

を備え、

前記半導体層は、平面的に観た場合、前記ゲート電極の形成領域内に配置され、前記ゲート電極側から、結晶性半導体層および非晶質半導体層の順次積層体から構成され、

前記ゲート電極は、少なくとも前記半導体層と対向する領域において、光透過率が0.3%以下となる膜厚で形成されている。

(もっと読む)

半導体装置

【課題】ゲート配線として耐熱性の導電性材料であるタングステン層を用いた場合に、タングステン層の比抵抗を低くすることによって、配線抵抗を十分に低減することを目的とする。

【解決手段】半導体層と、ゲート配線と、前記半導体層と前記ゲート配線との間に挟まれたゲート絶縁層とを有し、前記ゲート配線はタングステン層を有し、前記タングステン層中の酸素濃度を30ppm以下とすることによって、配線抵抗を十分に低減することができる。

(もっと読む)

液晶表示装置用基板及びそれを用いた液晶表示装置

【課題】本発明は、スイッチング素子が形成されたアレイ基板側にカラーフィルタを形成したCF−on−TFT構造の液晶表示装置用基板に関し、フォトリソグラフィ工程を代表とする製造プロセスを簡略化でき、且つ高い信頼性を有する液晶表示装置用基板を提供することを目的とする。

【解決手段】ガラス基板3上にマトリクス状に配列された複数の画素領域Pから引き出されたゲートバスライン6に電気的に接続された第1の端子電極52aと、画素電極の形成材料でガラス基板3上に直接形成された第2の端子電極52bと、第1及び第2の端子電極52a、52bを電気的に接続する電極繋ぎ換え領域52cとを備え、外部回路とゲートバスライン6とを電気的に接続する外部接続端子を有するように構成する。

(もっと読む)

半導体装置及びその作製方法

【課題】薄膜トランジスタのチャネルが形成される領域を含む半導体層と、ソース電極層及びドレイン電極層のコンタクト抵抗(接触抵抗)が小さい薄膜トランジスタを提供することを課題の一とする。また、配線の電気抵抗が小さい薄膜トランジスタを提供することを課題の一とする。また、ソース電極層及びドレイン電極層の端部に生じる段差の少なくとも一部を覆う半導体層をキャリアが滞りなく移動できる構造を有する薄膜トランジスタを提供することを課題の一とする。

【解決手段】薄膜トランジスタを形成するにあたって、第1電極層上に第1配線層を設け、第2電極層上に第2配線層を設け、第1電極層が第1配線層の端部から延在し、第2電極層が第2配線層の端部から延在し、第1電極層の側面及び上面と第2電極層の側面及び上面に半導体層が電気的に接続するように設ける。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】ソース・ドレイン電極形成時の活性層へのダメージを抑制するとともに、製造工程の簡略化を図ることが可能な薄膜トランジスタ及びその製造方法を提供する。

【解決手段】導電層50をエッチングによってパターニングすることにより、活性層18に接触するソース電極20及びドレイン電極22を形成するとともに、ソース電極20とドレイン電極22を除いた部分にソース電極20及びドレイン電極22よりも厚みが薄い導電層を第1保護薄膜56として残存させる工程と、第1保護薄膜56を半導体又は絶縁体に化学変化させて第2保護薄膜24を得る工程と、を含む薄膜トランジスタの製造方法を採用する。

(もっと読む)

結晶性半導体膜の作製方法及び薄膜トランジスタの作製方法

【課題】結晶粒径が大きく、均一な結晶性半導体膜を作製する方法を提供する。

【解決手段】絶縁膜上に接して結晶性半導体膜を形成する第1の工程と、前記第1の工程よりも核生成頻度が低い条件により結晶性半導体膜を成長させる第2の工程と、により結晶性半導体膜を作製する。第2の工程は、第1の工程よりも半導体材料ガスの流量比が小さい条件で行う。これにより、結晶粒径が大きく、均一性の高い結晶性半導体膜を得ることができ、結晶性半導体膜の下地膜に対するプラズマダメージを従来よりも低減することができる。

(もっと読む)

液晶表示装置用基板及びそれを備えた液晶表示装置及びその製造方法

【課題】本発明は、情報機器等の表示部に用いられ、輝度が高く表示特性の良好な表示装置が得られる液晶表示装置用基板及びそれを備えた液晶表示装置及びその製造方法を提供することを目的とする。

【解決手段】各画素は左右方向に延びるゲートバスライン25と、上下方向に延びるドレインバスライン26とで画定されている。各バスライン25、26の交差位置近傍にはTFTが形成され、その上部にTFTを遮光する樹脂重ね部32が形成されている。TFT基板8に対向して配置される共通電極基板上にはBMが形成されず、基板TFT基板8に形成された各バスライン25、26及び樹脂重ね部32がBMの機能を奏するようになっている。

(もっと読む)

薄膜トランジスタ、その製造方法、半導体装置および表示装置

【課題】オン電流が大きく、かつ電気的特性のばらつきが小さな薄膜トランジスタおよびその製造方法を提供する。

【解決手段】周辺TFT110のチャネル層141を形成するシリコンの結晶粒径は、微結晶シリコンによって形成されているので、閾値電圧のばらつきをある程度抑えながら、オン電流を大きくすることができる。しかし、多結晶シリコンからなるチャネル層を有する周辺TFTと比べて、小さなオン電流しか流すことができない。そこで、周辺TFT110のゲート電極125と対向する窒化シリコン膜180の表面に、さらにゲート電極195を形成する。この結果、チャネル層341を流れるオン電流は、2つのゲート電極125、195によって制御されるので、オン電流の不足分を補うことができる。

(もっと読む)

トランジスタの作製方法

【課題】酸化物半導体層を有するトランジスタにおいて、当該酸化物半導体層中の任意の領域に導電率が異なる領域を形成する方法を提供することを目的の一とする。

【解決手段】水素を有する酸化物半導体層上に水素バリア層を選択的に設け、酸化処理を行うことにより酸化物半導体層の所定の領域から選択的に水素を脱離させて、酸化物半導体層に導電率が異なる領域を形成する。その後、酸化物半導体層に形成された導電率が異なる領域を用いて、チャネル形成領域、ソース領域及びドレイン領域を形成することができる。

(もっと読む)

半導体装置

【課題】薄膜トランジスタにおいて、ソース/ドレイン領域へのコンタクトの方法を改良することにより、配線抵抗を減らす。

【解決手段】酸化珪素膜上の第1及び第2のシリサイド、チャネル形成領域、ソース領域及びドレイン領域を有する結晶性珪素膜と、チャネル形成領域上のゲイト絶縁膜と、ゲイト絶縁膜上のゲイト電極と、ゲイト電極の側面に設けられた側壁と、第1のシリサイドに接して設けられた第1の金属配線と、第2のシリサイドに接して設けられた第2の金属配線と、を有し、第1のシリサイドは、ソース領域の上面の一部及び側面に設けられ、第2のシリサイドは、ドレイン領域の上面の一部及び側面に設けられ、第1の金属配線と第2の金属配線は同一金属膜をエッチングして形成された構造であり、第1及び第2のシリサイドは、金属膜に用いられる金属を用いて形成されたシリサイドである。

(もっと読む)

電気光学装置用基板、電気光学装置用基板の製造方法、電気光学装置及び電子機器

【課題】電気光学装置用基板における意図しないエッチングに起因する影響を抑制し、電

気光学装置に好適な電気光学装置用基板を提供する。

【解決手段】電気光学装置用基板(200)は、基板(210)と、基板上に形成された

透光性を有する絶縁層(220)と、絶縁層上に配設された導電性パターン(230)と

を備える。該導電性パターンは、絶縁層上に所定の厚さに積層された第1金属層(232

)と、第1金属層の上層側に積層され、モリブデンを含んでなる第2金属層(231)と

を有し、第1金属層は、フッ素系ガスによりエッチングされる度合いが、フッ素系ガスに

より第1金属層がエッチングされる度合いに比べて小さく、且つ塩素系ガスによりエッチ

ングされる度合いが、塩素系ガスにより前記絶縁層がエッチングされる度合いに比べて大

きい金属を含んでなる。

(もっと読む)

表示装置

【課題】遮蔽膜とコモン線とを接続しないで良質な画像表示を行うことができるアクティブマトリクス型表示装置を提供する。

【解決手段】複数の画素TFTと、前記画素TFTに電気的に接続された画素電極と、遮蔽膜とが設けられた基板を有するアクティブマトリクス型液晶表示装置であって、遮蔽膜はフローティングになっており、画素電極と前記遮蔽膜との間に第1の誘電体を有し、遮蔽膜と前記コモン線との間に第2の誘電体を有する。

(もっと読む)

表示装置

【課題】動作特性に優れ低温で製造可能な酸化物半導体を用いた表示装置の特性を活かすには、適切な構成を備え、占有面積が小さい保護回路等が必要となる。

【解決手段】ゲート電極を被覆するゲート絶縁膜と、ゲート絶縁膜上においてゲート電極と重畳する第1酸化物半導体層と、第1酸化物半導体層のチャネル形成領域と重なる領域を覆うチャネル保護層と、第1酸化物半導体層上においてゲート電極と端部が重畳し、導電層と第2酸化物半導体層が積層された第1配線層及び第2配線層とを有する非線形素子を用いて保護回路を構成する。非線形素子のゲート電極を走査線又は信号線と接続し、ゲート電極の電位を印加するための非線形素子の第1配線層又は第2配線層とゲート電極の接続を直接接続することで、接続抵抗の低減による安定動作と接続部分の占有面積の縮小を図る。

(もっと読む)

液晶表示装置用薄膜トランジスタ基板及びその製造方法

【課題】TFT用薄膜トランジスタ基板の製造工程を単純化する。

【解決手段】絶縁基板と、その上に形成されており、ゲート線及びゲート電極を含むゲート配線と、前記ゲート線と平行な共通信号線及び前記共通信号線に連結され縦方向に伸びる共通電極を含む共通配線と、前記共通配線及び前記ゲート配線を覆うゲート絶縁膜と、一部は前記ゲート電極と重畳する半導体パターンと、前記半導体パターンの上部の縦方向に形成されて前記ゲート線と交差するデータ線と、前記データ線と連結されたソース電極と、前記ソース電極と分離された前記ゲート電極を中心にあり前記ソース電極と対向するドレーン電極とを含むデータ配線及び前記ドレーン電極と連結された画素電極を含む画素配線とを含み、少なくとも前記画素電極の下部に形成された前記半導体パターンは前記画素電極の外に出るように形成されている液晶表示装置用薄膜トランジスタ基板。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】金属材料からなるソース電極及びドレイン電極と、酸化物半導体膜とが直接接する薄膜トランジスタ構造とすると、コンタクト抵抗が高くなる恐れがある。コンタクト抵抗が高くなる原因は、ソース電極及びドレイン電極と、酸化物半導体膜との接触面でショットキー接合が形成されることが要因の一つである。

【解決手段】酸化物半導体膜とソース電極及びドレイン電極の間に1nm以上10nm以下のサイズの結晶粒を有し、チャネル形成領域となる酸化物半導体膜よりキャリア濃度が高い酸素欠乏酸化物半導体層を設ける。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】酸化物半導体層を有する薄膜トランジスタにおいて、水分などの不純物を混入させずに良好な界面特性を提供することを課題の一つとする。電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体装置を量産高く作製する方法を提案することを課題とする。

【解決手段】ゲート絶縁層表面に酸素ラジカル処理を行うことを要旨とする。よってゲート絶縁層と半導体層との界面に酸素濃度のピークを有し、かつゲート絶縁層の酸素濃度は濃度勾配を有し、その酸素濃度はゲート絶縁層と半導体層との界面に近づくにつれて増加する。

(もっと読む)

電界効果型トランジスタ、表示素子、画像表示装置及びシステム

【課題】高いキャリア移動度とノーマリーオフ特性とを有する電界効果型トランジスタを提供する。

【解決手段】ゲート電圧を印加するためのゲート電極26と、電流を取り出すためのソース電極23及びドレイン電極24と、ソース電極23及びドレイン電極24に隣接して設けられ、マグネシウム(Mg)とインジウム(In)を主成分とする酸化物半導体からなる活性層22と、ゲート電極26と活性層22との間に設けられたゲート絶縁層25とを備えている。そして、活性層22を形成する際に流す酸素ガスの流量は、酸素分圧が1.7×10−3Paとなるように調整されており、活性層22を構成する酸化物半導体は、体積抵抗率が10Ωcmで、酸素が非化学量論組成であるMgIn2O4系酸化物半導体となる。

(もっと読む)

半導体装置の作製方法

【課題】電気特性に優れ、信頼性の高い薄膜トランジスタを有する半導体装置を少ない工程で作製する方法を提供することを課題とする。

【解決手段】In、Ga、及びZnを含む酸化物半導体膜上にチャネル保護層を形成した後、n型の導電型を有する膜と、導電膜を成膜し、導電膜上にレジストマスクを形成する。このレジストマスクと共に、チャネル保護層及びゲート絶縁膜をエッチングストッパーとして利用して、導電膜と、n型の導電型を有する膜と、In、Ga、及びZnを含む酸化物半導体膜をエッチングして、ソース電極層及びドレイン電極層と、バッファ層と、半導体層を形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】インジウム(In)、ガリウム(Ga)、及び亜鉛(Zn)を含む酸化物半導体膜を用いる薄膜トランジスタにおいて、ソース電極またはドレイン電極のコンタクト抵抗を低減した薄膜トランジスタ及びその作製方法を提供することを課題の一つとする。

【解決手段】ソース電極層及びドレイン電極層とIGZO半導体層との間に、IGZO半導体層よりもキャリア濃度の高いバッファ層を意図的に設けることによってオーミック性のコンタクトを形成する。

(もっと読む)

配線、その製造方法、薄膜トランジスタおよび表示素子

【課題】良好な形状制御性を確保しつつ、銅配線層の酸化および銅の拡散を抑制できる配線を提供する。

【解決手段】金属拡散防止膜51上に形成したシード層52を、レジストを用いて選択的に除去する。レジストを除去した後、シード層52を覆って無電解めっき法により銅配線層53と、銅配線層53上に位置するメタルマスク層54とを形成する。メタルマスク層54を用いて金属拡散防止膜51を選択的に除去する。良好な形状制御性を確保しつつ、金属拡散防止膜51の形成時のエッチングなどによる銅配線層53の表面荒れなどを防止して、銅配線層53の酸化および銅の拡散を抑制できる。

(もっと読む)

81 - 100 / 144

[ Back to top ]