Fターム[2H092JA39]の内容

液晶−電極、アクティブマトリックス (131,435) | 能動素子 (19,865) | 三端子素子 (19,408) | 構造 (10,751) | ゲート電極 (2,011) | 厚さ (144)

Fターム[2H092JA39]に分類される特許

21 - 40 / 144

アクティブマトリックス基板及びアクティブマトリックス基板の製造方法、液晶表示装置

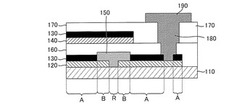

【課題】電極からの反射がなく、表示画像が悪化することがないアクティブマトリックス基板を提供する。

【解決手段】本発明のアクティブマトリクス基板は、基板110側と反対側に反射防止層130が形成された反射防止層130が形成された電極(図14のAに相当するソースドレイン電極層)と、基板110側と反対側に反射防止膜が形成されていない反射防止膜除去電極(図14のBに相当するソースドレイン電極層)と、基板110上に設けられた親液性領域Rと、反射防止膜除去電極とに接するように形成された半導体層150と、を有している。

(もっと読む)

半導体装置

【課題】カラーフィルタに含まれる不純物による汚染の問題を解決する。

【解決手段】薄膜トランジスタと、薄膜トランジスタに電気的に接続されるソース電極及

びドレイン電極と、薄膜トランジスタ、ソース電極及びドレイン電極上の第1の絶縁膜と

、第1の絶縁膜上のカラーフィルタと、カラーフィルタ上の第2の絶縁膜と、第2の絶縁

膜上の画素電極とを有し、第1の絶縁膜は窒化シリコンを有し、カラーフィルタは第1の

開口部を有し、第2の絶縁膜は第2の開口部を有し、第2の開口部は第1の開口部の内側

に設けられ、画素電極は、第1の開口部及び第2の開口部を介してソース電極及びドレイ

ン電極の一方に電気的に接続され、カラーフィルタは、画素電極、ソース電極及びドレイ

ン電極に接触しない。

(もっと読む)

半導体装置

【課題】金属酸化物中の酸素欠損を低減し、電気的特性の安定した半導体装置を提供することを目的の一とする。

【解決手段】ゲート電極と、ゲート電極上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられた第1の金属酸化物膜と、第1の金属酸化物膜に接して設けられたソース電極及びドレイン電極と、ソース電極及びドレイン電極上に設けられたパッシベーション膜と、を有し、パッシベーション膜は、第1の絶縁膜と、第2の金属酸化物膜と、第2の絶縁膜とが順に積層された半導体装置である。

(もっと読む)

電気光学装置の製造方法、電気光学装置、投射型表示装置および電子機器

【課題】絶縁膜の穴内に設けたプラグ電極によって導電層同士の導通を行うにあたって、研磨時間やプラグ電極形成用導電膜の成膜時間を短縮することのできる電気光学装置の製造方法、電気光学装置、投射型表示装置、および電子機器を提供すること。

【解決手段】液晶装置の素子基板において、第2電極層7aと画素電極9aとを層間絶縁膜48の穴48a内に設けたプラグ電極8aを介して電気的に接続するにあたって、第1絶縁膜46に設けたコンタクトホール46aを埋めるようにプラグ電極8aを形成した後、第2絶縁膜47を成膜する。そして、第2絶縁膜47を表面側から研磨してプラグ電極8aを露出させた後、第2絶縁膜47の表面側に画素電極9aを形成する。

(もっと読む)

薄膜トランジスタとその製造方法、および当該薄膜トランジスタを用いた画像表示装置

【課題】隔壁形成プロセスを省き、かつ、塗布法により半導体溶液を所望の場所に形成し、トランジスタ素子分離を行うことのできる薄膜トランジスタを提供する。

【解決手段】基板上に形成された梯子状の凸部を有するゲートバス電極と、ゲートバス電極の表面形状に沿うように当該ゲートバス電極上および基板上に形成されたゲート電極と、ゲート電極の凹凸に沿うようにゲート電極上および基板上に形成されたゲート絶縁体層と、ゲート絶縁体層の凹部内に形成された半導体層と、半導体層の中央に形成された保護膜と、半導体層の両端部で接続されたソース電極とドレイン電極とを備える。

(もっと読む)

表示装置

【課題】上部遮光膜を備えなくともチャネル形成領域を遮光することができる表示層装置。

【解決手段】チャネル形成領域上にシリコンを含むゲート絶縁膜103を有し、ゲート絶縁膜を介して、チャネル形成領域上にゲート電極104と、容量配線とを有し、その上にシリコンを含む第2絶縁膜106を有し、第2絶縁膜上に、Alを含む第2配線を有し、その上に酸化シリコンを有する第3絶縁膜を有し、第3絶縁膜上に、Alを含む第3配線を有する表示装置であって、第2配線及び第3配線はチャネル形成領域を遮光することができる。

(もっと読む)

電気光学装置の製造方法

【課題】遮光層の遮光性能を低下させずに、素子基板に対する加熱処理を行うことのできる電気光学装置の製造方法を提供すること。

【解決手段】液晶装置の製造工程において、素子基板用の基板本体10wの一方面10sに走査線3a(遮光層)、絶縁膜12を形成した後、半導体層1aを形成する半導体層形成工程、および半導体層1aに導入した不純物を拡散させる不純物拡散工程では、レーザーアニール装置やランプアニール装置等の加熱装置920によって、一方面10s側を他方面10t側より温度を高くした状態で加熱する。このため、走査線3aは高い温度に加熱されないので、走査線3aに用いたアルミニウム膜やタングステンシリサイド膜に溶融や再結晶化等が発生しない。

(もっと読む)

薄膜トランジスタの製造方法、薄膜トランジスタ、表示装置、センサ及びX線デジタル撮影装置

【課題】基板の選択性を広げつつ、電界効果移動度が高くノーマリーオフ駆動する薄膜トランジスタ等を得る。

【解決手段】活性層の成膜工程での成膜室中の雰囲気の全圧に対する酸素分圧をPo2depo(%)とし、熱処理工程中の雰囲気の全圧に対する酸素分圧をPo2anneal(%)としたときに、熱処理工程時の酸素分圧Po2anneal(%)が、−20/3Po2depo+40/3≦Po2anneal≦−800/43Po2depo+5900/43の関係を満たすように成膜工程と熱処理工程とを行う。

(もっと読む)

電気光学装置

【課題】電気光学装置の作製工程においてマスク枚数を追加することなく、反射電極の散

乱構造を作製する。

【解決手段】層間膜に感光性樹脂膜を用いる。フォトマスク100の第1の透光部101

を通して露光してパターニングしてコンタクトホール103〜106を得る。フォトマス

ク100の第2の透光部102を通して露光すると、感光性樹脂膜が解像不能となり、感

光性樹脂膜の表面に凹凸ができる。これにより一枚のフォトマスクでコンタクトホール形

成と層間膜表面に凹凸を有する散乱構造とができる。

(もっと読む)

薄膜トランジスタの半導体層用酸化物およびスパッタリングターゲット、並びに薄膜トランジスタ

【課題】Gaを含まないIn−Zn−Oの酸化物半導体を備えた薄膜トランジスタのスイッチング特性およびストレス耐性が良好であり、特に正バイアスストレス印加前後のしきい値電圧変化量が小さく安定性に優れた薄膜トランジスタ半導体層用酸化物を提供する。

【解決手段】Inと;Znと;Al、Si、Ta、Ti、La、Mg、およびNbよりなる群から選択される少なくとも一種の元素(X群元素)と、を含む薄膜トランジスタの半導体層用酸化物である。

(もっと読む)

EL表示装置

【課題】動作性能および信頼性の高いEL表示装置を提供する。

【解決手段】第1のチャネル形成領域と、第1のソース領域及び第1のドレイン領域と、ゲート絶縁膜と、第1のゲート電極とを備えた第1のTFTと、第2のチャネル形成領域と、第2のソース領域及び第2のドレイン領域と、ゲート絶縁膜と、第2のゲート電極とを備えた第2のTFTと、第1のTFT及び第2のTFT上に設けられた第1の絶縁膜と、第1のソース領域及び第1のドレイン領域の一方と接続されたソース配線と、第1のソース領域及び第1のドレイン領域の他方と接続し、且つ第2のゲート電極に接続された第1のドレイン配線と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の一方に接続された第2のドレイン配線と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の他方に接続された電流供給線と、を有する。

(もっと読む)

半導体装置、表示装置、電子機器

【課題】作製工程を増やすことなく、凹凸形状の画素電極を作製することを目的とする。

【解決手段】凸部は、フォトマスクを用いて作製すると再現性の高いものが得られるため、画素TFT1203の作製工程にしたがって作製すればよい。画素TFT1203の作製と同様に積層される半導体層、ゲート絶縁膜および導電膜を積層して凸部を形成する。こうして形成された凸部および同一工程で形成された画素TFT、駆動回路に含まれるTFTを覆うように層間絶縁膜を形成する。凹凸を有する層間絶縁膜が形成されたら、その上に画素電極を形成する。画素電極の表面も絶縁膜の凹凸の影響を受け表面が凹凸化する。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】

製造プロセスのステップ数を少なくでき、素子の構造が簡単でコストを抑制することが可能な薄膜トランジスタを提供する。

【解決手段】本発明の薄膜トランジスタ100は、主面を有する基材110と、前記基材110の前記主面に対する積層方向に配設される遮光層111と、前記積層方向からみて、前記遮光層111に含まれるように設けられる有機半導体層150と、前記有機半導体層150と接触するように設けられ、互いに対向しチャネル領域を形成するソース電極120及びドレイン電極130と、前記積層方向からみて、前記有機半導体層150の外周において前記ソース電極120と前記ドレイン電極130と重畳しない溝部165が設けられたゲート絶縁層160と、前記積層方向からみて前記有機半導体層150を含むように、前記ゲート絶縁層160上及び前記溝部165に設けられるゲート電極140と、からなることを特徴とする。

(もっと読む)

半導体装置

【課題】半導体装置の開口率を向上することを課題の一とする。

【解決手段】同一基板上に第1の薄膜トランジスタを有する画素部と第2の薄膜トランジ

スタを有する駆動回路を有し、画素部の薄膜トランジスタは、ゲート電極層、ゲート絶縁

層、膜厚の薄い領域を周縁に有する酸化物半導体層、酸化物半導体層の一部と接する酸化

物絶縁層、ソース電極層及びドレイン電極層、及び画素電極層とを有し、第1の薄膜トラ

ンジスタのゲート電極層、ゲート絶縁層、酸化物半導体層、ソース電極層、ドレイン電極

層、酸化物絶縁層、及び画素電極層は透光性を有し、駆動回路部の薄膜トランジスタのソ

ース電極層及びドレイン電極層は、保護絶縁層で覆われ、画素部のソース電極層及びドレ

イン電極層よりも低抵抗の導電材料である半導体装置を提供する。

(もっと読む)

配線構造

【課題】有機ELディスプレイや液晶ディスプレイなどの表示装置において、エッチストッパー層を設けなくてもウェットエッチング時の加工性に優れた配線構造を提供する。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、薄膜トランジスタの半導体層と、金属配線膜とを有しており、前記半導体層と前記金属配線膜との間にバリア層を有する配線構造であって、半導体層は酸化物半導体からなり、バリア層は、高融点金属系薄膜とSi薄膜の積層構造を有し、Si薄膜は半導体層と直接接続している。

(もっと読む)

液晶パネル、液晶表示装置、及びその製造方法

【課題】最上層に共通電極が形成された横電界方式の液晶パネルの製造工程において、露光の回数を低減する。

【解決手段】ゲート配線40は、画素電極70と同じ材料で形成され且つ画素電極70と同じ層に位置する下ゲート配線40aと、当該下ゲート配線40bに積層され、透明導電材料よりも導電率の高い材料で形成された上ゲート配線40bと、を含む2層構造を有している。

(もっと読む)

半導体装置、半導体装置の製造方法、電気装置

【課題】半導体装置、半導体装置の製造方法、電気装置を提供する。

【解決手段】本発明の半導体装置は、一面に、ソース電極41cおよびドレイン電極41dを有する第1基板34と、一面に、ゲート電極41e、ゲート絶縁膜41bおよび半導体層41aを有する第2基板39と、第1基板34および第2基板39が互いの一面側を対向させて貼り合わされることによりこれら第1基板34と第2基板39との間に構成される薄膜トランジスタTRと、を備えている。

(もっと読む)

半導体装置及びトランジスタの駆動方法

【課題】光照射されてトランジスタの電気特性が変動した場合でも、その電気特性をほぼ光照射前の状態にする手法を提供する。

【解決手段】酸化物半導体を用いたトランジスタのゲート電極に、正のバイアス電圧を10msec以上印加することにより、光照射されて変動した当該トランジスタの電気特性をほぼ光照射前の状態にすることが可能になる。なお、当該トランジスタのゲート電極に対する正のバイアス電圧印加は、当該トランジスタが受光する光量を参照して適切なタイミングで行う。これより光照射されても表示品位の低下が抑制された表示装置を実現することができる。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置に於けるLDD構造とGOLD構造の形成は、従来、ゲート電極をマスクにセルフアラインで形成しているが、ゲート電極が2層構造となる場合が多く、成膜工程とエッチング工程が複雑になる。またドライエッチング等のプロセスのみでLDD構造及びGOLD構造の形成を行っている為、トランジスタ構造が全て同一構造となり、回路毎にLDD構造とGOLD構造及びシングルドレイン構造を別々に形成することが困難である。

【解決手段】 回折格子パターン或いは半透膜から成る光強度低減機能を有する補助パターンを設置したフォトマスク或いはレチクルをゲート電極形成用フォトリソグラフィ工程に適用することにより、ドライエッチング及びイオン注入工程を通し、回路毎にGOLD構造及びLDD構造及びシングルドレイン構造のトランジスタを簡単に形成することができることを特徴としている。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】現在、良質な膜を得るために、下地膜から非晶質シリコン膜までの形成プロセスは、各々の成膜室にて行われている。これらの成膜条件をそのまま用いて同一成膜室にて下地膜から非晶質シリコン膜までを連続形成すると、結晶化工程で十分に結晶化されない。

【解決手段】水素希釈したシランガスを用いて非晶質シリコン膜を形成することにより、下地膜から非晶質シリコン膜までを同一成膜室内で連続形成しても、結晶化工程で十分に結晶化可能となる。

(もっと読む)

21 - 40 / 144

[ Back to top ]