Fターム[2H092MA02]の内容

液晶−電極、アクティブマトリックス (131,435) | 製造方法 (16,988) | 製法、工程 (14,676) | 成膜方法 (5,204)

Fターム[2H092MA02]の下位に属するFターム

Fターム[2H092MA02]に分類される特許

1 - 20 / 154

トランジスタ、表示装置および電子機器

【課題】良好な歩留りで製造可能なトランジスタ、表示装置および電子機器を提供する

【解決手段】ゲート電極と、絶縁層を間にして前記ゲート電極に対向する半導体層と、

前記半導体層に電気的に接続された一対のソース・ドレイン電極と、前記一対のソース・ドレイン電極それぞれと前記半導体層との間のキャリア移動経路に設けられ、その端面が前記ソース・ドレイン電極に覆われたコンタクト層と、を備えたトランジスタ。

(もっと読む)

反転印刷方法およびそれに使われる除去版、その製造方法

【課題】除去版のパターンサイズが小さい場合であっても、パターンの高解像性を維持することができる反転印刷方法およびそれに使われる除去版、その製造方法を提供する。

【解決手段】版材の厚さ方向の一方に位置する表面に凸部15と凹部12とからなるパターンを形成した除去版6を用意する。ブランケット3上に塗布されたインキ材料に除去版6を押し当てることにより凸部15の頂面16に対応するインキ材料をブランケット3から除去することでブランケット3上に残存するインキ材料からなる凹部12に対応する形状のパターンインキを形成する。パターンインキを基材4に転写することによって基材4上に凹部12に対応する形状のパターンを形成する。除去版6は、凸部15の頂面16で凹部12の外周に位置する部分に凹部12の輪郭に沿って延在する溝状の凹型補正線13が連続してあるいは断続して形成されている。

(もっと読む)

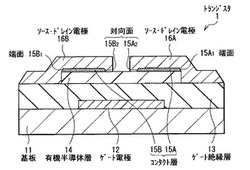

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】

製造プロセスのステップ数を少なくでき、素子の構造が簡単でコストを抑制することが可能な薄膜トランジスタを提供する。

【解決手段】本発明の薄膜トランジスタ100は、主面を有する基材110と、前記基材110の前記主面に対する積層方向に配設される遮光層111と、前記積層方向からみて、前記遮光層111に含まれるように設けられる有機半導体層150と、前記有機半導体層150と接触するように設けられ、互いに対向しチャネル領域を形成するソース電極120及びドレイン電極130と、前記積層方向からみて、前記有機半導体層150の外周において前記ソース電極120と前記ドレイン電極130と重畳しない溝部165が設けられたゲート絶縁層160と、前記積層方向からみて前記有機半導体層150を含むように、前記ゲート絶縁層160上及び前記溝部165に設けられるゲート電極140と、からなることを特徴とする。

(もっと読む)

FFSモード液晶表示装置及びその製造方法

【課題】 比較的簡単な工程で画素領域にコンタクトホールを形成せず、ダーク領域とディスクリネーションを最大限除去することによって、開口率を増加させることができるようにする。

【解決手段】 本発明による液晶表示装置は、画素領域内に透明画素電極と透明共通電極を備えて液晶を駆動し、透明共通電極は、複数のスリットを有し、単位画素が互いに連結されるようにスイッチング素子の少なくとも一部をオープンして形成され、スリットは、ゲートラインと5乃至10度の角度をもって形成され、液晶層のラビング方向は、ゲート方向と実質的に平行に構成される。本発明によれば、開口率の低下要因を除去し、光の漏れ現象を遮断し、内部反射をさらに向上させることができる。

(もっと読む)

半導体装置の作製方法

【課題】安定した電気特性を有するトランジスタを有する、信頼性のよい半導体装置を作製するための、半導体装置の作製方法を提供することを課題の一とする。

【解決手段】絶縁表面を有する基板上にゲート電極を形成し、ゲート電極上にゲート絶縁膜を形成し、ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜にマイクロ波または高周波の電磁波を照射し、電磁波が照射された酸化物半導体膜上にソース電極及びドレイン電極を形成し、ゲート絶縁膜、酸化物半導体膜、ソース電極、及びドレイン電極上に酸化物半導体膜の一部と接する酸化物絶縁膜を形成する半導体装置の作製方法。

(もっと読む)

液晶表示装置およびその製造方法

【課題】画像品質を向上し、小型化でき、工程を簡略化して製造歩留まりの向上や信頼性の向上する。

【解決手段】反射部11と光透過部12とが画素部に設けられている第1基板10と、第1基板10と間隔を隔てて対向している第2基板80と、第1基板10と第2基板80との間に配置されている液晶層19とを有する液晶表示装置において、第1基板10の光反射部11に対応する液晶層19側の領域に偏光層211を形成する。

(もっと読む)

半導体装置及びその作製方法

【課題】半導体膜に混入する不純物濃度を制御した活性層を有する半導体回路を備えた半

導体装置を提供するものである。

【解決手段】上記目的を解決するため、ガラス基板上に200nm〜500nmの膜厚の

第1の窒化珪素膜と、前記第1の窒化珪素膜上に第2の窒化珪素膜と、前記第2の窒化珪

素膜上にチャネル形成領域となる領域を含む非晶質半導体膜と、を有する構成において、

前記第1の絶縁膜と前記第2の絶縁膜との界面において、ボロンを有する。

(もっと読む)

電気光学装置の製造装置

【課題】サセプタの貫通孔内においてリフトピンを滑らかに昇降させることのできる構成を有する電気光学装置の製造装置を提供する。

【解決手段】チャンバー60と、チャンバー60内に設けられ、基板10’が載置されると共に、貫通孔63が設けられたサセプタ61と、貫通孔63内に挿通され、基板10’を昇降自在に支持するリフトピン62と、リフトピン62における下端62i側の外周面62gに形成された、貫通孔63の内周面63nに接触する接触部位62p1と、リフトピン62における上端62t側の外周面62gに貫通孔63の長さよりも短く形成された、貫通孔63の内周面63nに対し非接触となる非接触部位62p2と、リフトピン62の下端62iに当接した状態でリフトピン62を昇降させ、リフトピン62の上端62tに支持された基板10’を昇降させるリフトバー65と、を具備していることを特徴とする。

(もっと読む)

表示装置用基板およびそれを備えた液晶表示装置

【課題】配線の低抵抗化を実現することができ、かつ配線と導電層との密着性を向上させることができる表示装置用基板およびそれを備えた液晶表示装置を提供する。

【解決手段】絶縁性基板10、絶縁性基板10上に設けられた配線4、配線4における絶縁性基板10の反対側に設けられた導電層12、並びに、配線4および導電層12を覆うように絶縁性基板10上に設けられた層間絶縁膜15を備えており、導電層12が金属ナノ粒子を含有し、配線4における導電層12との接触面にはスリット21が形成されている。

(もっと読む)

配線基板の製造方法及び表示装置

【課題】工程数の増加を抑制しながら配線抵抗を低下させることができる配線基板の製造方法及び表示装置を提供する。

【解決手段】基板上に配線を備える配線基板の製造方法であって、上記製造方法は、上記基板上に上記配線を形成し、上記基板から上記配線を凸状に突出させる工程と、導電粒子を含むインクを吐出し、上記配線の上面の幅全体に連続して広がるインク滴を上記配線上に配置する工程と、上記インク滴を焼成し、上記配線上に導電層を形成する工程とを含む配線基板の製造方法である。

(もっと読む)

薄膜トランジスタ基板および表示装置

【課題】キャパシタの層間ショート欠陥を低減することが可能な薄膜トランジスタ基板およびこれを備えた表示装置を提供する。

【解決手段】キャパシタ30は、例えば、基板10上に、下層電極31、キャパシタ絶縁膜32および酸化物半導体よりなる上層電極33を順に有している。具体的には、上層電極33は、TFTの酸化物半導体層と同層に形成されたものである。上層電極33が薄く、ステップカバレージが悪いので、キャパシタ絶縁膜32中に異物が存在しても、下層電極31と上層電極33との間で層間ショートが発生しにくくなる。酸化物半導体はアモルファスシリコンに比べて導電性が高いので、櫛歯状などの複雑な形状にする必要はなく、上層電極33の全面をキャパシタ電極として機能させることが可能である。

(もっと読む)

配線、その製造方法、薄膜トランジスタおよび表示素子

【課題】良好な形状制御性を確保しつつ、銅配線層の酸化および銅の拡散を抑制できる配線を提供する。

【解決手段】金属拡散防止膜51上に形成したシード層52を、レジストを用いて選択的に除去する。レジストを除去した後、シード層52を覆って無電解めっき法により銅配線層53と、銅配線層53上に位置するメタルマスク層54とを形成する。メタルマスク層54を用いて金属拡散防止膜51を選択的に除去する。良好な形状制御性を確保しつつ、金属拡散防止膜51の形成時のエッチングなどによる銅配線層53の表面荒れなどを防止して、銅配線層53の酸化および銅の拡散を抑制できる。

(もっと読む)

インプリント用硬化性組成物、これを用いた硬化物およびその製造方法、並びに、液晶表示装置用部材

【課題】良好なインプリント性と光硬化性を有し、機械的特性や各種耐久性、中でも光硬化性、耐熱性および弾性回復率に優れたインプリント用硬化性組成物、これを用いた硬化物およびその製造方法、並びに、液晶表示装置用部材を提供する。

【解決手段】光重合性単量体と、光重合開始剤と、酸化防止剤と、含有する光インプリント用組成物であって前記光重合性単量体の含有量が80〜99質量%であり、前記酸化防止剤の含有量が0.3〜7.質量%であり、前記酸化防止剤が、ヒンダードフェノール系酸化防止剤のみ、セミヒンダードフェノール系酸化防止剤のみ、ヒンダードフェノール系酸化防止剤とセミヒンダードフェノール系酸化防止剤の混合物、またはヒンダードアミン系酸化防止剤のみ、のいずれかであることを特徴とするインプリント用硬化性組成物。

(もっと読む)

薄膜トランジスタおよびそれを用いた装置

【課題】薄膜トランジスタの構成部材の位置ずれを抑制し、さらに寄生容量の低減を図った薄膜トランジスタおよびそれを用いた装置の提供。

【解決手段】絶縁基板上に、ソース電極、ドレイン電極、前記ソース電極と前記ドレイン電極に電気的に接続される半導体層と、少なくとも前記半導体層上に形成されるゲート絶縁膜と、前記ゲート絶縁膜上に前記半導体層と重畳して配置されるゲート電極を備えるものであって、

前記ソース電極上に重ねられて第1バンク絶縁膜、前記ドレイン電極上に重ねられて第2バンク絶縁膜が形成され、

前記半導体層、ゲート絶縁膜、およびゲート電極は、前記第1バンク絶縁膜と前記第2バンク絶縁膜の間の領域に形成されている。

(もっと読む)

表示装置及びその製造方法

【課題】走査信号線と映像信号線との交差箇所に開口部を設け、半導体層及び導電体層をレジストリフロー方式により形成する場合に、例えば黒点化修正を行えるよう担保できる表示装置を提供する。

【解決手段】映像信号線DLとの交差箇所に開口部APが設けられた走査信号線GL、絶縁膜、導電体層より広がった領域を覆う半導体層AS、及び導電体層が順次積層され、導電体層は映像信号線DL、薄膜トランジスタTのドレイン電極DE及びソース電極SE、並びに映像信号線GLとドレイン電極DEとを接続する接続線LLを含み、接続線LLは開口部AP上で映像信号線DLから分岐し、開口部APは接続線LLと交差する方向の幅が半導体層ASの幅より広くなるように、走査信号線GLの両側端に向けて突出して形成されている表示装置である。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタアレイ及び画像表示装置

【課題】絶縁層の上部と下部との導電体の間の導通をバンプにより十分に確保することができる薄膜トランジスタ、薄膜トランジスタアレイ及び画像表示装置を提供する。

【解決方法】バンプと、バンプにより貫通される絶縁層とを含む薄膜トランジスタにおいて、バンプがフッ素化合物を含み、絶縁層が塗布法で形成され、バンプのフッ素含有量が、0.01wt%以上5wt%以下であり、バンプが凹版印刷法またはスクリーン印刷法で形成されていることを特徴とする薄膜トランジスタ。

(もっと読む)

アレイ基板及び画像表示装置

【課題】 ヒロック等の発生による障害が発生することがなく、十分な信頼性を確保することが可能なアレイ基板及び画像表示装置を提供する。

【解決手段】 第1配線層、第2配線層17、第3配線層19を有し、信号線が第2配線層17及び第3配線層19により構成されるとともに、最下層の第1配線層の一部が薄膜トランジスタのゲート電極15を構成している。外部接続用のOLBパッド4が最上層の第3配線層19の一部により形成されており、OLBパッド4と接続される引き出し配線が第2配線層17により形成されている。

(もっと読む)

多孔質銅焼結膜の製造方法、及び多孔質銅焼結膜

【課題】基材上に配置して乾燥後、250℃以下の比較的低温で焼成しても導電性に優れ、不純物の少ない導電部材を得ることが可能な分散性の高い銅微粒子分散水溶液を提供する。金属微粒子分散液を基板上に塗布して、加熱焼成方法により導電性の高い導電回路を形成する方法を提供する。

【解決手段】一次粒子の平均粒径が1〜500nmである銅微粒子が2〜70質量%の濃度となるように溶媒(S)に分散させた銅微粒子分散溶液(L)を基材(S)に塗布し、次に該銅微粒子分散溶液(L)が塗布された基材を160〜500℃に加熱された炉内に挿入して不活性ガス雰囲気中で急速加熱することにより銅微粒子を焼結して、空隙率が40〜70%である焼結膜を基材上に形成することを特徴とする、多孔質銅焼結膜の製造方法。多孔質銅焼結膜の1例である多孔質銅焼結膜を示す。

(もっと読む)

半導体装置及び電子機器

【課題】動作性能および信頼性の高い半導体装置を提供する。

【解決手段】第1の薄膜トランジスタと、第2の薄膜トランジスタとを有する画素部を有する。前記第1の薄膜トランジスタは、第1の半導体層と、前記第1の半導体層上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成された第1のゲート電極とを有し、前記第2の薄膜トランジスタは、第2の半導体層と、前記第2の半導体層上に形成された前記ゲート絶縁膜と、前記ゲート絶縁膜上に形成された第2のゲート電極とを有する。前記第1のゲート電極及び前記第2のゲート電極は、それぞれ端部にテーパー部を有し、前記第1の半導体層は、第1のチャネル形成領域、一対の第1の不純物領域、及び一対の第2の不純物領域を有し、前記第2の半導体層は、第2のチャネル形成領域、及び一対の第3の不純物領域を有する。

(もっと読む)

MEMSデバイスの製造方法

【課題】犠牲層を自己制御的に除去することができるMEMSデバイスの製造方法を提供する。

【解決手段】MEMSデバイス50の製造方法は、まず、第1シリコン酸化膜51上に、アルミ又はアルミ系合金からなる第1犠牲層52aを形成する。第1犠牲層52aは、ゲート電極の形成と同時に形成する。次に、第1犠牲層52a上に、ITOからなる第2犠牲層52bを形成する。第2犠牲層52bは、画素電極の形成と同時に形成する。このような犠牲層52上に、錘58として機能する第2シリコン酸化膜53、シリコン膜54を形成し、所定の形状にパターンニングする。その後、電食反応を利用して、犠牲層52に王水を接触させることにより、自己制御的に犠牲層52を除去し、錘58の下側に空洞を形成する。

(もっと読む)

1 - 20 / 154

[ Back to top ]