Fターム[2H092MA05]の内容

液晶−電極、アクティブマトリックス (131,435) | 製造方法 (16,988) | 製法、工程 (14,676) | 成膜方法 (5,204) | PVD (2,371) | スパッタ法 (1,712)

Fターム[2H092MA05]に分類される特許

1,661 - 1,680 / 1,712

半導体装置及びその作製方法、並びにテレビジョン

【課題】本発明は、しきい値のずれが生じにくく、高速動作が可能な逆スタガ型のTFTを有する半導体装置の作製方法を提供する。また、少ない原料でコスト削減が可能であり、且つ歩留まりが高い半導体装置の作製方法を提供する。

【解決手段】 本発明は、耐熱性の高い材料でゲート電極を形成した後、非晶質半導体膜を成膜し、該非晶質半導体膜に触媒元素を添加し加熱して結晶性半導体膜を形成し、該結晶性半導体膜上にドナー型元素又は希ガス元素を有する層を形成し加熱して触媒元素を結晶性半導体膜から除いた後、該結晶性半導体膜の一部を用いて半導体領域を形成し、該半導体領域に電気的に接するソース電極及びドレイン電極を形成し、ゲート電極に接続するゲート配線を形成して、逆スタガ型のTFTを形成して半導体装置を作製する。

(もっと読む)

表示装置および表示装置の検査方法

【課題】 表示装置の小型化が可能で、かつ表示不良などの検査を行うことができる表示装置を提供する。

【解決手段】 配線群が形成された絶縁性基板1と、前記絶縁性基板の端部近傍に形成され、前記絶縁性基板1の表示領域の配線群と接続される駆動電極出力用配線が形成された面上で、前記配線群に信号を供給する駆動回路3のバンプと接続される電極端子とを備えた表示装置であって、前記絶縁性基板1上に形成された駆動回路出力用電極端子7は、前記駆動回路3が実装された領域以外まで延在して形成されていることを特徴とする。

(もっと読む)

電気光学装置および電子機器

【課題】 工程数を増大させることなく、遮光性の優れた遮光層を形成可能な電気光学装置、この電気光学装置を備えた電子機器、および電気光学装置の製造方法を提供すること。

【解決手段】 電気光学装置において、異なる色に対応する画素5の境界領域において、遮光層29は、下地層22の溝状の凹部220の内部に形成された反射層23の一部230と、異なる色に対応する反射表示用カラーフィルタ層251R、251G、251Bのうちの2つの重なり部分250とから構成されている。また、同一の色に対応する画素5同士の境界領域において、遮光層29は、下地層22の溝状の凹部220の内部に形成された反射層23の一部230と、3色の反射表示用カラーフィルタ層251R、251G、251Bの重なり部分とから構成されている。

(もっと読む)

薄膜トランジスタ表示板及びその製造方法

【課題】薄膜トランジスタ表示板の製造工程の簡素化、及び画素の開口率を低減しないストレージキャパシタの形成。

【解決手段】基板上にゲート電極を有するゲート線と維持電極線を形成し、それら線上にゲート絶縁膜を形成する。ゲート絶縁膜上に半導体層を形成し、その上にオーミック接触部材を形成する。オーミック接触部材上にソース電極を有するデータ線及びドレイン電極を形成し、それらの上に保護膜を蒸着する。保護膜上に第1感光膜を形成し、それをマスクとして保護膜をエッチングし、データ線の一部とゲート絶縁膜の第1部分を露出させる。第1感光膜を変化させ第2感光膜を形成し、それをマスクとして保護膜をエッチングし、ゲート絶縁膜の第2部分とドレイン電極の少なくとも一部を露出させ、且つゲート絶縁膜の第1部分を除去してゲート線の一部を露出させる。導電体膜を蒸着する。第2感光膜を除去してドレイン電極と接続される画素電極を形成する。

(もっと読む)

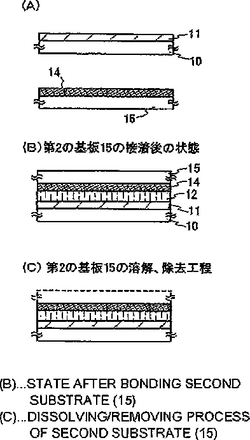

アクティブマトリクス基板およびそれを備えた表示装置

【課題】配線抵抗の増加やスイッチング素子の駆動能力の低下を伴うことなく、走査配線と信号配線との交差部に形成される容量を低減することが可能なアクティブマトリクス基板およびそれを備えた表示装置を提供する。

【解決手段】本発明によるアクティブマトリクス基板は、基板10と、基板10上に形成された信号配線11と、信号配線11に交差する走査配線13と、走査配線13に印加される信号に応答して動作するボトムゲート型の薄膜トランジスタ14と、薄膜トランジスタ14を介して信号配線11に電気的に接続され得る画素電極15とを備えている。信号配線11は、第1の層間絶縁膜12を介して走査配線13の下層に形成されており、第1の層間絶縁膜12に形成されたコンタクトホール12’を介して薄膜トランジスタ14のソース電極14Sに電気的に接続されている。

(もっと読む)

フラットパネルディスプレイ用Ag基合金配線電極膜およびAg基合金スパッタリングターゲット、並びにフラットパネルディスプレイ

【課題】 優れた電気伝導性を示すと共に、大気中で繰り返し高温加熱処理が施された場合であっても、優れた耐凝集性を示すフラットパネルディスプレイ用Ag基合金配線電極膜を提供する。

【解決手段】 フラットパネルディスプレイ用の配線電極膜であって、Biを0.01〜1.5at%含有し(Cu、Au及びPdよりなる群から選択される1種以上を合計で0.1〜1.5at%含んでいてもよい)、残部実質的にAgからなることを特徴とするフラットパネルディスプレイ用Ag基合金配線電極膜。

(もっと読む)

薄膜トランジスタパネル及びその製造方法

【課題】 アモルファスシリコン薄膜トランジスタとポリシリコン薄膜トランジスタとを備えた薄膜トランジスタパネルにおいて、より一層の小型化を図る。

【解決手段】 アモルファスシリコンからなる半導体薄膜41を有する光電気変換型の薄膜トランジスタ3は、ポリシリコンからなる半導体薄膜25、26を有する駆動回路用のCMOS薄膜トランジスタ21、22よりも上層側に設けられている。これにより、半導体薄膜41を半導体薄膜25、26と同一の層上に設ける場合と比較して、より一層の小型化を図ることができる。この場合、薄膜トランジスタ3のボトムゲート電極9、ソース・ドレイン電極10及びトップゲート電極8と薄膜トランジスタ21、22のソース・ドレイン電極を含む導電体層35、36とを接続する接続配線の一部である上層接続配線48、51、54は、トップゲート電極8が設けられたトップゲート絶縁膜39上に設けられている。

(もっと読む)

薄膜トランジスタパネル及びその製造方法

【課題】 アモルファスシリコン薄膜トランジスタとポリシリコン薄膜トランジスタとを備えた薄膜トランジスタパネルにおいて、より一層の小型化を図る。

【解決手段】 アモルファスシリコンからなる半導体薄膜42を有する光電気変換型の薄膜トランジスタ3は、ポリシリコンからなる半導体薄膜25、26を有する駆動回路用のCMOS薄膜トランジスタ21、22よりも上層側に設けられている。これにより、半導体薄膜42を半導体薄膜25、26と同一の層上に設ける場合と比較して、より一層の小型化を図ることができる。この場合、薄膜トランジスタ3のボトムゲート電極9、ソース・ドレイン電極10及びトップゲート電極8と薄膜トランジスタ21、22のソース・ドレイン電極に接続される導電体層35、36とを接続するための上層接続配線49、52、55、58は、トップゲート電極8を覆う層間絶縁膜40上に設けられている。

(もっと読む)

半導体装置および半導体装置の作製方法

(課題)様々な基材に被剥離層を貼りつけ、軽量された半導体装置およびその作製方法を提供することを課題とする。

(解決方法)本発明は、基板上に被剥離層を形成し、この被剥離層にエッチングストッパー膜が設けられた封止基板を接着材で貼り合わせ、その後、封止基板のみをエッチングまたは研磨によって除去する。残ったエッチングストッパー膜は、そのままブロッキング膜として機能させる。また、貼り付ける部材としてマグネットシートを貼り付けてもよい。  (もっと読む)

(もっと読む)

電気光学装置、その製造方法および電子機器

【課題】 良好な素子特性を維持しながら、補助容量線の抵抗に起因した表示品位の低下を抑制する。

【解決手段】 本発明の電気光学装置は、互いに交差する方向に延在する走査線21及びデータ線13と、データ線13に一端が接続された二端子型非線形素子であって、第1導電層141と、絶縁層145と、第1導電層141よりも抵抗率が低い材料からなる第2導電層131,142とを積層してなる二端子型非線形素子14と、二端子型非線形素子14の他端に接続され、走査線21に電気光学物質を挟んで対向する画素電極16と、第2導電層131,142と同一の材料からなり、走査線21と交差する補助容量線17と、補助容量線17に接続された第1電極181と画素電極16に接続された第2電極182とが相互に対向してなる補助容量18とを備えている。

(もっと読む)

液晶用マトリクス基板およびその製造方法

【課題】 表示品位が高く、周辺回路とのコンタクト性に優れた液晶表示装置を構成するマトリックス基板およびその製造方法を実現する。

【解決手段】 複数の液晶セルを形成するためのマトリクス回路が形成されている液晶用マトリクス基板において、液晶パネルを組み立てるときに貼り合わせ面となる表面に島状に、第1の導電材からなる絵素電極12と、第2の導電材からなる端子電極13とを形成する。このとき、第1の導電材は、第2の導電材よりも透過性が高く、かつ、導電性が低いものを使用する。

(もっと読む)

半導体装置および半導体装置の作製方法

(課題)

本発明は、被剥離層に損傷を与えない剥離方法を提供し、小さな面積を有する被剥離層の剥離だけでなく、大きな面積を有する被剥離層を全面に渡って歩留まりよく剥離することを可能とすることを目的としている。また、本発明は、様々な基材に被剥離層を貼りつけ、軽量された半導体装置およびその作製方法を提供することを課題とする。特に、フレキシブルなフィルムにTFTを代表とする様々な素子(薄膜ダイオード、シリコンのPIN接合からなる光電変換素子やシリコン抵抗素子)を貼りつけ、軽量された半導体装置およびその作製方法を提供することを課題とする。

(解決方法)

基板上に金属層11を設け、さらに前記金属層11に接して酸化物層12を設け、さらに被剥離層13を形成し、前記金属層11をレーザー光で照射することで酸化を行い金属酸化物層16を形成させれば、物理的手段で金属酸化物層12の層内または金属酸化物層16と酸化物層12との界面において、きれいに分離することができる。  (もっと読む)

(もっと読む)

液晶ディスプレイ

【課題】 ピクセル口径比(開口率)を増大し、静電容量性クロストークを減少させたTFTアレイ、およびそのTFTアレイを有するアクティブ・マトリックス方式の液晶ディスプレイ、および製造方法を提供すること。

【解決手段】 複数のコンタクト・バイアス35あるいは開口部を有するフォトイメージ形成型絶縁層をアドレス線5、7とピクセル電極3間に設け、両者を重複可能とする。この絶縁層により静電容量性クロストークを減少し、かつピクセル開口率を増加させる。望ましい一実施例では、クロストークを減少するために絶縁層の誘電率は約3.0未満である。

(もっと読む)

表示装置およびその製造方法

【課題】フリッカ、焼き付き、中間階調の表示不良などの不具合が発生することを防止し、画像品質を向上する。

【解決手段】複数の走査配線211における各行の走査配線211bが、複数の画素電極111のうち、当該行の走査配線211bの形成領域と異なる領域に形成された画素電極111bを選択して画素スイッチング素子112に走査信号を供給するように形成する。これにより、走査信号を供給する際に、走査配線211と画素電極111との間で発生する寄生容量を減少させる。

(もっと読む)

薄膜トランジスタ装置及びその製造方法

【課題】ゲート絶縁膜が薄い低電圧駆動TFTとゲート絶縁膜が厚い高電圧駆動TFTとを有する薄膜トランジスタ装置において、高電圧駆動TFTのゲート電極及びソース/ドレイン電極をAl合金等の低抵抗金属で形成することができ、且つ熱活性化処理により不純物の活性化を行うことができる薄膜トランジスタ装置及びその製造方法を提供する。

【解決手段】第1の絶縁膜117を形成し、第1の絶縁膜117の上にMo膜により低電圧駆動TFTのゲート電極118と高電圧駆動TFTのチャネルとなる領域を覆うマスク膜とを形成し、ゲート電極118及びマスク膜をマスクとし半導体膜115に不純物を注入し、高濃度不純物領域122,124を形成する。その後、例えば500℃、2時間の条件で熱処理して不純物を活性化する。次いで、マスク膜を除去し、第2の絶縁膜126を形成し、その上にAl合金により高電圧駆動TFTのゲート電極127を形成する。

(もっと読む)

電気光学装置及びその製造方法、並びに電子機器

【課題】高品位な表示画像を得る。

【解決手段】加熱温度220℃、保持時間30分の条件下にて、アモルファス系の画素電極の場合はアニ−ル処理Cを実行して画素電極10の抵抗を小さくする。次に、その他の構成要素を取り付けて素子基板を作製すると共にカラーフィルタ基板91を作製してそれらを貼り合せる等して電気光学装置100を製造する。これにより、コンタクト抵抗は500KΩ以下の大きさになり、横スジムラ、画素ムラ等の生じない高品位な表示画像が得られる。

(もっと読む)

酸化インジウムスズ膜の製造方法

【課題】 熱安定および低電気抵抗の酸化インジウムスズ膜の製造方法を提供する。

【解決手段】 酸化物誘電層20を形成し、即ち、基板10の表面に酸化物薄膜を形成するステップaと、酸化物誘電層20を表面処理し、即ち、酸素をイオン源設備に送入し、酸素がイオン源を通過した後に発生するイオン束により酸化物誘電層20に表面処理を実行するステップbと、透明導電膜を形成し、即ち、イオン処理を通過した後の酸化物誘電層20の上に酸化インジウムスズ膜30を積層するステップcとを含む。基板10は、プラスチックの本体11と本体11の一側面に形成される硬質コーティング12から構成され、本体11の他側は基板10の表面10aを形成する。酸化物誘電層20にイオン処理を予め実行することで、酸化物誘電層20の安定性および精密度を高める。

(もっと読む)

半導体装置

【課題】ゲッタリングの効率を上げ、熱処理時間を短縮させた半導体装置の提供。

【解決手段】多結晶質半導体層におけるリッジに重金属等の不純物元素が偏析することが分かった。このリッジを積極的に利用し、ゲッタリングサイト1220,1221を形成することにより近接ゲッタリングを行う。さらにイオンドーピングを用いたゲッタリングサイトと併用することで、TFTのチャネル形成領域および、PN接合における空乏層領域から重金属等の不純物元素を取り除くことができ、ゲッタリング能力、ゲッタリング効率を高めることができる。

(もっと読む)

アクティブマトリクス装置及びその製造方法

【課題】 表示品質の悪化や製造効率の低下を防止することが可能なアクティブマトリクス装置を提供する。

【解決手段】 複数の画素部がマトリクス状に配置されたアクティブマトリクス装置であって、少なくとも一つの画素部は、不良箇所を有する第1の回路部と、第1の回路部上に積層され、第1の回路部の少なくとも不良箇所を置き換える第2の回路部と、第1の回路部と第2の回路部との間に設けられた接着層126とを備える。

(もっと読む)

半導体装置

【課題】特性の優れた薄膜トランジスタ(TFT)およびTFTを有する半導体集積回路を提供する。

【解決手段】周辺回路およびアクティブマトリクス回路を含む半導体装置において、前記周辺回路および前記アクティブマトリクス回路は、第1の絶縁膜を介して半導体層の下に設けられた第1のゲイト電極および第2の絶縁膜を介して前記半導体層の上に設けられた第2のゲイト電極を含む複数の薄膜トランジスタを含み、前記周辺回路の薄膜トランジスタの半導体層に結晶性半導体が用いられ、前記アクティブマトリクス回路の半導体層に非晶質半導体が用いられたことを特徴とする。

(もっと読む)

1,661 - 1,680 / 1,712

[ Back to top ]