Fターム[2H092NA21]の内容

液晶−電極、アクティブマトリックス (131,435) | 目的 (17,448) | 素子性能の向上 (1,705)

Fターム[2H092NA21]の下位に属するFターム

ON/OFF比の向上 (571)

寄生容量の低減 (220)

素子性能の均一化 (379)

Fターム[2H092NA21]に分類される特許

21 - 40 / 535

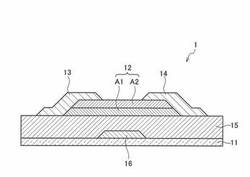

薄膜トランジスタ及びその製造方法、表示装置、イメージセンサー、X線センサー並びにX線デジタル撮影装置

【課題】400℃以下で作製可能であり、30cm2/Vs以上の高い電界効果移動度と、ノーマリーオフとなる低いオフ電流を両立する薄膜トランジスタを提供する。

【解決手段】ゲート電極16と、ゲート電極と接するゲート絶縁膜15と、In(x)Zn(1−x)O(y)(0.4≦x≦0.5,y>0)で表される第1の領域A1及びIn(a)Ga(b)Zn(c)O(d)(b/(a+b)>0.250,c>0,d>0)で表され、ゲート電極に対して第1の領域よりも遠くに位置する第2の領域A2を含み、ゲート絶縁膜を介してゲート電極に対向配置されている酸化物半導体層12と、互いに離間して配置されており、酸化物半導体層を介して導通可能なソース電極13及びドレイン電極14と、を有する薄膜トランジスタ1。

(もっと読む)

半導体素子の製造方法及び電界効果型トランジスタの製造方法

【課題】光照射時の素子特性を安定化する。

【解決手段】酸化物半導体を主体とする半導体膜を成膜する第一工程と、第一工程後に、半導体膜の面上に第一の絶縁膜を成膜する第二工程と、第二工程後に、酸化性雰囲気中で熱処理する第三工程と、第三工程後に、第一の絶縁膜の面上に第二の絶縁膜を成膜する第四工程と、を有し、第二工程と前記第三工程の際に、第一の絶縁膜の厚みをZ(nm)とし、第三工程での熱処理温度をT(℃)とし、前記第一の絶縁膜及び前記半導体膜中への酸素の拡散距離をL(nm)としたとき、0<Z<L=8×10−6×T3−0.0092×T2+3.6×T−468±0.1の関係式を満たすように第一の絶縁膜の厚みと熱処理温度を調整する。

(もっと読む)

液晶表示装置及びその製造方法

【課題】歩留まりの低下を抑制することが可能な液晶表示装置及びその製造方法を提供する。

【解決手段】スイッチング素子の上に配置されるとともに第1上面及び前記第1上面から前記スイッチング素子まで貫通した第1コンタクトホールを有する有機絶縁膜と、前記有機絶縁膜の前記第1上面に配置された上部電極及び前記上部電極と繋がり前記第1コンタクトホールに配置され前記スイッチング素子に電気的に接続された下部電極を有する島状の中継電極と、前記有機絶縁膜の前記第1上面に配置され前記中継電極から離間した共通電極と、前記中継電極及び前記共通電極の上に配置されるとともに前記中継電極の前記上部電極及び前記下部電極まで貫通した第2コンタクトホールを有する層間絶縁膜と、前記層間絶縁膜の前記第2コンタクトホールで前記中継電極に電気的に接続され前記共通電極と向かい合うスリットを有する画素電極と、を備えたことを特徴とする液晶表示装置。

(もっと読む)

半導体装置およびその作製方法

【課題】微細化に伴う短チャネル効果を抑制しつつ、トランジスタの電気特性のしきい値電圧(Vth)をプラスにすることができ、所謂ノーマリーオフを達成した半導体装置、及びその作製方法を提供する。また、ソース領域、及びドレイン領域と、チャネル形成領域との間のコンタクト抵抗を低くして良好なオーミックコンタクトがとれる半導体装置、及びその作製方法を提供する。

【解決手段】酸化物半導体層を有するトランジスタにおいて、少なくともチャネル形成領域となる、酸化物半導体層の一部をエッチングによって部分的に薄くし、そのエッチングによってチャネル形成領域の膜厚を調節する。また、酸化物半導体層の厚い領域に、リン(P)、またはホウ素(B)を含むドーパントを導入し、ソース領域、及びドレイン領域を酸化物半導体層中に形成することにより、ソース領域、及びドレイン領域と接続するチャネル形成領域とのコンタクト抵抗を低くする。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を含み、高速動作が可能なトランジスタ及びその作製方法を提供する。または、該トランジスタを含む信頼性の高い半導体装置及びその作製方法を提供する。

【解決手段】チャネル形成領域と、該チャネル形成領域を挟むように設けられ、チャネル形成領域よりも低抵抗な領域であるソース領域及びドレイン領域と、を含み、チャネル形成領域、ソース領域及びドレイン領域はそれぞれ結晶性領域を含む酸化物半導体層を有する半導体装置を提供する。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた整流特性の良い非線形素子(例えば、ダイオード)を提供

する。

【解決手段】水素濃度が5×1019/cm3以下である酸化物半導体を有する薄膜トラ

ンジスタにおいて、酸化物半導体に接するソース電極の仕事関数φmsと、酸化物半導体

に接するドレイン電極の仕事関数φmdと、酸化物半導体の電子親和力χが、φms≦χ

<φmdの関係になるように構成する。また、薄膜トランジスタのゲート電極とドレイン

電極を電気的に接続することで、さらに整流特性の良い非線形素子を実現することができ

る。

(もっと読む)

半導体装置の作製方法

【課題】高いオン特性を有する酸化物半導体を用いたトランジスタを提供する。高速応答及び高速駆動の可能なトランジスタを有する高性能の半導体装置を提供する。

【解決手段】チャネル形成領域を含む酸化物半導体膜を有するトランジスタの作製工程において、該酸化物半導体膜に、金属元素を含む膜と接した状態で加熱処理することにより導入された金属元素と、注入法により該金属元素を含む膜を通過して導入されたドーパントとを含む低抵抗領域を形成する。低抵抗領域はチャネル長方向においてチャネル形成領域を挟んで形成する。

(もっと読む)

半導体装置及び表示装置

【課題】より良い動作を実現する半導体装置を提供する。

【解決手段】第1のトランジスタと、第1のトランジスタのゲートに電気的に接続される

第2のトランジスタとを有し、第1のトランジスタの第1の端子は第1の配線に電気的に

接続され、第1のトランジスタの第2の端子は第2の配線に電気的に接続され、第1のト

ランジスタのゲートは第2のトランジスタの第1の端子又は第2の端子に電気的に接続さ

れることにより半導体装置が構成されるものである。上記において、第1乃至第2のトラ

ンジスタは、少なくともチャネル領域に酸化物半導体を有し、かつ、オフ電流が小さなも

のを用いることができる。

(もっと読む)

薄膜半導体装置と薄膜半導体装置を用いた表示装置

【課題】IGZO等の酸化物半導体膜からなる薄膜半導体装置において、無酸素雰囲気中で加熱しても酸素が酸化物半導体膜に拡散してTFT特性を発現する薄膜半導体装置を提供すること。

【解決手段】薄膜半導体装置は、ガラスの基板20、ゲート電極23G,ゲート絶縁膜21、ソース電極23S、ドレイン電極23D、IGZOの酸化物半導体膜24、二酸化マンガン(MnO2)の酸素放出絶縁膜25、保護膜22からなる。薄膜半導体装置は、蛍光表示装置等の薄膜形成時における加熱工程、焼成工程、封着工程において加熱すると、酸素が酸素放出絶縁膜25から放出されて酸化物半導体膜24に拡散してTFT特性を発現する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタにおいて、電気的特性の変動が小さく、信頼

性の高い半導体装置を作製することを課題とする。

【解決手段】チャネルを形成する酸化物半導体層に接する絶縁層に、シリコン過酸化ラジ

カルを含む絶縁層を用いる。絶縁層から酸素が放出されることにより、酸化物半導体層中

の酸素欠損及び絶縁層と酸化物半導体層の界面準位を低減することができ、電気的特性の

変動が小さく、信頼性の高い半導体装置を作製することができる。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタパネル、及びこれらを製造する方法

【課題】薄膜トランジスタ、薄膜トランジスタパネル、及びこれらを製造する方法に関する。

【解決手段】薄膜トランジスタは、ゲート電極、ゲート絶縁膜、上記ゲート絶縁膜上に形成された酸化物半導体層、及び上記酸化物半導体層上に相互に離隔して形成されたドレーン電極及びソース電極を含む。上記ドレーン電極は、上記酸化物半導体層上に形成された第1のドレーン副電極及び上記第1のドレーン副電極上に形成された第2のドレーン副電極を含む。上記ソース電極は、上記酸化物半導体層上に形成された第1のソース副電極及び上記第1のソース副電極上に形成された第2のソース副電極を含む。上記第1のドレーン副電極及び上記第1のソース副電極は、ガリウム亜鉛酸化物(GaZnO)を含み、上記第2のドレーン副電極及び上記第2のソース副電極は、金属原子を含む。

(もっと読む)

薄膜トランジスタおよびその製造方法、ならびに電子機器

【課題】ソース電極およびドレイン電極と有機半導体層とにおける電荷注入効率の向上と性能の確保とを両立させることが可能な薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタは、エッチングガスと反応可能な金属元素および半金属元素のうちの少なくとも一方を含む金属含有材料により形成された有機半導体層と、互いに離間されたソース電極およびドレイン電極と、有機半導体層とソース電極およびドレイン電極とが重なる領域において有機半導体層とソース電極およびドレイン電極との間に挿入され、エッチングガスと反応可能な金属元素および半金属元素のうちの少なくとも一方を含まない非金属含有材料により形成された有機導電層とを備える。

(もっと読む)

半導体装置

【課題】動作特性および信頼性の向上した、新規なマルチゲート構造のトランジスタを提

供することを課題とする。

【解決手段】2つ以上のゲート電極と、直列に接続した2つ以上のチャネル形成領域、ソ

ース領域、ドレイン領域、及び高濃度不純物領域を有する半導体層と、を有するマルチゲ

ート構造のトランジスタにおいて、ソース領域側に近接するチャネル形成領域のチャネル

長が、ドレイン領域側に近接するチャネル形成領域のチャネル長よりも大きくする。

(もっと読む)

スイッチング素子基板

【課題】本発明は、低比誘電率かつ高OD値を達成することが可能な樹脂製遮光部を有し、画素部の面積が大きく、かつ、液晶表示装置に用いた場合に、コンタクトホール内における画素電極の断線を好適に防止することが可能なスイッチング素子基板およびこれを用いた液晶表示装置を提供することを主目的とする。

【解決手段】基材と、上記基材上に形成されたスイッチング素子と、上記基材上に設けられた画素部と、上記スイッチング素子上に形成され、上記スイッチング素子に用いられる電極上にコンタクトホールを有する樹脂製遮光部と、上記コンタクトホールの側面および端部を覆うように形成され、絶縁性を有する断線防止層とを有し、上記コンタクトホールの縦断面形状が、垂直形状または逆テーパー形状であり、上記断線防止層が、上記断線防止層の形成部分の縦断面形状が順テーパー形状となるように形成されていることを特徴とするスイッチング素子基板を提供することにより、上記目的を達成する。

(もっと読む)

半導体装置の作製方法

【課題】オフ電流を低減した優れた特性を有する薄膜トランジスタを作製する。

【解決手段】少なくとも微結晶半導体領域及び非晶質半導体領域が積層する半導体膜を有する逆スタガ型の薄膜トランジスタにおいて、半導体膜上に導電膜及びエッチング保護膜を積層形成し、エッチング保護膜上にマスクを形成し、エッチング保護膜、導電膜及び非晶質半導体領域の一部をエッチングする第1のエッチング処理の後、マスクを除去する。次に、上記エッチングされたエッチング保護膜をマスクとして、露出した非晶質半導体領域及び微結晶半導体領域の一部をドライエッチングする第2のエッチング処理により、微結晶半導体領域の一部を露出させ、バックチャネル領域を形成する。

(もっと読む)

薄膜トランジスタ基板およびその製造方法

【課題】高い表示品位を有する表示装置用の薄膜トランジスタ基板およびこれらを生産効率よく実現することができる製造方法を提供する。

【解決手段】基板1上の複数の部分に配設された半導体膜2と、半導体膜2上に、該半導体膜2と接し互いに離間して配設されたソース電極およびドレイン電極4と、半導体膜2、ソース電極3およびドレイン電極4を覆うゲート絶縁膜6と、ゲート絶縁膜6を介して、ソース電極3およびドレイン電極4の間に跨るように配設された、ゲート電極7とを有した薄膜トランジスタ201と、半導体膜2上に、該半導体膜と接して配設された補助容量電極10と、下層に半導体膜2を有してソース電極から延在するソース配線31と、ゲート電極7から延在するゲート配線71と、ドレイン電極4に電気的に接続された画素電極9と、隣り合う画素の補助容量電極10どうしを電気的に接続する、補助容量電極接続配線12とを備えている。

(もっと読む)

半導体装置

【課題】酸化物半導体層を用いる薄膜トランジスタにおいて、酸化物半導体層と電気的に

接続するソース電極層またはドレイン電極層との接触抵抗の低減を図ることを課題の一と

する。

【解決手段】ソース電極層またはドレイン電極層を2層以上の積層構造とし、その積層の

うち、酸化物半導体層と接する一層を酸化物半導体層の仕事関数より小さい仕事関数を有

する金属又はそのような金属の合金とする。二層目以降のソース電極層またはドレイン電

極層の材料は、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素、または上述

した元素を成分とする合金か、上述した元素を組み合わせた合金等を用いる。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体膜を用いて薄膜トランジスタを形成することで、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少なくとも結晶化した領域を有する。

(もっと読む)

半導体装置、表示モジュール、及び電子機器

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成すること

で、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置

及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、

ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の

導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも結晶化した領域を有する。

(もっと読む)

アクティブマトリクス基板及びそれを備えた表示パネル

【課題】フォトマスクの枚数を増やすことなく、酸化物半導体の半導体層を用いたTFTの特性の低下を抑制することにある。

【解決手段】マトリクス状の複数の画素電極Pと、各画素電極Pに接続されたTFT5と、互いに平行に延びる複数のソース線15aとを備え、TFT5が、絶縁基板10上のゲート電極11aと、ゲート電極11aを覆うゲート絶縁膜12aと、ゲート絶縁膜12a上でゲート電極11aに重なる酸化物半導体層13aと、酸化物半導体層13aに接続されたソース電極17a及びドレイン電極17bとを備え、ソース電極17a及びドレイン電極17bと酸化物半導体層13aとの間には、酸化物半導体層13aを覆う保護絶縁膜14aが設けられ、各ソース線15aは、金属材料により形成され、ソース電極17a及びドレイン電極17bは、各画素電極Pと同一材料により形成されている。

(もっと読む)

21 - 40 / 535

[ Back to top ]